基于CPLD逆变器并联载波同步的分析与设计

2015-06-19白雪飞胡国文

白雪飞,胡国文

(盐城工学院电气工程学院,江苏盐城224000)

基于CPLD逆变器并联载波同步的分析与设计

白雪飞,胡国文

(盐城工学院电气工程学院,江苏盐城224000)

采用数字控制的多台逆变器并联时,由于各自载波不同步会形成高频环流,严重影响系统的稳定性和增加损耗。给出了一种基于CPLD实现载波同步的方法,结合DPLL技术能够使从机在一个开关周期里跟踪主机同步信号,克服了传统载波同步方法效率低、抗干扰性差等缺点。在两台50 kW逆变器并联实验平台上进行实验验证,结果表明该载波同步方法动态响应速度快、稳定性好。

逆变器并联;载波同步;DPLL;CPLD;稳定性

多模块并联实现大容量电源系统是当今电源技术的发展方向。多模块并联各模块功率开关管的电流应力降低,从根本上保证了可靠性[1]。对于逆变器并联,各模块输出电压幅值相等、频率一致、相位同步,并且尽可能减小模块内部的环流。

对于采用数字控制的多台逆变器,载波由内部PWM模块产生,由于上电时间等随机问题,会造成各逆变器载波不同步。逆变器并联时,载波不同步会引起高频环流,严重影响系统的稳定性和增加系统损耗[2]。目前,传统载波同步是通过DSP或通讯来实现[3],采用DSP实现是用主机同步信号直接触发从机PWM,由于同步信号一般为高频信号,所以该方法抗干扰性差;通讯方式会引入通讯延时,降低了控制的精度。本文基于CPLD给出一种新型载波同步方法,其内部嵌入了DPLL[4],提高了系统抗干扰性,且能够在一个开关周期使从机跟踪主机同步信号。此外,本文根据开关频率动态修改载波同步参数,增加载波同步的范围。

图1 逆变器并联载波同步原理图

1 载波同步原理分析

以3台逆变器并联系统为例,图1给出了载波同步原理图。

载波同步让从机跟踪主机发出的同步信号,使从机和主机的载波相位一致,从而消除载波不同步带来的高频环流,提高系统稳定性和减少系统损耗。图1中,#1号逆变器为主机,#2、#3号为从机。主机PWM计数器根据预先设置点每隔一个开关周期产生一个脉宽很窄的同步信号),其经过载波同步处理模块后,产生一个与)同频同相的信号),该信号被送至从机,并触发其DSP的PWM模块,获得与主机相位一致的三角载波。传统的载波同步技术是将直接送至从机,由于)具有高频和脉宽窄等特性,所以带来抗干扰性差、不易捕捉等问题。针对上述问题,本文给出的载波同步方法主要完成如下功能:内嵌DPLL环节,将)经过数字锁相环处理,提高系统抗干扰能力;放大)的脉宽,便于同步信号的捕捉;增加锁相故障,提高系统稳定性;动态修改同步参数,增加载波同步跟踪频率的范围。图2所示为本文给出的载波同步方法结构框图。图2中,为从机反馈的同步信号,其与脉宽放大后的信号构成故障判断模块的输入,在主从机无同步脉冲或主从机长时间不同步时,输出故障信号。

图2 本文载波同步方法结构框图

2 基于CPLD载波同性能分析

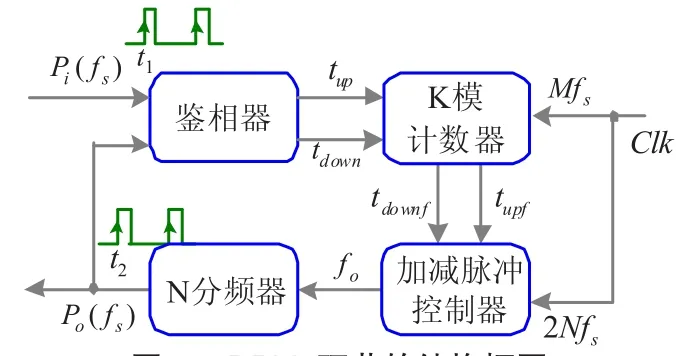

本文给出的载波同步方法关键部分为DPLL环节,图3给出其结构框图。

图3 DPLL环节的结构框图

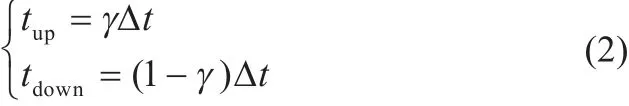

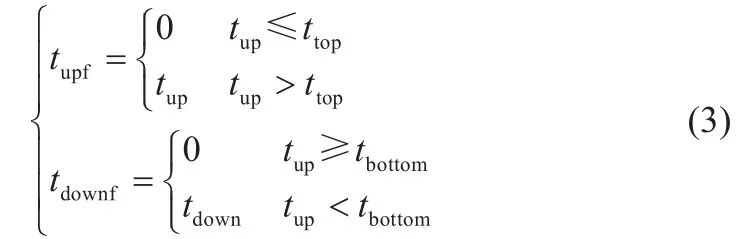

可以看出,DPLL由鉴相器、K模计数器、脉冲加减控制器和分频器组成。1、2对应和上升沿时刻,经鉴相器可获得其相位关系,并输出超前或滞后脉冲;K模计数器对其进行滤波处理,输出超前和滞后修正时间upf和downf,作为脉冲加减控制器的输入,对时钟脉冲进行扣除或添加处理,输出频率为的信号,经过分频后为。为系统时钟周期,分别为K模计数器和脉冲加减控制器提供时钟。令和相位差为△,则:

3 基于CPLD载波同步的设计

本文给出的逆变器并网系统采用DSP+CPLD控制,CPLD主要完成载波同步处理,图4给出了从机系统总体框图。

图4 从机系统总体框图

DSP选用F28335,CPLD采用Alter公司的EPM1270-T144C5。图4采用总线传输方式获取当前开关频率,并实时修正分频系数;载波同步模块输入为主机发送的同步信号和DSP EPWM模块反馈信号,输出信号直接送至EPWM同步输入端。根据前文的分析,鉴相器采用边沿方式实现,令MasterP和SlaveP分别标记主从机同步信号下降沿时刻,其值与相应操作如表1所示。

表1 MasterP和SlaveP值与相应操作的关系

K模计数器为双向可逆计数器,在相位超前或滞后时分别向上或向下计数,当计数值超过设定的top和bottom时,认为当前脉冲有效,模值K取值会影响跟踪速度和滤波效果,实际取16,对应时间为530 ns。为了简化设计,本文将脉冲加减计数器和分频器合并,其实现原理如表2所示。

表2 脉冲加减计数器实现原理

4 实验结果及分析

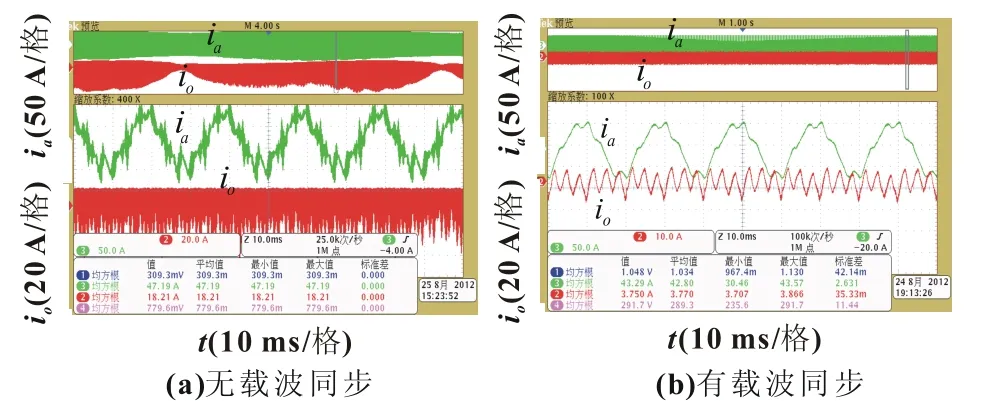

实验平台选择2台50 kW的三相逆变器,开关管为IGBT,滤波电感为0.3 mH,滤波电容为150μF,开关频率为8 kHz。图5所示为有/无载波同步时的环流波形。为环流,对比图5(a)和(b)可以看出,当采用载波同步时,环流中高频分量被有效地抑制。

图5有/无载波同步时环流波形

图6 给出了基于CPLD实现的载波同步波形。图中,()为主机发送的同步信号,()为载波同步模块输出的同步信号,通过测量,()和()上升沿间隔为298 ns,对于8 kHz开关频率,误差为0.24%。可见本文给出的载波同步方法能够使从机精确跟踪主机同步信号。感退出饱和,将电流钳在零位,使滞后桥臂实现零电流开关。仿真验证了所选ZVZCS电路能很好地体现其软开关特性,减少了电路中器件的开关损耗。

图6 载波同步实验波形

[1]殷文贵.移相全桥ZVS变换器研究[D].上海:上海交通大学,2012.

[2]胡红林,李春华,邵波.移相全桥零电压PWM软开关电路的研究[J].电力电子技术,2009,43(1):12-14.

[3]唐建山,林国庆.脉宽调制DC/DC全桥变换器软开关技术的研究[J].电工电气,2009,4:37-40.

[4]阮新波,严仰光.直流开关电源的软开关技术[M].北京:科学出版社,2000.

[5]李金鹏,尹华杰.ZVZCS移相全桥变换器的拓扑综述[J].电源世界,2004,7:1-5.

[6]朱艳萍.移相全桥ZVZCS DC/DC变换器综述[J].电源技术应用,2004,7(1):61-64.

[7]程琼,丁志林.基于PSpice的全桥移相控制芯片ucc3895的研究[J].电源技术应用,2013,16(1/2):22-25.

[8]余新颜,段善旭,康勇.零电压零电流移相全桥DC/DC变换器关键技术的研究[J].通信电源技术,2005,22(1):1-3.

5 结论

逆变器并联时,载波同步可以消除高频环流,提高系统的稳定性。常规载波同步方法具有效率低、抗干扰性差等缺点。本文基于CPLD给出一种新型载波同步方法,其内嵌了DPLL算法,通过分析和实验验证得出如下结论:

(1)增加了K模计数器,就有滤波的效果,提高系统抗干扰能力;

(2)能够在一个开关周期使从机跟踪主机的同步信号,动态响应快;

(3)具有动态修正同步参数的功能,增加了同步跟踪频率的范围;

(4)采用该方法可以明显减少逆变器并联时的高频环流。

参考文献:

[1]MAZUMDER S K,TAHIR M,ACHARYA K.Master-slave currentsharing control of a parallel DC/DC converter system over an RF communication interface[J].IEEE Trans Industrial Electronics, 2008,55(1):59-66.

[2]杨勇,阮毅,汤燕燕,等.风力发电系统中并网逆变器并联运行环流分析[J].高电压技术,2009,35(8):2012-2018.

[3]秦娟英,陕周荣.逆变器并联及DSP的应用[J].电气传动,2005, 35(6):29-31.

[4]何中一,王笑娜,刑岩.基于电力线通讯的逆变器并联系统同步控制方法[J].中国电机工程学报,2008,28(33):25-29.

Analysis and design of carrier synchronizer in parallel inverter based on CPLD

BAI Xue-fei,HU Guo-wen

High frequency circulation was generated in digitally controlled multiple inverter without carrier synchronization,resulting in serious impact on system stability and losses.A new type method of carrier synchronization was proposed based on CPLD,which overcame traditional method with shortcomings of low efficiency and poor anti-interference.This method which allowed slave tracking host synchronization signal in a switching cycle was combined with DPLL.Finally,two 50kW inverter parallel experiment platforms were build for verification.The result shows that this method has the advantage of fast dynamic response and good stability.

inverter parallel;carrier synchronization;DPLL;CPLD;system stability

TM 464

A

1002-087 X(2015)03-0581-02

2014-08-12

白雪飞(1981—),女,内蒙古自治区人,硕士,讲师,主要研究方向为电力电子技术应用。