HIRFL-CSR外靶实验读出电子学预研系统

2015-05-25康龙飞周家稳刘树彬

康龙飞,赵 雷,*,李 敏,周家稳,刘树彬,安 琪

(1.中国科学技术大学核探测与核电子学国家重点实验室,安徽合肥 230026;2.中国科学技术大学近代物理系,安徽合肥 230026)

HIRFL-CSR外靶实验读出电子学预研系统

康龙飞1,2,赵 雷1,2,*,李 敏1,2,周家稳1,2,刘树彬1,2,安 琪1,2

(1.中国科学技术大学核探测与核电子学国家重点实验室,安徽合肥 230026;2.中国科学技术大学近代物理系,安徽合肥 230026)

本文介绍了兰州重离子加速器冷却储存环(HIRFL-CSR)外靶实验读出电子学预研系统的设计。该系统可实现TOF墙探测器、中子墙探测器、多丝漂移室(MWDC)等的读出。基于前沿定时及使用TOT技术分别进行时间和电荷测量,从而对前沿定时带来的时间-幅度游走效应进行修正。该系统基于工业智能仪器总线PXI进行设计,提高了数据传输带宽,并保证了系统的可扩展性。目前已完成基本单元模块的实验室电子学测试,以及与探测器的初步联合测试,验证了各项功能指标。

兰州重离子加速器;外靶实验;时间测量;电荷测量;TOT;PXI

兰州重离子加速器冷却储存环(HIRFLCSR)[1-2]外靶实验用于研究核物理性质、放射性物理、超核等,探测器系统主要包括起始时间探测器、靶区γ探测器、大接收度二极磁铁中的多丝正比室(MWPC)、多丝漂移室(MWDC)、飞行时间(TOF)墙探测器和中子墙探测器。打靶后的反应产物经大接收度二极磁铁后,中性粒子不改变方向,带电粒子则偏向两边。通过测量粒子在各探测器中产生对应的电子学信号,可得到粒子的飞行时间、电荷等信息。

CSR外靶实验读出电子学预研系统旨在以较小通道规模实现完整系统的主要功能,为电子学系统进一步的完善和扩展做好准备。针对实验装置中的探测器类型,此预研系统包括1个时钟扇出模块、1个MWDC测量模块、1个TOF墙测量模块、两个中子墙测量模块和1个触发模块。高精度的时间和电荷测量是各测量模块要完成的主要功能,对于TOF墙和中子墙测量模块,要求在50~1 500mV的信号幅度内时间测量精度达25ps,电荷测量精度好于10%,而对于MWDC测量模块,要求精度达到百ps量级,同时实现高集成度设计。本文欲对HIRFL-CSR外靶实验读出电子学预研系统的设计进行介绍。

1 系统结构

图1 读出电子学预研系统基本结构示意图Fig.1 Block diagram of prototype readout electronics system

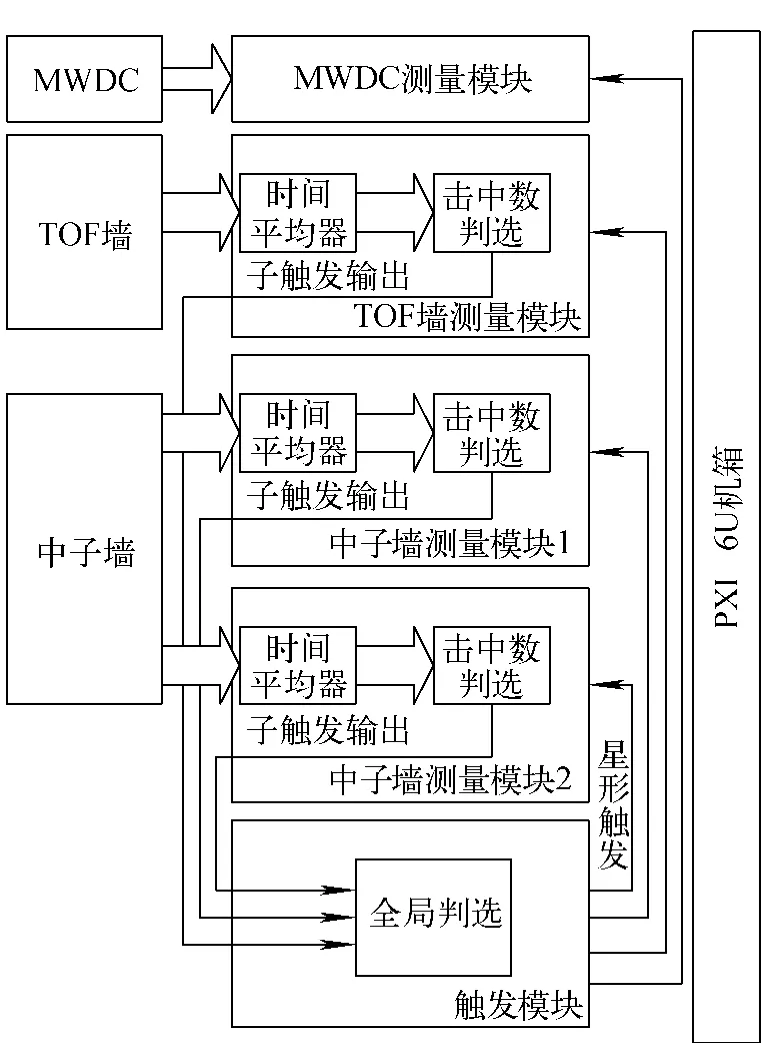

图1为读出电子学预研系统基本结构示意图,整个系统是基于PXI 6U[3]标准实现的。时钟扇出模块通过差分电缆向各模块提供高精度40MHz同步时钟;各测量模块对相应探测器输出信号进行测量,数据暂存于本模块缓存中;TOF墙测量模块和中子墙测量模块还要对输入信号进行判断产生子触发信号,并上行传输至触发模块;触发模块根据多路子触发信号进行逻辑处理产生总触发信号,并通过PXI背板上的星形触发总线扇出至各测量模块进行有效数据的读出。TOF墙和中子墙探测器由位于PXI机箱中的电子学模块进行读出,而MWDC的读出电子学则由紧邻探测器的SFE16前端模块和后端数字化模块(即图1中的MWDC测量模块)组成。

读出电子学预研系统设计难点包括:1)高精度时间与电荷测量电路;2)高集成度读出方法;3)基于多级判选的触发机制;4)基于PXI总线的高速数据传输;5)FPGA逻辑的在线更新。

1.1 高精度时间与电荷测量电路

TOF墙探测器和中子墙探测器均基于塑料闪烁体和光电倍增管(PMT)进行读出,两种探测器主要用于测量打靶反应中各种粒子的飞行时间。经过打靶后的束流粒子和打靶产生的各种次级粒子入射塑料闪烁体生成光子,通过位于塑料闪烁体两端的PMT进行光电转换并倍增,然后经同轴电缆传输至读出电子学。两种探测器输出信号的形状特征、测量指标基本一致,仅信号动态范围略有差别。因此,两种探测器的读出电子学基于同一种方案进行设计。

为进行高精度时间测量,本文采用前沿定时方法,同时对信号进行电荷测量,以对前沿定时带来的时间-幅度游走效应进行修正。为简化系统结构,本设计采用基于TOT技术[4-5]的高集成度专用ASIC芯片进行电荷测量。

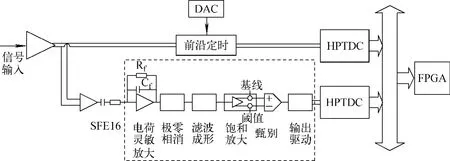

图2为高精度时间与电荷测量电路。输入信号放大后转换为差分模拟信号,然后基于差分模式进行处理以提高抗干扰能力,减少模拟电路偶次谐波所致的非线性失真,从而得到较高的测量精度。

差分信号分为两路,一路送入甄别器进行前沿定时,输出的LVDS信号送入HPTDC[6]进行时间数字变换,使用HPTDC的甚高精度模式,单芯片可提供8个精度达25ps的测量通道。另一路通过电压-电流变换后送入SFE16[7]芯片中,经过其内部的电荷灵敏放大、极零相消、滤波成形电路后进行饱和放大,然后使用甄别器得到输出脉宽与输入电荷量相关联的LVDS输出信号,再输入至HPTDC(高精度模式,100ps精度,每片集成32个通道),完成电荷测量。

基于上述技术完成时间和电荷测量模块(TCMM),每个模块集成16个通道。

1.2 高集成度读出方法

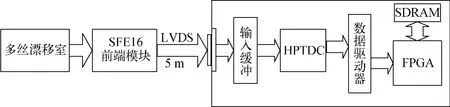

在外靶实验中,多丝漂移室的输出信号超过3 000通道,因此,需考虑进行高集成度电子学的设计。多丝漂移室电子学共分为两部分,分别为安插在探测器侧边的SFE16前端模块和位于PXI机箱中的MWDC测量模块(HDTDM)。图3为多丝漂移室读出电子学框图,前端模块(由中国科学院近代物理研究所设计)基于SFE16芯片将输出信号电荷转换为LVDS信号,其前沿含有时间信息,脉宽含有电荷信息,然后通过5m电缆传输送入HDTDM进行数字化。基于LVDS差分信号进行长距离传输,可减少传输中的信号失真和衰减。

图2 高精度时间与电荷测量电路Fig.2 Circuit of high precision time and charge measurement

在HDTDM中,为提升电子学集成度,并考虑到百ps的测量精度需求,在单个模块上使用4片工作在高精度模式下的HPTDC进行时间数字变换,共可提供128个100ps的测量通道。为实现高密度信号连接,输入接口选用超高密度连接器(VHDCI 743370051,Molex公司)。为了提供模块的数据缓存能力,在FPGA外部设计1片SDRAM,以确保数据的完整性。

1.3 基于多级判选的触发机制

为实现有效事例的筛选,剔除噪声等干扰,需进行触发判选电子学的设计以构成完整系统。在预研系统中,触发系统采用多级判选的结构,由触发模块和分布在各测量模块中的初级判选单元构成。上述3种探测器中,中子墙探测器和TOF墙探测器参与触发信号产生,而MWDC不参与。触发系统的结构如图4所示。

图3 多丝漂移室读出电子学框图Fig.3 Block diagram of MWDC readout electronics

触发判选共分3个步骤进行。前两个步骤对应初级判选,由各测量模块FPGA中的判选单元完成。探测器输出信号经甄别后得到通道击中信号,并输入FPGA中进行处理。第1步将来自同一根塑料闪烁体两端PMT的信号用时间平均器[8]处理;第2步使用状态机来统计在一段时间内测量模块中的击中通道数,当达到预设阈值时将产生子触发信号;各测量模块产生的子触发信号进一步传输至触发模块,进行第3步的全局触发判选。考虑到实验中对于多种可能触发判选算法的需求,此触发电子学基于可重构触发判选结构进行设计,整个触发算法基于可编程器件的逻辑设计完成,并在算法设计中使用系列的可重配置寄存器单元保证触发判选算法的灵活性。此外,通过FPGA逻辑在线更新技术,也可实现未来实验中对触发判选逻辑结构上的更改。

图4 触发系统结构Fig.4 Architecture of trigger system

经过全局判选的信号从PXI机箱的背板星形触发线扇出至各测量模块,以进行数据读出。星形触发总线是PXI协议扩展的点对点总线,触发信号通过此总线扇出,可减少在传输过程中各信号间的延时差异。

1.4 基于PXI总线的高速数据传输

在外靶实验中,由于数据通道较多,数据率较高,且各探测器各通道的数据率亦不一致,这就要求数据获取系统要有较高的数据传输率。PXI总线继承了PCI的电气信号,具有极高的数据传输能力,在33MHz时钟、32bit位宽的情况下理论传输速率可达132MB/s。同时,PXI采用和Compact PCI同样的机械外型结构,具备高密度、坚固外壳及高性能连接器的特性。

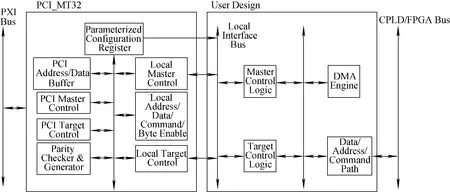

在预研系统中,采用可编程逻辑器件CPLD实现PXI接口设计,在完成基本接口通讯的同时,还可实现远程更新模块FPGA逻辑的功能,增加了系统的灵活性。在接口设计中,使用了Altera公司提供的PCI_MT32[9]作为接口函数(图5)。User Design是根据需求进行设计的用户接口逻辑。其中,Target Control Logic控制从模式下的读写操作,Master Control Logic与DMA Engine共同完成主模式下的突发写传输操作。为提高数据传输率,数据传输基于主模式下的突发传输方式。

图5 PXI接口框图Fig.5 Block diagram of PXI interface

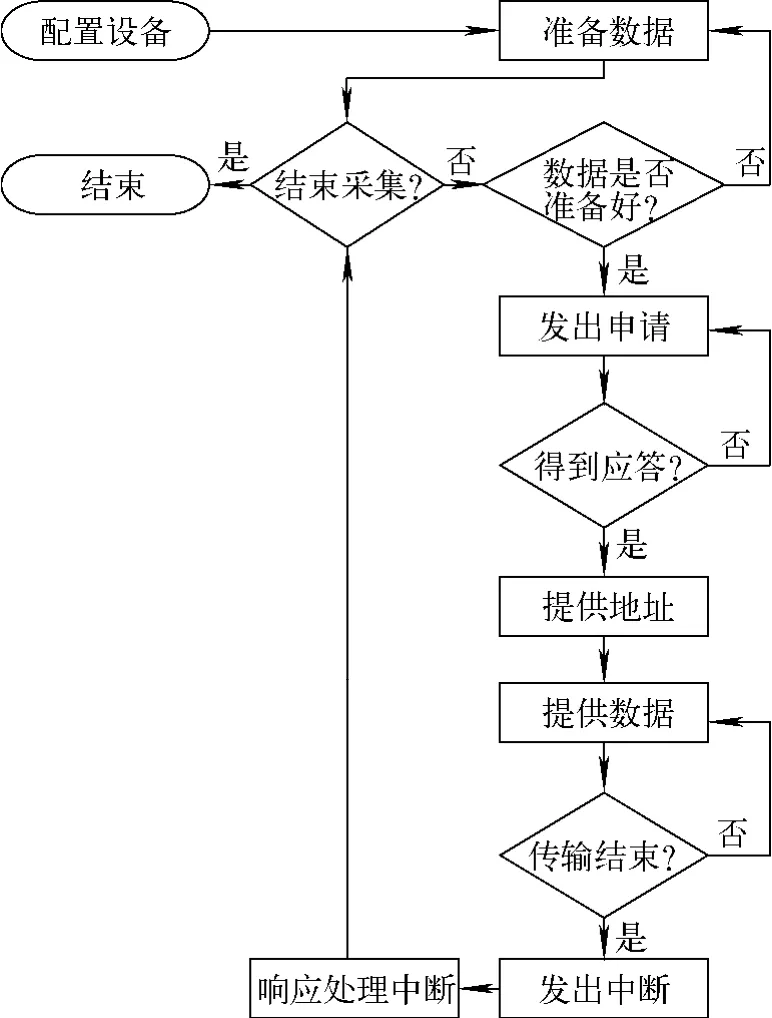

图6为数据读出的流程。当系统初始化时,上位机通过数据获取软件对测量模块(以下称设备)进行寄存器配置,包括各种DMA寄存器、突发长度寄存器等,并申请中断内存空间、注册中断函数。当某设备缓存数据量达到一定程度时,接口Local端(即图5中的User Design)向PCI_MT32发出申请,然后PCI_MT32向总线仲裁器发出总线占有申请;总线仲裁器根据总线当前状态进行仲裁,如果空闲,向设备发出应答信号。设备得到应答后,Local端向PCI_MT32提供1个时钟周期地址,接着提供数据,即数据传输开始;在提供数据的同时对传输数据个数进行统计,当达到预定个数即突发长度后,设备发出中断信号。中断控制器收到中断后,通知CPU;CPU对此中断作出响应并处理,包括清中断、拷贝数据并保存等操作。

图6 数据读出流程Fig.6 Flow diagram of data readout

不同突发长度对应不同数据传输率,在一定范围内随突发长度的增大,数据传输率增大。实际测试表明:在控制器不进行硬盘写入操作的情况下,突发长度为40kB时传输带宽值可达110MB/s;进行硬盘写操作情况下,突发长度为4kB时,数据传输带宽超过40MB/s[10]。可见,硬盘的写入速度限制了数据带宽,单独对硬盘进行写入操作时速度约为60MB/s。若将硬盘换成固态硬盘,数据传输带宽能得到提升。此外,CPU响应中断在一定程度上也降低了数据传输速率。

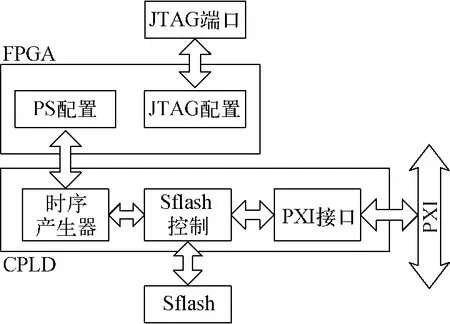

1.5 FPGA逻辑的在线更新

如前所述,外靶实验的规模较大,FPGA逻辑的在线更新功能为各模块逻辑的升级提供了便利,同时提高了触发判选的可重构性。图7为FPGA的配置,此系统模块中的FPGA设计了两种配置方式,即JTAG模式和PS模式,调试时使用JTAG模式,正常情况下使用PS模式。

图7 FPGA的配置Fig.7 Configuration of FPGA

通过PXI接口,将FPGA配置数据写到Sflash中。每次上电时,CPLD从Sflash中读取配置数据,并通过一定的时序将数据送至FPGA完成FPGA的PS配置。当FPGA需更新逻辑时,擦除Sflash原有数据并将新的配置数据写入,再次配置FPGA。

2 系统测试

系统测试包括实验室电子学性能测试及与探测器系统的初步联合测试。

2.1 实验室电子学性能测试

实验室电子学性能测试由任意波形发生器(AFG3252)作为信号源模拟真实信号,输入到各测量模块进行一系列测试。

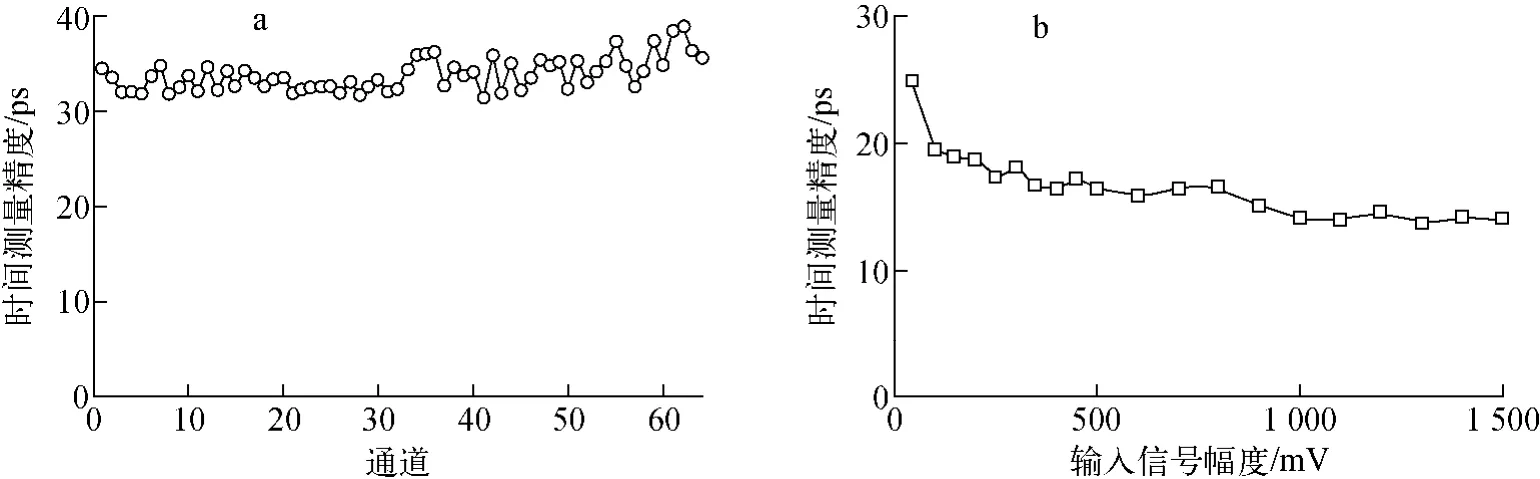

1)时间性能测试

图8示出了HDTDM和TCMM时间精度测试结果。对于HDTDM,将128通道分为64对,对每对进行时间差测试,时间测量精度均好于40ps;对于TCMM,在输入信号幅度50~1 500mV范围内,时间测量精度均好于25ps。

2)电荷性能测试

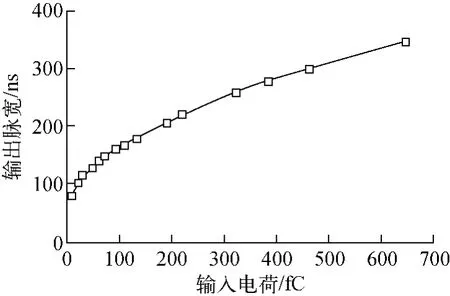

在不同输入信号幅度下,测量SFE16输出信号的脉宽及其抖动RMS值。根据脉宽与幅度的关系,可拟合出脉宽与幅度的斜率曲线。抖动RMS与拟合脉宽的比值,即为电荷测量精度。

图9示出了HDTDM和TCMM电荷性能测试结果,测得的电荷测量精度好于5%,满足10%的设计需求。可看出,随输入信号幅度的增大,电荷测量精度先变差后变好。这是因为电荷测量是由基于TOT技术的SFE16芯片完成的,在进行甄别得到输出脉宽前,有一级放大处理,当输入幅度达到一定值时,放大器将饱和,在饱和前的较小幅度输入下,脉宽与幅度拟合出的斜率基本一致,而在此饱和临界区域,斜率将会急剧减小,之后随着输入幅度的增加,斜率将会基本保持一致。

2.2 与探测器联合测试

图8 HDTDM(a)和TCMM(b)时间测量精度测试结果Fig.8 Time resolution test results of HDTDM(a)and TCMM(b)

图9 HDTDM(a)和TCMM(b)电荷测量精度测试结果Fig.9 Charge resolution test results of HDTDM(a)and TCMM(b)

电子学性能得到验证后,将读出电子学各模块与探测器系统进行了联合测试。

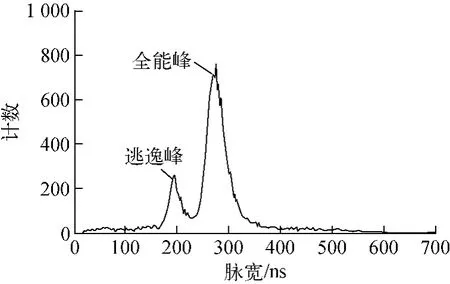

1)MWDC测量模块与多丝漂移室联合测试

使用55Fe作为多丝漂移室的放射源。55Fe衰变过程中产生的γ光子,在入射至多丝漂移室中通过与Ar原子反应会得到两种能量分布峰,55Fe X射线源5.9keV的全能峰和Ar的3keV逃逸峰。测试得到的结果如图10、11所示,全能峰和逃逸峰对应的脉宽分别为270ns、195ns,相应的输入电荷量为390fC、200fC,符合两峰之间能量的比例关系。

2)TCMM与探测器联合测试

将60Co作为放射源,使用塑闪小晶体和TOF墙塑闪单元条探测60Co在衰变过程中产生的1对级联γ光子。60Co放射源被放置在塑闪小晶体和TOF墙塑闪单元条之间,当60Co原子发生衰变时,连续产生两个γ光子,光子的发射方向是随机的,当两个光子一个向上穿过塑闪小晶体,另一个经过TOF墙塑闪单元条时,被视为一次有效事例。

图10 脉宽分布直方图Fig.10 Histogram of pulse width distribution

图11 输出脉宽与输入电荷对应关系曲线Fig.11 Curve of output pulse width with input charge

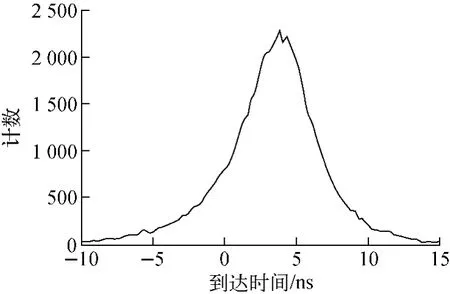

将塑闪小晶体作为事例发生的起始时间探测器,用TOF墙塑闪单元条一端的信号时间减去塑闪小晶体的信号时间,获得这端信号的到达时间(图12)。TOF墙塑闪单元条及其两端PMT的型号分别为BC408、R7525,两端PMT到达时间差小于25ns。由于入射粒子在塑闪单元条的入射位置是随机的,且光子从塑闪单元条的一端传播到另一端的时间为25ns,所以到达时间差的分布在25ns之内;测试时,由于未将塑闪小晶体精确定位在塑闪单元条的中间,造成了分布的不对称。

图12 TOF墙输出信号到达时间分布Fig.12 Histogram of arrival time for output signal of TOF wall

3)宇宙线联合测试

为进一步验证系统,将TOF墙和中子墙探测器与预研系统进行宇宙线联合测试。搭建测试平台(图13),使用两个塑闪小晶体进行定位,当宇宙线同时穿过这两个塑闪小晶体时被视为1次有效事例。中子墙测量模块和TOF墙测量模块分别对两种闪烁体输出信号进行测量。

图13 宇宙线测试示意图Fig.13 Block diagram of cosmic ray test

将塑闪小晶体1作为起始时间探测器,中子墙探测器一端PMT输出信号到达时间分布如图14所示,可看出,到达时间在5~15ns之间,大部分集中在7~10ns。

3 总结

本文针对HIRFL-CSR外靶实验主要探测器完成了读出电子学预研系统的设计,该预研系统包括128通道100ps的高精度时间测量模块、16通道25ps的高精度时间及电荷测量模块、时钟扇出模块和触发模块。目前已完成实验室电子学性能测试,并与探测器进行了初步联合测试,验证了系统性能指标,为电子学系统进一步的完善和扩展做好了准备。

[1] ZHENG Chuan,XIAO Zhigang,XU Hushan,et al.Hadron physics programs at HIRFL-CSRm:Plan and status[J].High Energy Physics and Nuclear Physics,2007,31(12):1 177-1 180.

[2] XIA J W,ZHAN W L,WEI B W,et al.The heavy ion cooler-storage-ring project(HIRFLCSR)at Lanzhou[J].Nuclear Instruments and Methods in Physics Research A,2002,488(1-2):11-25.

[3] PXI hardware specification revision 2.2[EB/OL].[2004-09-22].http:∥www.pxisa.org/userfiles/files/Specifications/PXIHWSPEC22.pdf.

[4] MANFREDI P F,LEONA A,MANDELLI E,et al.Noise limits in a front-end system based on time-over-threshold signal processing[J].Nuclear Instruments and Methods in Physics Research A,2000,439(2-3):361-367.

[5] LIU Xuzong,LIU Shubin,AN Qi.A time-overthreshold technique for PMT signals processing[J].Nuclear Science and Techniques,2007,18(3):164-171.

[6] 刘树彬,郭建华,张艳丽,等.高精度数据驱动型TDC在高能物理实验中应用的研究[J].核技术,2006,29(1):72-76.

LIU Shubin,GUO Jianhua,ZHANG Yanli,et al.The test of data driven TDC application in high energy physics experiment[J].Nuclear Techniques,2006,29(1):72-76(in Chinese).

[7] DELAGNES E,ABBON P,BEDFER Y,et al.SFE16,a low noise front-end integrated circuit dedicated to the read-out of large micromegas detector[J].IEEE Transactions on Nuclear Science,2000,47(4):1 447-1 453.

[8] DZAHINI D,POUXE J,ROSSETTO O,et al.Design and performance of a compensated meantimer[J].IEEE Transactions on Nuclear Science,2000,47(3):839-843.

[9] PCI compiler user guide[EB/OL].[2005-02-06].http:∥www.altera.com/literature/ug/ug_pci.pdf.

[10]KANG Longfei,ZHAO Lei,ZHOU Jiawen,et al.A 128-channel high precision time measurement module[J].Metrology and Measurement System,2013,20(2):275-286.

Prototype Readout Electronics System of External Experiment in HIRFL-CSR

KANG Long-fei1,2,ZHAO Lei1,2,*,LI Min1,2,ZHOU Jia-wen1,2,LIU Shu-bin1,2,AN Qi1,2

(1.State Key Laboratory of Particle Detection and Electronics,University of Science and Technology of China,Hefei 230026,China;2.Department of Modern Physics,University of Science and Technology of China,Hefei 230026,China)

A prototype of the readout electronics system was designed for the external experiment in HIRFL-CSR.This system is responsible for the readout of the TOF wall detector,the neutron wall detector and the MWDC.The time measurement was based on leading edge discrimination,while the TOT method was employed in charge measurement,and this made the time-walk to be corrected.The electronics was designed based on the PXI standard in order to guarantee that this system has a high data transfer rate and a good flexibility.The laboratory tests and preliminary commissioning tests with the detectors were conducted,which indicate the system functions are good.

HIRFL;external experiment;time measurement;charge measurement;TOT;PXI

TL594

:A

:1000-6931(2015)01-0154-08

10.7538/yzk.2015.49.01.0154

2013-10-10;

2014-02-28

国家自然科学基金资助项目(11079003);中国科学院知识创新工程重要方向性项目资助(KJCX2-YW-N27)

康龙飞(1985—),男,四川内江人,博士研究生,物理电子学专业

*通信作者:赵 雷,E-mail:zlei@ustc.edu.cn