高分辨率大面阵微型相机设计

2015-05-10陶淑苹郑晓云朴永杰

陶淑苹,郑晓云,朴永杰

(中国科学院 长春光学精密机械与物理研究所 小卫星技术国家地方联合工程研究中心,吉林 长春 130033)

1 引 言

微型飞行器或微小卫星为地球观测、临近空间目标监视、开发测试商业货架产品等应用研究提供了有效的低成本解决办法[1-2],因此开发支持这些基本或其他高级应用的小型化相机成为必需。目前,一些微小卫星已经采用小相机来获取图像,如德国亚琛应用科学大学于2008年发射的COMPASS-1即采用了OV7648FB相机模组,用于对地凝视拍照[1]。其中相机分辨率为640×480,像元尺寸5.6μm,输出支持 YUV/YCbCr 4∶2∶2ITU-656和RAW RGB,相机电子学系统高度集成,其供电、驱动和数据输出均通过FPC连接器与底端控制系统相连,功耗40mW,整星重量只有1kg。由于受微型飞行器或微小卫星重量、体积和成本等的限制,其携带的成像系统也必须具备集成度高、体积小、成本低特点。因此相较于CCD传感器在集成度、成像控制、功耗、成本方面具有明显优势的CMOS传感器更利于小型化相机设计。另外,将A/D转换集成于芯片内部的CMOS传感器输出为数字信号,避免了CCD传感器输出高频模拟信号在传输中易受噪声干扰的缺陷[3-7]。随着CMOS制造工艺的不断成熟,CMOS传感器应用于微型飞行器或微小卫星成为极可能趋势。

然而,人们对相机分辨率和幅宽等的要求越来越高,这对成像系统的设计也提出了更高的要求。为了满足高分辨率、小型化需求,本文设计了一种基于CMOS传感器OV14825的大面阵小型成像系统。

2 分辨率及幅宽分析

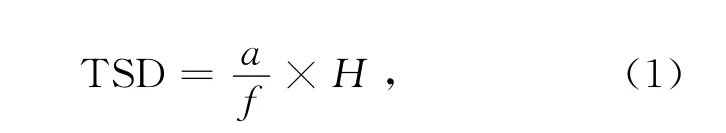

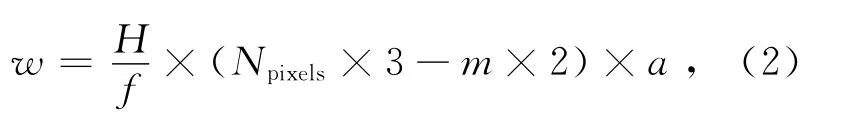

根据一次成像关系,如图1所示,结合成像距离、光学系统的焦距和所选用的传感器像元大小,可以由式(1)计算得到成像系统的目标像元分辨率TSD。

式中:a为CMOS传感器的像元尺寸,f为光学系统焦距,H为成像距离。在光学相机的方案设计阶段则可依据目标像元分辨率要求,反推得到光学系统焦距。

图1 一次成像示意图Fig.1 Schematic diagram of first imaging

所选传感器像元尺寸a=1.4μm,选取H=20km,f=50mm,计算得到地面像元分辨率可达到0.56m。

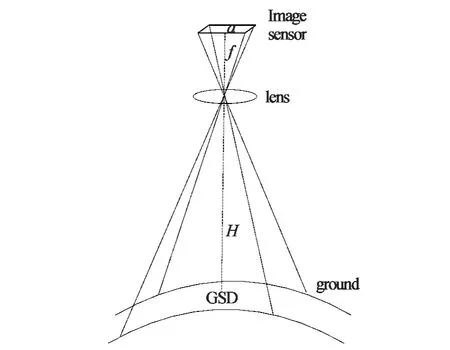

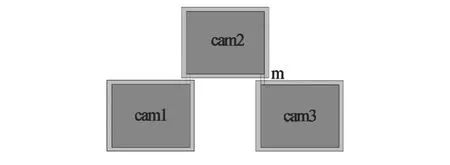

设计中采用3片传感器交错拼接方式(如图2所示),将焦面组成一个大面阵,因此该系统在保证高分辨率的同时又兼顾了大幅宽。成像幅宽计算公式如下:

式中,Npixels为传感器每行像元数,且对于本文所选传感器Npixels=4 416;m为两相邻传感器的搭接像元,此处选用m=20,由此计算得到大面阵相机幅宽为7.396km。

图2 传感器拼接示意图Fig.2 Schematic diagram of sensor splicing

为了获得最终图像还需要对3个传感器分别获取的图像进行拼接。如果对星下点成像则水平方向直接将搭接像元去除,垂直方向按照第2片传感器与1、3片传感器的位置几何关系和相对运动速度得到以时间和行数为变量的拼接算法,将对应于同一水平线上目标景物的不同传感器不同时刻不同行输出图像拼接。当侧摆成像时,还需要在上述操作之前增加几何校正,从而去除成像角度引起的缩放比不同的影响。

3 电子学系统方案

设计的大面阵CMOS成像系统电子学结构框图如图3所示,主要包括控制采集部分和成像部分。控制采集部分由图像快视系统、控制指令终端等组成,成像部分由FPGA、CMOS传感器、时序驱动电路、数据存储电路、数传电路等组成。实验选用了OmniVision公司的OV14825彩色面阵CMOS传感器,FPGA为Xilinx公司的XC4VFX60,另外采用了2片片外SRAM用于数字信号存储。其中3片彩色面阵CMOS传感器拼接组成一个大面阵焦平面。

图3 硬件系统结构框图Fig.3 Block diagram of the hardware system

控制指令终端通过RS422接口向FPGA发送控制指令,FPGA收到控制指令后译码,完成对CMOS内部寄存器的设置,同时相机有关的关键参数也可以返回上位机控制终端。CMOS传感器的驱动时序由FPGA生成,彩色面阵CMOS传感器初始化成功后会输出串行差分图像,图像进入FPGA首先进行串并转换,然后将信号转换为满足Camera Link接口时序的串行数据。另外FPGA控制2片SRAM实现数字图像的存储,最终数字图像以Camera Link接口形式发送至快视系统。

3.1 OV14825及其工作原理

OV14825是OmniVision公司生产的一款高性能彩色CMOS传感器。分辨率为4 416×3 312,像元尺寸1.4μm,其数字输出图像接口支持12bit并行DVP、MIPI或LVDS格式,数据格式为RAW RGB。串行相机控制总线SCCB接口用于实现对传感器驱动及成像参数有关寄存器的设置。

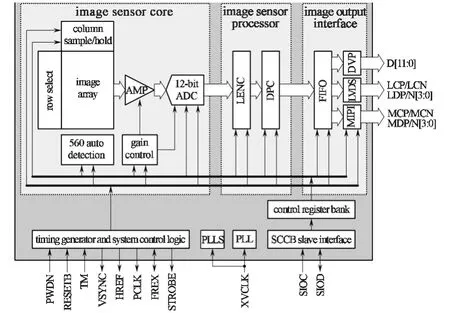

OV14825的结构框图如图4所示,包含图像传感器核、图像传感器处理器、图像输出接口、时序发生器、SCCB接口及控制寄存器,锁相环PLL。其中图像传感器核内部集成一个12bit的ADC模块,并可以实现外界光频率自动检测和增益调整;图像传感器处理器用于完成一些数字图像处理功能;图像输出接口支持DVP、MIPI或LVDS,可根据实际应用需求选择合适的接口方式。

图4 OV14825组成结构框图Fig.4 Structure diagram of OV14825

3.2 串行差分数据接收与发送

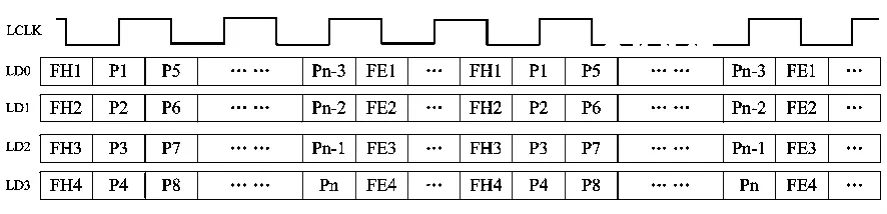

为了提高传输速率,本文选用LVDS数据接口方式进行系统设计。共有4对差分数据信号和1对差分时钟信号,当采用4通道数据输出时,其工作时序如图5所示。图中LCLK为像素时钟,LD0为第1个串行差分数据通道,LD3为第4个串行差分数据通道,单个数据通道内部为串行数据,多个数据通道之间形成并行发送,FH为4个帧头标识,FE为4个帧尾标识。

图5 LVDS图像工作时序图Fig.5 Timing diagram of the LVDS images

传感器LVDS图像数据直接进入FPGA,由于图像快视系统的采集卡为CAMERA LINK接口,因此FPGA除了完成图像数据的接收缓存外,还需完成CAMERA LINK接口数据的转发控制。

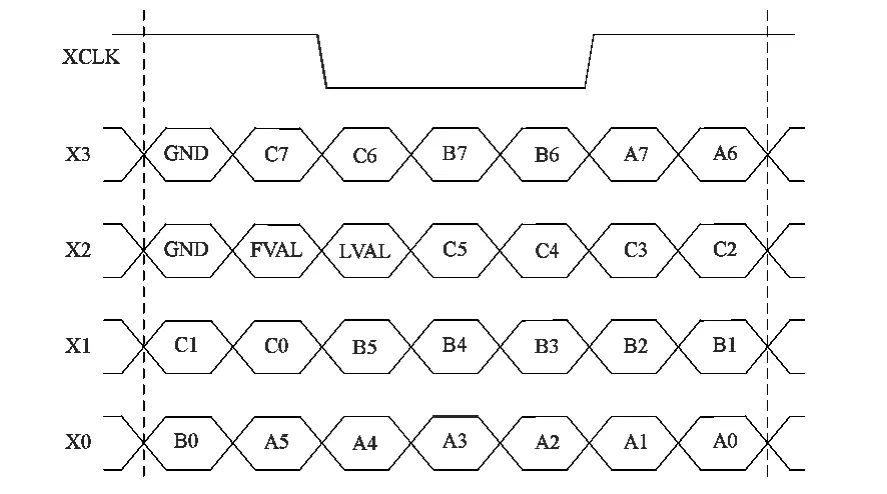

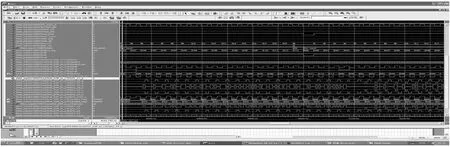

CAMERA LINK为标准工业相机输出接口,其传输信号仍为低电压差分信号,但数据格式异于图像传感器输出的LVDS图像数据,且与并行图像数据之间满足图6所示时序关系,因此可将输入串行差分数据转换为并行图像数据,然后再按照图6时序将并行图像数据转换为符合CAMERA LINK接口时序的差分信号后输出。串并转换和并串转换操作均在FPGA内部完成,尤其在FPGA内部实现的并串转换操作可以省去CAMERA LINK接口转换芯片。编写FPGA程序并仿真,得到串行差分数据接收和发送的功能仿真图分别如图7和图8所示。

图6 Camera Link接口时序图Fig.6 Interface timing of the Camera Link

图7 串并转换FPGA程序仿真图Fig.7 FPGA based simulation results of the SERDES

图8 并行数据转换为Camera Link差分信号的FPGA程序仿真图Fig.8 FPGA based simulation results of the parallel data being converted to differential signals for Camera Link

4 成像实验

基于以上软硬件设计,实现了FPGA对CMOS图像传感器的SCCB时序驱动以及成像参数配置,并基于FPGA完成图像数据接收、缓存及转发模块功能,最终图像通过CAMERA LINK接口传输至图像快速采集显示系统。整个成像系统高度集成,除去光学系统的系统总重量250g;体积4cm×4cm×3cm;功耗2W。另外高质量的光学系统必然会带来高结构刚度要求和大质量的代价,因此在工程应用时还必须从选材和结构形式等方面周密考虑,从而满足微型飞行器或微小卫星对重量、体积、功耗等的小型化设计要求。

图9 成像实验获取图像Fig.9 Image gotten by the imaging experiment

为了验证系统成像效果,开展成像实验,并获取图像如图9所示。实验中,靶标与相机距离13m,理论分辨率为0.364mm,实际获取图像分辨率优于0.5mm,而且获取图像细节丰富,层次分明,达到了预期的设计效果,证明该方案切实可行。

5 结 论

本文针对低成本小型化相机应用需求,提出了一种高分辨率大面阵的小型化成像系统,详细阐述了该系统的电子学方案,并预估了该成像系统用于目标观测的像元分辨率和幅宽。利用3片高集成度CMOS传感器交错拼接的大面阵相机最终重量控制在250g,体积4cm×4cm×3cm,功耗2W。最后基于设计的相机样机开展了成像实验,在13m成像距离条件下获取图像分辨率优于0.5mm,而且图像细节丰富,层次分明。

[1] Kashif G.Camera Design for Pico And Nano Satellite Satellites [M].Lunea University of Technology,2010.

[2] 尤政,于世洁,林杨.基于CMOS图像传感器的纳型卫星遥感器系统设计[J].清华大学学报,2004,44(8):1047-1050.You Z,Yu S J,Lin Y.Remote sensing system for nanosatellite with CMOS imaging sensor [J].Journal of Tsinghua University,2004,44(8):1047-1050.(in Chinese)

[3] 熊平.CCD与CMOS图像传感器特点比较[J].半导体光电,2004,2(1):1-4.Xiong P.Comparison of CCD and CMOS image sensors[J].Semiconductor Optoelectronics,2004,2(1):1-4.(in Chinese)

[4] 邢汝佳.基于CMOS图像传感器的成像系统研究[M].北京:中国科学院研究生院,2007:5-17.Xing R J.Imaging System Research Based on CMOS Image Sensor [M].Beijing:Graduate School of the Chinese Academy of Sciences,2007:5-17.(in Chinese)

[5] 王军,李国宏.CMOS图像传感器在航天遥感中的应用[J].航天返回与遥感,2008,29(2):42-47.WANG J,LI G H.The Application of CMOS image sensor in space remote sensing[J].Spacecraft Recovery &Remote Sensing,2008,29(2):42-47.(in Chinese)

[6] 陶淑苹,金光,曲宏松,等.实现空间高分辨成像的数字域时间延迟积分CMOS相机设计及分析[J].光学学报,32(4),2012,0411001-0411009.Tao S P,Jin G,Qu H S,et al.Design and analysis of CMOS camera based on time delay and integration in digital domain to realize spatial high-resolution imaging[J].Acta Optica Sinica,2012,32(4):0411001-0411009.(in Chinese)

[7] 董岩,张涛,李清军,等.基于PCI总线的CMOS图像传感器OV6620的驱动设计[J].液晶与显示,25(3),2010,460-465.Dong Y ,Zhang T ,Li Q J,et al.Design of image aquision system based on PCI bus[J].Chinese Journal of Liquid Crystals and Displays,2010,25(3):460-465.(in Chinese)