TFT-LCD制程中Sand Mura的失效模式分析及改善研究

2015-05-10史高飞沈奇雨许徐飞韩基挏李乘揆

史高飞,沈奇雨,许徐飞,宋 洁,赵 娜,韩基挏,李乘揆

(合肥京东方光电科技有限公司,安徽 合肥 230011)

1 引 言

当今信息社会高速发展,液晶显示器(TFTLCD)已经深入人们的日常生活,随着人们对液晶显示技术的更多了解,消费者对液晶显示面板画面品质的要求也在不断提高。这些更高画质要求促使液晶面板厂商进一步提升技术并开发高技术规格的产品,因而致使TFT-LCD面板开发生产过程中不断产生新的不良现象[1-4]。

Mura是一种非常影响液晶显示面板画面品质的不良现象,主要表现为有效显示区域内亮度或者颜色显示不均匀。在实际TFT-LCD液晶面板设计生产中,有很多过去未曾发现或难以明确的新型Mura,其具体产生原因多种多样,需要具体情况具体分析及改善[5-6]。

本文研究对象Sand Mura就是一种TFTLCD高分辨率产品开发过程中新出现的Mura问题。本文通过对此不良现象的测试和分析讨论了其产生的原因;同时通过对不良现象发生机理的深入分析,设计一种通过变更像素电极厚度及刻蚀时间的方案来解决此问题,并通过实验来验证改善方案的可行性。

2 实验及过程

2.1 Sand Mura不良现象确认

实验测试面板为8in(1in=2.54cm)WUXGA+ORG ADS产品,Top pixel,面板尺寸为111.64mm×180.274mm。在显示同一灰度或者单色画面时,基板表面出现沙粒状暗点,具体不良现象如图1所示。

图1 Sand Mura现象示意图Fig.1 Schematic of Sand Mura phenomenon

2.2 Sand Mura不良原因分析

从不良现象上看,在Sand Mura不良现象发生区域的画面比正常区域偏暗,怀疑与该不良像素区液晶分子偏转及透光性相关。实验首先通过显微镜观察Sand Mura不良发生位置的像素分布来进行分析,显微镜下的像素分布图如图2所示。从图中可以明显观察到不良区域的部分像素未能被正常点亮,导致了沙粒状暗点不良现象的发生,也进一步证实了之前推测的正确性。

图2 Sand Mura像素分布图Fig.2 Schematic of Sand Mura micro

将实验面板进行拆解(decap)处理并用乙醇去除基板表面残留液晶,观察彩膜(CF)基板对应暗点位置并未发现异常,可以判定不良根源存在于TFT基板。然后,将TFT基板进行切片处理,通过扫描电子显微镜(SEM)和聚焦离子束测试仪(FIB)观察不良位置处的暗点,SEM和FIB结果如图3所示。从图中可以看出,不良处像素ITO电极发生了断裂。分析表明,像素电极发生断裂(Open)导致该处未能与公共电极形成偏转电场,液晶分子不能正常偏转,进而阻挡了光的传播形成暗点。

图3 像素区薄膜的表面和断面图.(a)表面图;(b)断面图.Fig.3 Top and cross section picture of pixel films.(a)Top picture;(b)Cross section picture.

2.3 Sand Mura不良改善

通过上述的分析可知,像素ITO电极Open是导致Sand Mura不良发生的主要原因。然而导致像素电极发生Open的因素很多,可能是由于ITO薄膜沉积厚度的影响,使得有机膜(ORG)过孔和钝化层(PVX)过孔段差位置处产生应力集中,当应力达到一定程度释放时就会导致该处ITO薄膜发生断裂;另外,像素电极在刻蚀过程中的过刻量(Over Etch)也是导致ITO 发生Open的重要因素。

针对上述导致ITO Open的原因,故需要从段差、ITO薄膜厚度以及过刻量3个方面进行改善,在目前量产工艺和设备条件下,通过不同的DOE实验验证找到最合适的各项参数。

首先,为了验证ORG层段差对ITO Open产生的影响,实验中设计了A和B两组实验条件,其中B组为ORG skip参考实验。在A和B组中又设计了不同ITO厚度的验证条件,具体条件(split)信息如表1所示,其中厚度(THK)T1<T2<T3;另外,沉积时加水可以使水分子占据晶格位置,使ITO结晶度降低而变得疏松,减小膜应力,容易刻蚀。

表1 ITO膜厚测试条件Tab.1 ITO Thickness test split item

为了验证沉积完成后ITO Open发生情况,实验中使用宏观微观检查设备Macro/Micro(M/M)对薄膜表面进行微观检查,检查结果如图4所示。

从M/M设备检查结果图4中可以看出,4种不同厚度的ITO薄膜沉积后膜层表面均较为平整,并未出现膜层断裂现象,由此可以判定沉积条件并不是导致ITO Open的原因,并且A和B两组沉积后对比均未见差异。

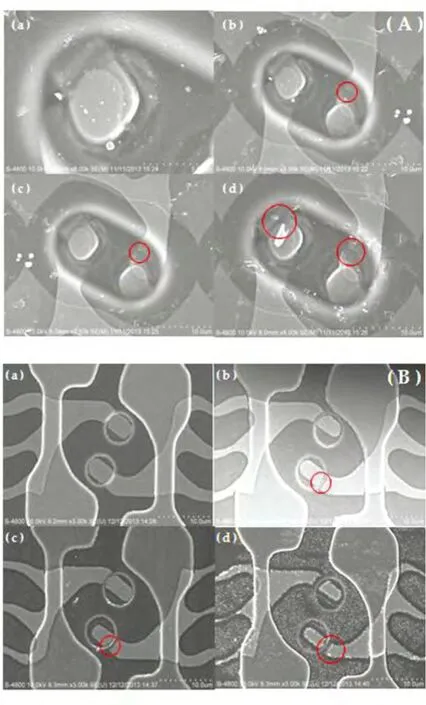

为了进一步验证刻蚀工艺完成后不同厚度膜层对Open不良的影响,实验中对刻蚀完成后A和B两组中的各条件样品分别进行了SEM分析,结果如图5所示。

图4 像素区 MM 图.(a)split1MM 图 ;(b)split2 MM 图;(c)split3MM 图 ;(d)split4MM 图.Fig.4 The MM picture of pixel films.(a)MM picture of split1;(b)MM picture of split2;(c)MM pictureof split3;(d)MM picture of split4.

从SEM分析图中可以看出,刻蚀完成后的ITO均出现了不同程度的Open现象,并且随着膜厚的增加呈现出逐渐加重的趋势。其中split1中除了边缘位置发生Open,其他部分未见Open;当THK大于T1时,Open现象加重,而split2和split3并未出现明显差异,由此可以得出,dep时加水并没有对刻蚀产生较大的影响,而膜厚的变化才是影响刻蚀导致ITO Open的重要因素,另外,由于ORG层坡度角比较平缓,A和B两组刻蚀后各条件也未发现明显区别,分析表明ORG层段差并非导致Open的原因。

为了进一步验证过刻量对Open的影响,而影响过刻量的主要因素是刻蚀时间,本文在上述实验的基础之上设计了不同刻蚀时间的DOE验证实验,具体实验条件信息如表2所示,其中刻蚀时间t1<t2<t3,ITO厚度为T1。

表2 ITO刻蚀时间测试条件Tab.2 ITO etch time test split item

图5 刻蚀后像素区电镜图.(a)split1SEM图;(b)split2SEM 图;(c)split3SEM 图;(d)split4 SEM图.Fig.5 SEM picture of pixel films after etch.(a)SEM pictureof split1;(b)SEM picture of split2;(c)SEM pictureof split3;(d)SEM picture of split4.

实验采用相同条件制备样品,并在同一台设备上进行刻蚀工艺,不同点就是采用不同的刻蚀时间。刻蚀完成之后进行PR胶剥离,然后进行MM观察,发现采用split2条件进行刻蚀时,在玻璃边缘存在轻微的残留现象,其他条件下未发现。对每个split进行FIB分析,分析结果图如6所示。

由FIB图可以看出,split1未发生Open不良,进一步验证了dep条件不是导致断裂的原因;split2和split3也均未出现Open现象,而split4的表面和断面中均可以看到轻微的Open,这是因为在进行ITO刻蚀的过程中,随着刻蚀时间的延长,过刻量增大,CD bias也逐渐增加,而导致Open;同时刻蚀的均匀性(同一块基板上单点之间刻蚀差异,以及不同基板之间的刻蚀差异)和稳定性也随之变差。

图6 刻蚀后像素区表面和断面图.(a)split1表面和断面图;(b)split2表面和断面图;(c)split3表面和断面图;(d)split4表面和断面图.Fig.6 The top and cross section picture of pixel films.(a)thetop and cross section picture of split1;(b)the top and cross section picture of split2;(c)the top and cross section picture of split3;(d)the top and cross section picture of split4.

3 结果与讨论

由以上实验分析表明,ITO沉积条件和有机层的段差并不是导致像素电极发生Open的真正原因,而ITO膜层的厚度以及过刻量才是导致Open并最终产生Sand Mura不良的根源。当ITO厚度增大时,在PVX层过孔处应力集中将会增大,在刻蚀过程中应力释放而导致膜层断裂。根据现有的设备和量产条件,实验最终确定ITO厚度T1为Main条件。当ITO膜层厚度一定时,刻蚀时间的长短将会影响刻蚀过程中的过刻量的大小。当刻蚀时间较短时,过刻量也较小,这就容易在玻璃边缘位置存在残留现象;而当刻蚀时间延长,过刻量增大,CD bias增加,会出现刻蚀不均而在PVX过孔段差处发生断裂。经过实验验证,当刻蚀时间为t2时刻蚀效果最好,即残留和Open现象均未发生。

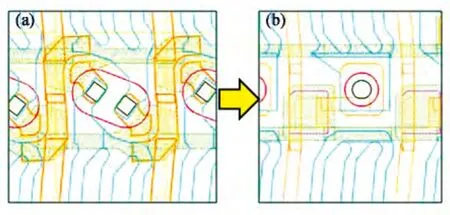

为了消除PVX过孔段差处应力集中及过刻引起的Open问题,从根本上解决Sand Mura不良,可以通过变更设计的方式,变更方案如图7所示。

图7 Mask设计变更示意图.(a)变更前示意图;(b)变更后示意图.Fig.7 Schematic of Mask design change.(a)schematic of before change;(b)schematic of after change.

从设计变更示意图中可以看出,Mask设计变更主要为过孔设计优化,包括以下两点:一方面PVX过孔仍采用小孔设计的方法,而增大像素ITO面积,这样像素ITO与PVX过孔便能充分接触,使得像素电极与PVX过孔段差处的应力相同,以防止Open现象的发生;另一方面ORG大孔设计变更为小孔设计,这样可以防止ORG大孔中PR胶过厚而导致PVX刻蚀不充分的问题。

为了验证这一设计方案的可行性,本文进行了相关的验证实验,实验条件采用与表1中split2相同,以达到对比分析的效果。工艺完成后对样品进行FIB测试分析,测试结果如图8所示。由FIB图中可以看出,Mask设计变更后在像素区表面和断面图中均未发现像素ITO电极发生Open现象,实验结果表明,该设计方案是可行性。

图8 Mask设计变更后像素区表面和断面图.(a)表面图;(b)断面图.Fig.8 The top and cross section picture of pixel films after Mask design change.(a)The top picture;(b)The cross section picture.

4 结 论

研究了在TFT-LCD高分辨率产品开发过程中新出现的Sand Mura问题,通过变更像素电极ITO厚度及刻蚀时间的方案来解决此问题,并验证了改善方案的可行性。实验结果表明:Sand Mura发生的根本原因是由于膜厚影响,像素ITO电极在PVX过孔段差处产生应力,在刻蚀过程中由于过刻而发生Open,导致在通电时该处液晶分子偏转发生异常,进而阻挡了光的透过而形成Mura。通过减少ITO膜层厚度并缩短过刻时间来减小过刻量可以改善Sand Mura问题,不良发生率降至0.3%;本文还研究了通过变更设计方案来防止Sand Mura的发生,实验证明了设计方案的可行性。

[1] 徐伟,彭毅雯,雷有华,等.TFT-LCD横向线状未确认 Mura分析及改善研究 [J].液晶与显示,2013,28(4):539-546.Xu W,Peng Y W,Lei Y H,et al.Analysis and improvement of TFT-LCD horizontal line unknown Mura[J].Chinese Journal of Liquid Crystals and Displays,2013,28(4):539-546.(in Chinese)

[2] 夏子棋.TFT-LCD制造工艺中 White Mura的消除[D].天津:天津大学,2010.Xia Z Q.White Mura elimination in TFT-LCD manufacture process[D].Tianjin:Tientsin University.(in Chinese)

[3] Pauluth D,Taruml K.Optimization of liquid crystal for television[J].SID,2005,13(8):693-702.

[4] Liu C T.Revolution of the TFT-LCD technology[J].Journal of Display technology,2007,3(4):342-350.

[5] 王志龙,郑英花,马亮,等.L0周边 Mura分析及其改善研究 [J].液晶与显示,2014,29(5):668-673.Wang Z L,Zheng Y H,Ma L,et al.Research and improvement of L0side Mura[J].Chinese Journal of Liquid Crystals and Displays,2014,29(5):668-673.(in Chinese)

[6] 齐鹏,施园,刘子源.TFT-LCD touch Mura不良的改善和研究 [J].液晶与显示,2014,28(2):204-209.Qi P,Shi Y,Liu Z Y.Research and improvement of touch Mura in TFT-LCD [J].Chinese Journal of Liquid Crystals and Displays,2014,28(2):204-209.(in Chinese)