一种高速图像实时采编存储系统设计

2015-04-25孙海波吴瑞斌王晓斌

孙海波,吴瑞斌,王晓斌,邱 伟

(北京强度环境研究所 北京 100076)

引 言

在某些武器、飞行器飞行试验中,需要对高速图像进行长时间采集与存储,同时要求设备小型化、低功耗,并能够适应高冲击与振动环境。美国Vision Research公司研制的高速相机,可以支持分辨率为1920×1080、帧频为490帧/s的图像高速、长时间存储。相比之下,国内在该领域的研究还有一定的差距,长春光机所使用FPGA控制2块IDE固态硬盘对Camera Link相机进行图像存储,实现了分辨率为640×480、帧频为100帧/s的10位图像数据存储[1];中科院光电技术研究所采用PCI总线和SAS总线技术实现4块固态硬盘组成的磁盘阵列,可实现150MB/s的高速图像存储,但是结构复杂,功耗较大[2];多家单位采用NAND FLASH阵列存储高速图像,虽然能够达到很高的存储带宽,但是设计复杂,同时需考虑坏块、纠错和损耗均衡的问题[3~5]。

本文介绍的高速图像实时采编存储系统,采用FPGA的LVDS(Low-Voltage Differential Signaling)接口直接采集Camera Link接口工业相机的图像数据,无需采用专用接口芯片,降低了成本、体积和功耗。系统对图像进行编码,以便后期恢复图像并检验是否丢帧,最后将编码后的数据通过LVDS接口发送至数据存储单元,实现高速图像的长时间存储。数据存储单元采用文献[6]介绍的基于SATA接口固态硬盘的高速存储系统,并对该高速存储系统进行改进,数据输入端加入大容量DDR3 sdram缓冲数据,可进一步提高数据吞吐量,最高存储速度可以达到90MB/s。本系统可实现高速图像的实时、长时间采编与存储,并且体积小、功耗低,可适应高冲击与振动环境。

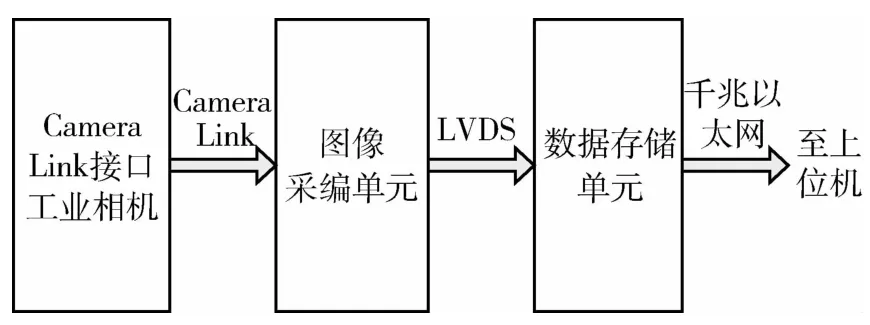

1 系统组成

高速图像实时采编存储系统的组成如图1所示。系统由Camera Link接口工业相机、图像采编单元和数据存储单元组成。图像采编单元实现Camera Link接口工业相机的图像采集和图像编码功能,并通过LVDS接口发送至数据存储单元。数据存储单元采用成熟的模块化存储系统[6],接收LVDS接口的数据,并按照数据帧格式将数据存储至SATA接口固态硬盘中。数据存储单元通过千兆以太网接口完成存储控制和数据上传等功能。

图1 高速图像采编存储系统的组成Fig.1 The architecture of high-speed image acquisition-coding and storage system

2 图像采编单元

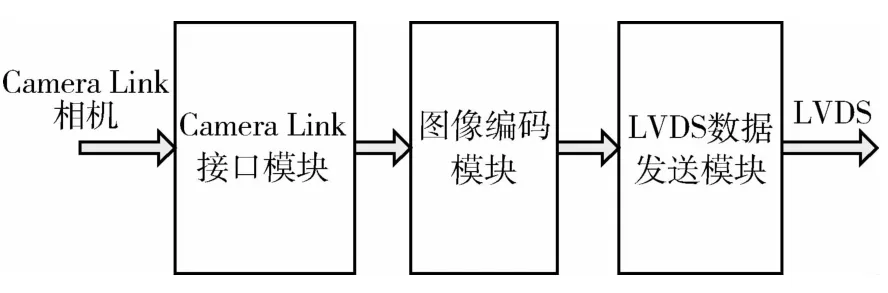

2.1 图像采编单元组成

图像采编单元的功能为实现图像采集和编码:采集Camera Link接口工业相机的图像数据,并将图像数据按照数据存储单元支持的数据格式进行编码,最后通过LVDS接口发送至数据存储单元。图像采编单元采用Xilinx Spartan6 FPGA实现,由以下几个模块组成:Camera Link接口模块、图像编码模块和LVDS数据发送模块,如图2所示。

各模块的功能如下:Camera Link接口模块实现Camera Link接口变换功能,将LVDS串行数据变换为并行数据;图像编码模块完成图像数据的采集和图像帧、数据帧的编码功能;LVDS数据发送模块将编码后的数据帧通过LVDS接口发送至数据存储单元。

图2 图像采编单元组成Fig.2 The architecture of image acquisition-coding unit

2.2 Camera Link接口模块

Camera Link是一个工业高速串口数据和连接标准,它是由多家数码相机供应商和图像采集公司联合推出的,目的在于解决数据传输速率问题。Camera Link标准定义了配套的标准工业接口器件,标准化了信号线类型,简化了相机和图像采集器的信号传输。Camera Link采用LVDS传输数据,速度快,功耗低,抗噪声效果好。Camera Link有三种传输模式:Base、Medium、Full,其中Medium和Full模式是Base模式的并行扩展,传输速度更快。目前在Base和Full模式中,最高传输速率分别可达2.38Gb/s和7.14Gb/s,其传输速率足以满足当今数字相机对高数据传输速率的要求[7]。

目前的Camera Link接口多采用专用接口芯片如DS90CR286和DS90CR287实现,其中DS90CR286实现串并转换,把4对LVDS串行数据信号转换为28位LVCMOS/LVTTL电平的并行信号。LVDS数据信号按照7∶1的比例在驱动器端占用4路LVDS信号通道并行传输,每路LVDS信号在一个时钟周期内串行输出7位数据,共28位数据,有24位是数据信号(其中可能有8位或16位为有效数据),另外4位则分别代表帧有效信号(FVAL)、行有效信号(LVAL)、数据有效信号(DVAL)及保留信号[1,7]。

本设计中,采用FPGA芯片的LVDS接口直接实现Camera Link接口,无需专用接口芯片,节省了成本、体积和功耗。Xilinx公司的spartan6系列FPGA最高可支持1050Mb/s的高速LVDS数据接收和发送,利用FPGA内部丰富的解串器(ISERDES)、锁相环PLL(Phase Locked Loop)和延时(IODELAY)资源,可实现7∶1的数据解串[8]。

Camera Link接口模块的输入输出接口如图3所示。模块输入接口为FPGA的LVDS差分管脚:1对差分时钟信号(clkin_p,clkin_n)和4 对差分数据信号(data_p[3:0],data_n[3:0])。输出信号为时钟信号LVDS_clk、8位并行数据LVDS_data[7:0],以及帧有效信号 FVAL、行有效信号LVAL、数据有效信号DVAL,后级模块可根据这些信号完成图像数据采集。FVAL、LVAL、DVAL和8位并行数据LVDS_data[7:0]在解串后的28位数据中的对应关系没有统一的标准,要根据相机的技术手册而定。

图3 Camera Link接口模块输入输出接口Fig.3 The input and output interfaces of Camera Link interface module

2.3 图像编码模块

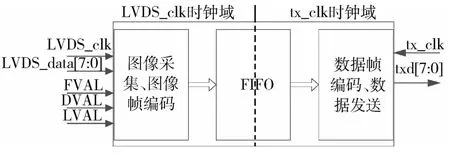

图像编码模块完成图像数据采集,并对图像数据进行图像帧编码和数据帧编码。在图像编码模块中,共对图像数据进行两次编码:图像帧编码和数据帧编码。图像帧编码的目的是标记每一帧图像,以便后期恢复图像数据,并可检验是否丢失图像帧;数据帧编码的目的是使图像数据与数据存储单元的数据格式相匹配,方便数据存储单元进行数据判读和接收,并能检验是否丢失数据帧。

图像编码模块的组成如图4所示。虚线左侧为LVDS_clk时钟域,完成图像采集和图像帧编码功能;虚线右侧为数据发送时钟tx_clk时钟域(tx_clk来自LVDS数据发送模块),完成数据帧编码和数据发送功能。两时钟域之间采用FIFO传递数据。

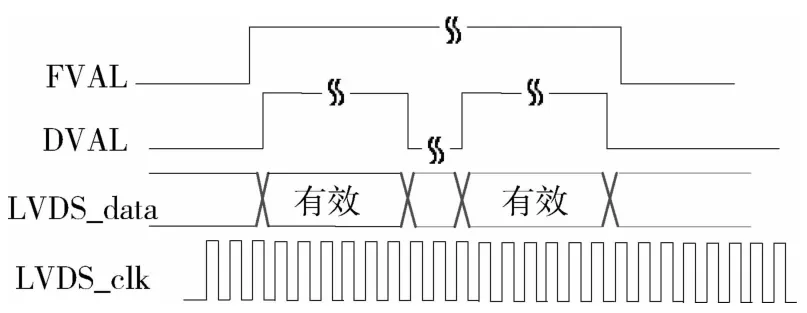

Camera Link接口模块输出的图像信号时序图如图5所示。FVAL信号上升沿,表示一帧图像数据到来,系统开始采集图像数据信号;当DVAL信号有效时,在每个LVDS_clk(图像的时钟信号)的上升沿,输出一次有效的图像数据。以SENTECK公司STC-CL338A高速相机为例,其最高分辨率为644×484,在每个FVAL信号有效周期内,有484个DVAL有效信号,并且在每个DVAL信号有效周期内,有644个有效像素的数据[9]。故每一帧图像的有效数据为484×644=311696字节。

图4 图像编码模块组成Fig.4 The architecture of image coding module

图5 图像信号时序图Fig.5 Timing of image signal

图像编码模块的工作流程如下:从Camera Link接口模块采集一帧完整的图像数据;然后添加帧头、帧计数、帧长等内容,组成一个图像帧(见表1),并将图像帧数据发送至FIFO进行缓存;当FIFO的深度达到4096(数据存储单元要求的数据帧的帧长度)时,读取FIFO中的数据,并添加帧头、帧计数、帧长、帧尾等内容,组成一个数据帧(见表2),同时将数据txd[7:0]发送至LVDS数据发送模块。在图像帧格式中,由于一帧图像的数据量为311696字节,故图像帧格式中数据长度为155848字,而为了节省存储带宽,用一个字表示帧长,这里采用总数据量除以16,即311696/16=0x4C19。

表1 图像帧格式Table1 Format of image frame

2.4 LVDS数据发送模块

LVDS的高速、低功耗、低噪声等特点使其在高速数据传输中得到广泛的应用。与Camera Link接口模块的解串功能相反,LVDS数据发送模块将编码后的数据串行化,并通过LVDS接口发送至数据存储单元。本系统采用两对LVDS数据线,分别为伴随时钟线差分对和数据线差分对。通过内部的PLL配置LVDS伴随时钟的频率,这里配置为87.5MHz,串行解串因子(SerDes ratio)为8:1,即每个伴随时钟周期内传输8bit数据,故数据码率为700Mb/s。

LVDS数据发送模块输入输出接口如图6所示。输入信号为50MHz的本地时钟clkin和待发送的数据信号txd[7:0];输出信号为数据信号差分对(dataout_p,dataout_n)和时钟信号差分对(clkout_p,clkout_n),以及发送时钟tx_clk(87.5M Hz,PLL产生,提供给图像编码模块)。在每个tx_clk时钟的上升沿,接收数据txd[7:0],并在tx_clk的8倍频时钟下,逐位将txd[7:0]发送至数据信号差分对。

3 数据存储单元

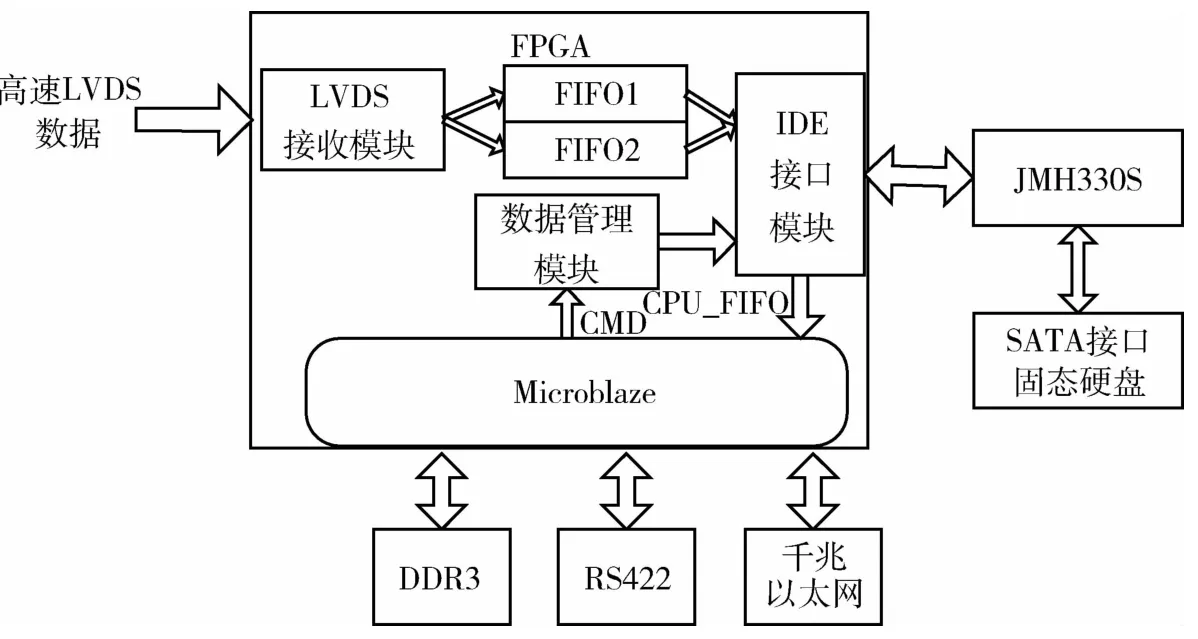

本设计参照文献[6]介绍的基于SATA接口固态硬盘的高速存储系统,文献[6]中LVDS接收模块与IDE接口模块之间使用了32k字的FIFO缓冲数据,本设计的数据存储单元做了以下改进:在LVDS接收模块和IDE接口模块之间添加大容量DDR3 sdram例化的FIFO(FIFO1和FIFO2,各为2M字节容量),两块FIFO交替向IDE接口模块写数据,实现数据缓冲功能,提高数据存储效率,并可防止由于不同型号的固态硬盘速度不匹配引起的数据丢失问题。数据存储单元的组成如图7所示。

图7 基于SATA接口固态硬盘的高速存储系统组成Fig.7 The architecture of high-speed storage system based on SATA interface solid state hard disk

数据存储单元的工作原理如下:FPGA内部的LVDS接收模块接收LVDS数据流并按照数据帧格式将其转换为并行数据。并行数据通过大容量FIFO1和FIFO2交替进入IDE接口模块,在数据管理模块控制下,IDE接口模块读取FIFO1或FIFO2的数据,并通过JMH330S芯片控制固态硬盘进行高速存储(每次存储2M字节);读取数据时,IDE接口模块将读出的硬盘数据存入CPU_FIFO中,Microblaze通过DMA方式将数据读入其DDR3内存,并通过千兆以太网发送至上位机。

4 性能测试

在数据存储单元进行数据存储时,每2M字节启动一次写盘操作,使用示波器观察忙信号。忙信号的平均有效时间为22.3ms,即最大存储速度约为90MB/s。使用87.5MB/s的LVDS数据源对数据存储单元进行大量测试,数据源为累加数据,没有出现数据误码和丢数情况。在图像采编与存储测试中,使用SENTECK公司STC-CL338A高速工业相机,该相机的最高分辨率为644×484、最高帧率为240帧/s,每秒的数据量约为74.3MB,固态硬盘选择三星公司840pro-128G,容量为128GB。经过多次采集存储200s数据,并通过以太网下载至上位机,千兆以太网的平均数据下载速度为22MB/s。经过上位机软件数据分析,数据无误码和丢帧现象,存储的图像数据完整可靠,数据帧和图像帧均连续没有丢帧。测试结果验证了本文介绍的高速图像实时采编存储系统的可靠性。

5 结束语

本文介绍了一种高速图像实时采编存储系统,它采用FPGA的LVDS接口直接采集Camera Link接口工业相机的图像数据,并使用高可靠性的SATA接口固态硬盘作为存储介质,可以实现高速、实时、长时间、高可靠性的图像采集与存储。如果使用多个数据存储单元并行存储,可以支持更高速的图像实时采编与存储。该系统由两块2.5寸电路板和一块2.5寸固态硬盘组成,结构简单,体积小,功耗低,高冲击与振动环境适应性强,可应用于航空、航天等高速图像采集记录领域,具有广阔的应用前景。

[1] 吕耀文,王建立,曹景太.Base型Camera Link脱机存储系统设计[J].光电子技术,2012,32(4):242~45.Lü Yaowen,Wang Jianli,Cao Jingtai.Design of Base Camera Link Video Storage System Independent of Computer[J].Optoelectronic Technology,2012,32(4):242 ~45.

[2] 田 园,任国强,吴钦章.基于SSD硬盘的嵌入式高速图像存储技术[J].光电工程,2009,36(12):138~142.Tian Yuan,Ren Guoqiang,Wu Qinzhang.Embedded Technology of High-speed Image Storage Based on SSD[J].Opto-Electronic Engineering,2009,36(12):138 ~142.

[3] 张 耀,徐智勇,张启衡,等.小型化高速数据记录器[J].仪表技术与传感器,2011,(4):63~65.Zhang Yao,Xu Zhiyong,Zhang Qiheng,et al.Small Sized High Speed Data Recorder[J].Instrument Technique and Sensor,2011,(4):63 ~65.

[4] 吴 萌.一种高速大容量图像存储系统设计[D].西安:中国科学院西安光学精密机械研究所,2009.Wu Meng.Design of High-speed and High-capacity Image Storage System[D].Xi’an:Xi’an Institute of Optics and Precision Mechanics,Chinese Academy of Sciences,2009.

[5] 赵 林.大容量高速数据记录器的设计与实现[D].太原:中北大学,2014.Zhao Lin.The Design and Implementation of Large-capacity and High-speed Data Recorder[D].Taiyuan:North University of China,2014.

[6] 孙海波,王晓斌,李雅梅.基于SATA接口固态硬盘的高速存储系统设计[J].遥测遥控,2014,35(2):48~52.Sun Haibo,Wang Xiaobin,Li Yamei.Design of High-speed Storage System Based on SATA Interface Solid State Hard Disk[J].Journal of Telemetry,Tracking and Command,2014,35(2):48 ~52.

[7] Basler,Dalsa,et al.Specifications of the Camera Link Interface Standard for Digital Cameras and Frame Grabbers(V2.0)[S].USA,2012.

[8] Nick Sawyer.Application Note XAPP1064:Source-Synchronous Serialization and Deserialization(v1.1)[R].USA:Xilinx Corporation,2010.

[9] SENTECK Corporation.STC-CL338A STC-CLC338A User’s Guide(v1.5)[R].Japan: SENTECK Corporation,2013.