Ka波段脉冲功率放大器高速、高可靠设计

2015-03-23夏俊颖赵宪章赵夕彬

夏俊颖,赵宪章,郭 芳,赵夕彬

(1.中国电子科技集团公司第13研究所,石家庄 050051;2.石家庄铁道大学,石家庄 050051)

Ka波段脉冲功率放大器高速、高可靠设计

夏俊颖1,赵宪章1,郭 芳2,赵夕彬1

(1.中国电子科技集团公司第13研究所,石家庄 050051;2.石家庄铁道大学,石家庄 050051)

提出一种Ka波段脉冲功率放大器的设计方法,重点针对高速双脉冲调制开关电路进行了论述,同时针对可靠性开展了热设计,对样机进行了测试,脉冲功率信号上升、下降沿时间≤4.0 ns,可靠性设计满足一级降额要求,各项主要指标满足设计要求,验证了设计方法的合理性和可行性。

高速双脉冲调制;高可靠;毫米波

0 引 言

Ka波段脉冲功率放大器是收发系统中的关键模块,放大器作为系统中功耗最大、发热最厉害的模块,其可靠性对于整个设备的长期稳定运行意义重大。在高速脉冲发射系统中为满足脉冲功率信号的时序要求, 除了要考虑脉冲的频率、幅度及占空比外,实现快速的脉冲前后沿指标也至关重要。

本文针对以上两方面进行技术研究,设计一种高可靠的Ka波段高速脉冲功率放大器。系统要求放大器输入功率Pin=5 dBm,2路输出功率均≥34 dBm,开关隔离度≥65 dB,脉冲功率信号上升、下降沿时间≤4.0 ns。

1 工作原理

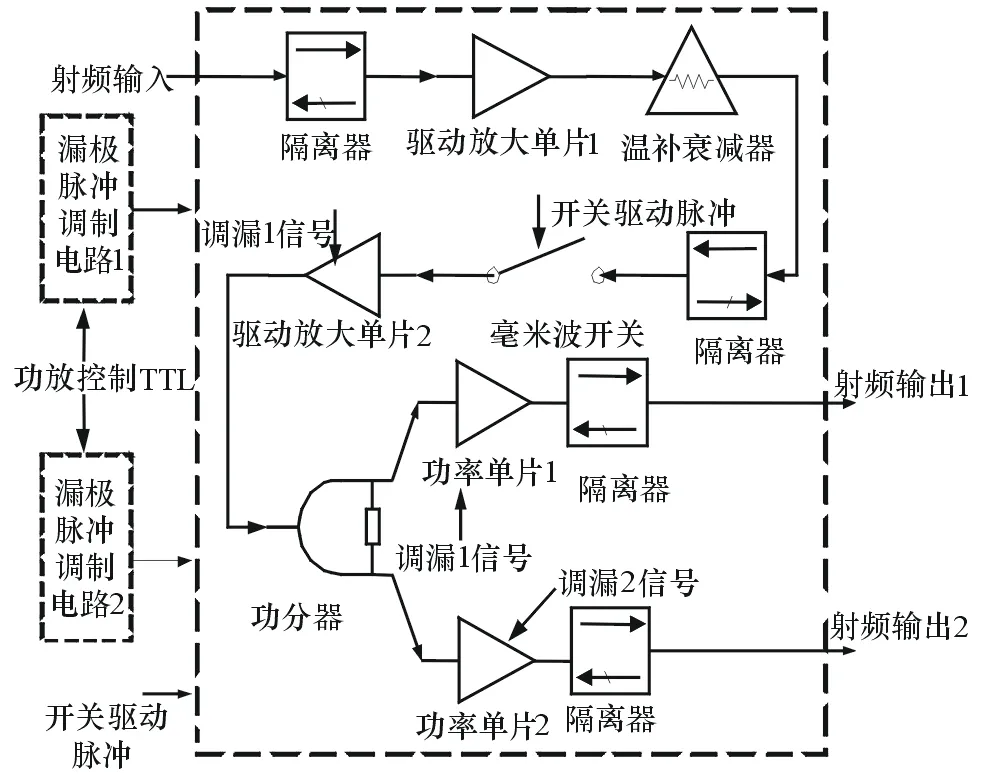

设计的Ka波段脉冲功率放大器基本原理框图如图1 所示,输入信号经2级放大后再进行2路功分,分别经末级放大输出。组件为双脉冲调制工作方式。驱动放大器2及2个末级功率单片均采用功放控制TTL漏极脉冲调制,毫米波开关则外加开关脉冲驱动控制,开关脉冲驱动为低电平时,毫米波开关导通,反之关断。时序图见图2。

2 毫米波通路增益、功率及开关高隔离设计

如图1所示,组件驱动放大器1的增益为15 dB,驱动放大器2的增益为22 dB。为保证传输时延的一致性,末级功率单片1和2选用同一型号的GaAs pHEMT功率单片,增益16 dB,饱和输出功率36 dBm。温补衰减器常温衰减值为5 dB,单个隔离器衰减为0.9 dB,毫米波开关衰减为4 dB,功分器衰减为4.5 dB。通过以上参数可计算出链路增益余量为6.5 dB。这6.5 dB的增益余量及温补衰减器的反向衰减特性,可全温区内保证末级功率单片工作在合适的饱和程度。

图1 Ka波段脉冲功率放大器原理框图

图2 功放控制TTL和微波开关控制时序图

在双脉冲调制电路中,发射驱动脉冲下降沿(即毫米波开关开启时间)比功放控制TTL上升沿延迟100 ns,控制时序图见图2。在这100 ns的间隙期间内,噪声经放大后输出,对后级的接收灵敏度影响极大。因此,必须提高毫米波开关的隔离度以减小信号泄漏对后级接收机接收灵敏度的影响[1]。单级毫米波开关单片在工作频点的插损为0.3 dB,隔离度为46 dB,满足不了组件开关隔离度≥65 dB的要求,因此需要2个该毫米波开关级联使用。考虑到器件端口的输入阻抗经过1/4波长变换到分支节点处刚好为高阻状态,两级该毫米波开关的距离控制在λ/4。经合理的电路及腔体设计后,组件的开关隔离度指标可做到≥75 dB。

3 高速双脉冲调制电路前后沿设计

为实现放大器开关前后沿的高速设计,本组件采用双脉冲调制,使组件经双脉冲调制后的前后沿与毫米波开关的指标一致,达到4~5 ns的高速水平;设计时应注意以下两方面:

(1) 选用高速毫米波开关单片,插损为0.3 dB,隔离度为46 dB,开关前后沿速度为4~5 ns,从器件层面保证组件调制前后沿指标;为保证组件经双脉冲调制后的前沿指标与毫米波开关一致,调整驱动放大单片2和末级功率单片的静态工作点很关键,需要使放大单片工作在A类状态,使单片在静态和动态工作时电流保持一致。根据文献[2],电流上升时间为:

(1)

式中:RG为栅极串联电阻;CGS和CGD分别为pHEMT内部寄生电容;VGH为栅极驱动电压的高电平;VGS(th)为pHEMT的栅极阈值电压;gfs为跨导;IDM为漏极电流的最大值;Von为pHEMT通态压降。

可以看出tri和tfv都与IDM呈正相关,也就是漏极电流的峰值越大,MOSFET的开通速度越慢。电流下降时间tfi有:

(2)

可看出关断过程的电流下降时间tfi与IDM呈正相关。式(1)、(2)中的RG和VGH能在电路中进行调整,RG为图3中R1和R2串联后的阻值,RG取值越小,前后沿速度越快,但如果取值过小又会导致栅流过大,影响长期可靠性;VGH为图3中R1和R2对地串联分压后的电压值,VGH取值越接近0 V,前沿速度越快,但如果取值太接近0 V,又会导致漏电流过大,影响器件长期可靠性。经综合考虑,选用的R1阻值为390 Ω,R2阻值为43 Ω,GaAs pHEMT器件栅压调整到-0.5 V,此时功率单片的静态电流与饱和动态电流基本一致,故不会因动、静工作状态切换时漏电流变化大导致前后沿指标恶化。

(2) 因为漏极脉冲调制会有30~50 ns的展宽,所以功放经漏极脉冲调制的后沿比毫米波开关关断时间滞后30~50 ns,因此组件经双脉冲调制后的下降沿能保持毫米波开关下降沿的水平4~5 ns;考虑到发射驱动脉冲下降沿(即毫米波开关开启时间)比功放控制TTL上升沿延迟100 ns,因此要求功放经漏极脉冲调制的延迟加上功放前沿累计时间控制在70 ns内,以保证功放经漏极脉冲调制的前沿比毫米波开关开启时间提前15~30 ns,进而保证组件经双脉冲调制后的前沿与毫米波开关的指标一致[3]。

本组件的功率器件采用GaAs pHEMT结构的功率单片,从工程设计的稳定性及安全性方面充分考虑后,决定选择漏极调制方式,下面针对漏极脉冲调制电路进行分析。组件实际工作中,对驱动放大单片2和末级功率单片进行漏极脉冲调制,考虑到PMOS管承受电流能力有限,因此采用2组相同电路形式的漏极调制电路,该电路的单组电路图如图3所示。

图3 漏极调制电路图(单组)

电路用到的主要器件包括PMOS管及MOSFET驱动器。选用的PMOS器件主要参数如下:漏源导通时电阻RDS(on)为0.02 Ω,脉冲工作状态下源电流ISM额定值为45 A,结温TJ最大额定值为150℃,热阻RqJA为50°C/W,上升沿延迟时间18 ns。选用的MOSFET驱动器主要参数如下:电源电压为+4 V~+12.6 V,N沟道峰值输出电流为7.6 A,P沟道峰值输出电流为1.3 A,传输延时≤12 ns。设计该漏极调制电路需要注意以下3点:

(1) 为保证组件的脉冲调制开关前后沿高速设计,需要尽量缩短MOS器件栅极的上升沿及下降沿时间,因此MOSFET驱动器P_OUT和N_OUT之间的串联电阻(见图3中的R3)应尽量小,本组件中该电阻值为0 Ω。

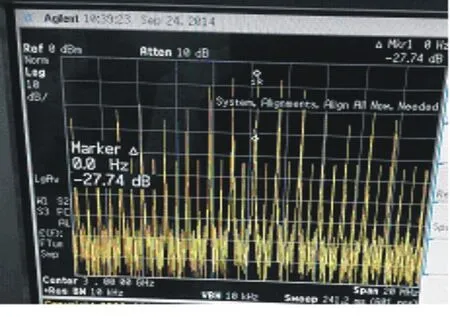

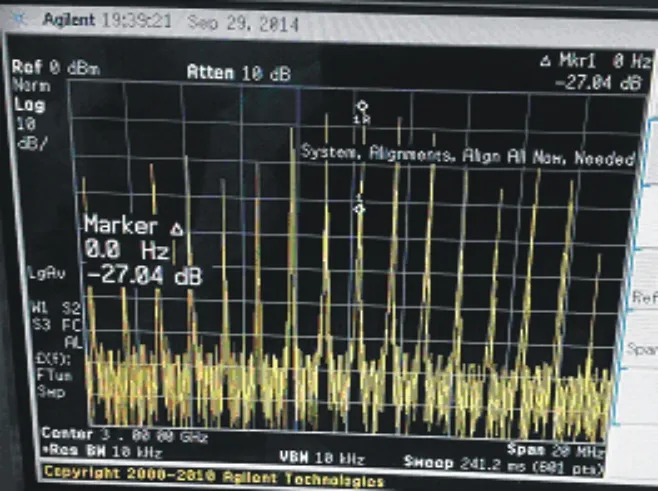

(2) 因为漏极调制电路处理较高的1.08 MHz信号频率,过高的di/dt容易引起振荡,低温工作时容易产生杂波(含杂波频谱波形,如图4),因此需要在MOSFET驱动器V+引脚对地之间加0.1 μF的旁路电容(见图3中的C2),布板时位置尽量靠近MOSFET驱动器V+引脚,加0.1 μF旁路电容后的频谱波形如图5;为避免因布板走线过细过长引起的自感效应,布板时要注意MOSFET驱动器尽量排布在靠近PMOS管栅极的位置。

图4 旁路滤波前含杂波的频谱波形

图5 经旁路滤波后的频谱波形

(3) 为保证组件带动大电流GaAs PHEMT负载时的高速开关前沿及顶降,需要在Vdd端口对地并联储能电容(见图3中的C3、C4)[4],根据电容定义:

(3)

式中:C为储能电容容量;Q为脉冲工作期间电容上电量的变化量;ΔU为脉冲工作期间电容上电压的变化量。在脉冲工作期间:

Q=Ip×τ

(4)

式中:Ip为脉冲峰值电流(脉冲功放中GaAs pHEMT的工作电流);τ为脉冲宽度。

通过以上公式计算,最终确定组件Vdd端口对地并联的储能电容(见图3中的C3、C4)为2个10 μF电容。

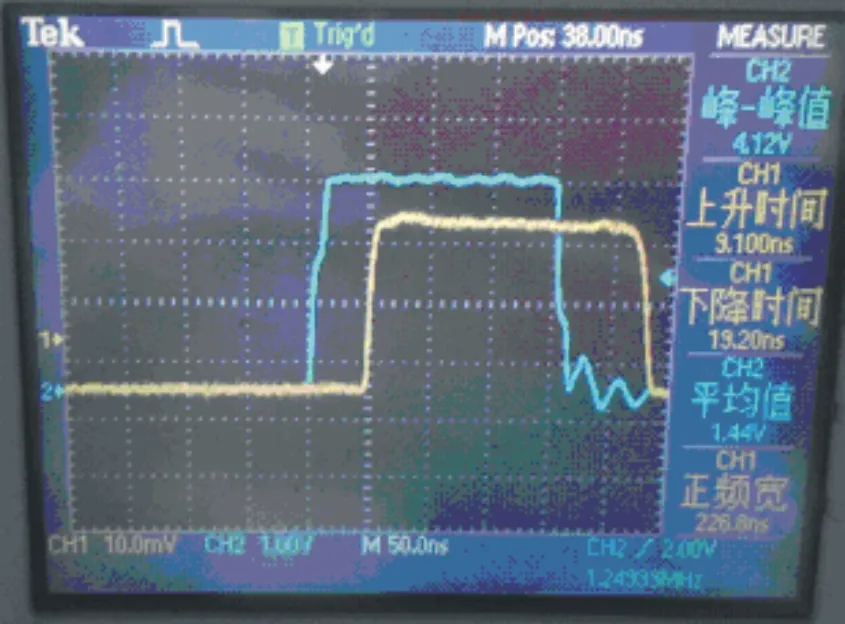

PMOS管及MOSFET驱动器传输延时典型值累加为30 ns,在实际电路中组件经单脉冲漏极调制后的延迟时间做到≤50 ns,如图6所示,满足了本文双脉冲调制电路设计要点中提出的延迟时间≤70 ns的要求。

图6 单脉冲漏极调制的延迟时间示意图

4 可靠性设计及电气指标测试结果

本文主要讨论产品可靠性设计中的热设计环节。所有放大单片均采用烧焊的安装方式,芯片形式的单片用280℃金锡焊料烧焊在钼铜底托上,再将钼铜底托用183℃焊料烧焊在盒体上,确保功率芯片产生的热量有效传导到盒体上。

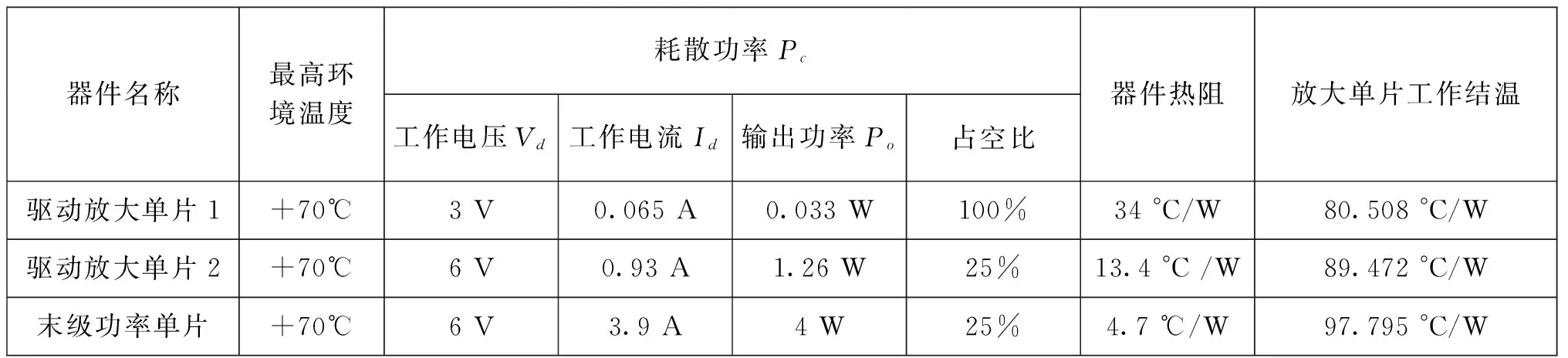

组件工作在脉冲状态下,驱动放大单片2及2个末级功率单片占空比为25%,组件的最高环境温度是+70℃。放大单片的结温计算公式为:放大单片结温=环境温度+耗散功率×热阻+5℃,其中耗散功率Pc=(Vd×Id-Po)×占空比。

根据国军标GJB/Z35-93《元器件可靠性降额准则》的规定,额定最高结温为175℃的晶体管器件,工作结温的I级降额等级标准为≤100℃,Ⅱ级降额等级标准为≤125℃,Ⅲ级降额等级标准为≤145℃。组件用到的发热器件工作时结温均≤100℃,达到I级降额等级标准,最大程度地改善了元器件使用可靠性,实现了组件降额设计及热设计的高可靠性,发热器件结温计算各参数详见表1。

表1 组件发热器件工作时结温计算表

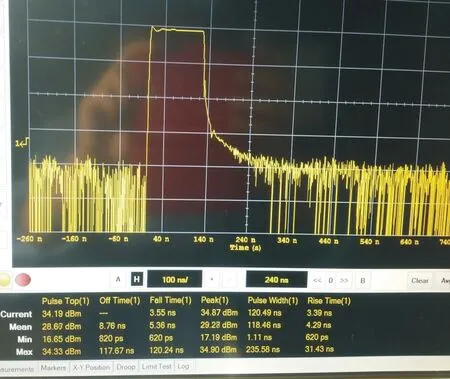

组件测试结果:经双脉冲调制后最终的上升沿指标做到3.39 ns,下降沿指标做到3.55 ns,实现了组件前后沿的高速设计,测试结果如图7所示;组件毫米波开关隔离做到75 dB,优于设计预期指标。

图7 测试结果图

5 结束语

本文给出了Ka波段脉冲功率放大器的基本设计思路, 设计出高速双脉冲调制开关电路,并针对组件高可靠中的热设计进行了分析,样机达到了脉冲功率信号上升、下降沿时间≤4.0 ns的性能指标,可靠性满足Ⅰ级降额要求,验证了设计方法的合理性和可行性。

[1] 王超,陈晓光.Ku 波段固态高速脉冲功率放大器的设计与实现[J].电子器件,2008,31(6):1808-1811.

[2] 王冬冬.大功率固态开关在脉冲功率应用中的特性研究[D].上海:复旦大学,2011.

[3] 胡召宇.Ka频段固态脉冲功率放大技术研究[D].成都:电子科技大学,2011.

[4] 顾占彪,王淼.GaAs FET 脉冲功率放大器输出脉冲包络分析研究[J].半导体技术,2013,38(6):474-478.

Design of High-speed and High-reliability for Ka-band Pulse Power Amplifier

XIA Jun-ying1,ZHAO Xian-zhang1,GUO Fang2,ZHAO Xi-bin1

(1.The 13th Research Institute,CETC,Shijiazhuang 050051,China;2.Shijiazhuang Tiedao University,Shijiazhuang 050051,China)

This paper presents a design method of Ka-band pulse power amplifier,emphatically discusses the high-speed double-pulse modulation switch circuit,at the same time performs thermal design in view of reliability,tests the prototype.The result shows that the rise time and fall time of the pulse power signal are less than 4 ns,and reliability design meets the qualification of the senior downgrade,and each main index satisfies the design requirement,which validates the rationality and feasibility of the design method.

high-speed double-pulse modulation;high reliability;millimeter wave

2015-01-29

T722.75

B

CN32-1413(2015)02-0113-04

10.16426/j.cnki.jcdzdk.2015.02.029