一款可综合全数字锁相环设计与分析*

2015-03-19俞思辰黄永勤

赵 信,俞思辰,闵 昊,王 飙,黄永勤

(上海高性能集成电路设计中心,上海210000)

1 引言

由于全数字锁相环ADPLL(All Digital PLL)拥有较高的集成度、灵活的配置性、快速的工艺可移植性以及不逊于模拟锁相环的相位噪声特性,可以解决模拟电路中电压裕度不足、无源器件面积过大、抗噪声能力不强、锁定速度慢以及工艺的不可移植等瓶颈问题,所以从ADPLL 提出之日起,就受到了广泛的关注和研究。

目前业内所提到的ADPLL 的数控振荡器通常采用LC振荡器设计,并未实现一个完全数字化的设计,主要原因在于完全数字电路设计的DCO(Digital Control Oscillator)的最小调整精度不高,导致量化噪声比较大。但是,随着工艺的提高,单个反相器的延时已经减小到10皮秒以内,那么数控振荡器(DCO)数字量化噪声变得可以接受。受益于工艺的进步,全数字锁相环的抖动性能理论上可以控制在一个反相器的最小延时以内(即10ps以内)。

现今,基本的ADPLL系统结构基本可分为四种:(1)Staszewski R B 等人[1](TI公司)在ISSCC 2004上发表的系统结构;(2)Perrott M H 等人[2](MIT)在JSSC 2008 上 发 表 的 系 统 结 构;(3)Chang H H 等人[3](MTK 公司)在ISSCC 2008上发表的系统结构;(4)Rylyakov A V 等人[4](IBM公司)在ISSCC 2008上发表的系统结构。

这四种ADPLL 系统结构都能很容易地实现分数分频,后面提出的ADPLL结构大多在此四种结构的基础上加以改进。但是,以上结构都包含部分模拟电路,没有实现完全意义上的全数字设计。本文将基于Staszewski R B提出的结构进行改进,提出一款全新的全数字锁相环,该结构全部采用标准单元进行设计,可使用EDA 工具进行综合实现。该结构具有设计周期短、工艺可移植能力强和抗噪声能力强等优点,而且抖动性能可达ps级别。

2 全数字锁相环结构

如图1所示,整个ADPLL系统环路主要包含有Reference Phase Accumulator、Variable Phase Accumulator、TDC(Time to Digital Converter)、Retiming FREF、DCO Period Normalization、Phase Detector、Loop Filter、DCO Gain Normalization、Sigma-Delta Modulator和DCO。而在环路之外,还包含有Presetting OTW_C 和Adaptive Lock and Unlock Controller等环路控制模块。

整个ADPLL的系统时钟CKR 是由Retiming FREF模块产生的,该模块有两个作用,一是产生同步时钟CKR,另外一个是采用一定机制避免时钟的亚稳态。

在整个环路当中,Reference Phase Accumulator 和Variable Phase Accumulator 将 分 别 对FREF和CKV(DCO 的输出)的整数部分相位进行累加(一个CKV 周期为一个单位相位),Reference Phase Accumulator在每个FREF 周期累加FCW,FCW 即为倍频的倍数,Variable Phase Accumulator在每个CKV 周期累加1。FREF 与CKV 之间的小数部分相位差则由TDC 和DCO Period Normalization 来估算。TDC 的输出不能以整数的形式直接给DCO 使用,因为时间分辨率是一个可变的参数,必须通过DCO Period Normalization来归一化,转化为相位误差之后给PD使 用。PD 将Reference Phase Accumulator 和Variable Phase Accumulator的计数值相减,然后与TDC 的输出相加,便得到了FREF 和CKV 的相位差。相位差通过Loop Filter滤波,PLL 一般分为两个阶段,捕获阶段和锁定阶段,捕获阶段为了加快捕获,要求PLL的带宽大,但是会损失噪声性能,进入锁定阶段后,要求PLL 的带宽小,噪声性能好,为了保证不同阶段的无缝对接,在设计Loop Filter时采用了Gear Shifting技术,保证增益的一致性。为了得到更好的噪声性能和精确的频率响应特性,这里在精调阶段使用了IIR 滤波器。

DCO Gain Normalization是为了消除PVT 对环路增益的影响,通过DCO 增益估计技术,使得DCO 和DCO Gain Normalization整体增益为一个常数,这样便抵消了PVT 变化对DCO 增益的影响。Sigma-Delta Modulator用来减少小数部分的spurs,但是会增加噪声。

Figure 1 ADPLL structure图1 ADPLL结构

而在环路之外,ADPLL 的整个锁定过程(从粗调到精调的过程)以及失锁过程都将由Adaptive Lock and Unlock Controller模块进行自动检测并加以控制;另外,由于此次设计的DCO 粗调模式拥有常数KDCO特性,因此可以通过Presetting OTW_C 模块来预先设定DCO 粗调模式的控制位,从而加速ADPLL的粗调锁定过程。

此系统架构与Staszewski R B 所提出的ADPLL架构非常类似,它们的不同之处在于:(1)DCO Gain Normalization只被应用在精调(Tracking Mode)模式下。这主要是由于在粗调模式的锁定过程中,DCO Gain Normalization并不能解决由较大的频率动态范围(1.5GHz至2.5GHz)所引起的稳定性问题。另外,在锁相环直接相位调制的应用中,粗调模式下的KDCO也并不需要被精确估计。(2)在环路之外,加入了Adaptive Lock and Unlock Controller模块,此模块将自动检测Phase Detector模块输出的Phase Error以及Loop Filter模块输出的NTW(Normalized Tuning Word)信号,从而自动控制ADPLL的锁定以及失锁的过程。

该结构基于数字标准单元库实现了ADPLL的可综合设计,解决了纳米工艺下模拟电路的一系列瓶颈问题,而且可以达到和模拟电路相近的抖动和噪声性能。

3 频域相应建模

根据图1 所示的系统架构,图2 则给出了II型高阶ADPLL在相位域(Phase Domain)的模型。

一般情况下,ADPLL 的环路带宽fC都会小于1/10的参考时钟周期,因此ADPLL 系统在通常情况下可以近似为一个连续时间系统,即可以利用s域的线性模型近似代替z域模型来表征ADPLL的传输特性。由图2可得ADPLL 的开环传输函数为:

其中,fR为基准信号的频率,α、ρ和λi为环路滤波器和IIR 滤波器的参数(三者都为2k形式,其中k为整数,故只需左右移位即可实现乘法功能),2π×KDCO为DCO 的增益,fIIR(s)则为IIR 滤波器在s域中的传输函数。再根据图2 和式(1)可得ADPLL输入到输出的闭环传输函数为:

在使用模拟技术时,PLL 可实现的最大阶数为3,受PVT 的影响,使得高阶系统稳定性变差。但是用数字电路实现时不存在这种限制,可以实现高阶的电路来有效地减小噪声和提高频率响应精度。因为数字实现的环路滤波器对于不同工艺的可测试性、健壮性和可移植性更好。通常在粗调模式锁定过程中,IIR 滤波器并不需要开启(不需要考虑在锁定过程中ADPLL 输出信号的相位噪声),因此可以进一步将式(3)改写成经典的两极点系统的传输函数:

其中,ωn为本征频率,ζ为阻尼因子,两者的表达式分别为:

根据式(3)~式(6),图3给出了ADPLL开环传输函数在特定ζ(约为0.707 1)不同环路参数α和ρ条件下的幅频响应曲线。

可以看出当α=1/128,ρ=1/32768,λ1~λ3=1/8,λ4=1/16 时,相位裕度为47.8,增益裕度为18.6dB,有较好的稳定性能。

4 噪声分析

Figure 2 Model of s domain图2 s域建模

Figure 3 Open loop amplitude-frequency response curves of the ADPLL图3 ADPLL开环幅频曲线

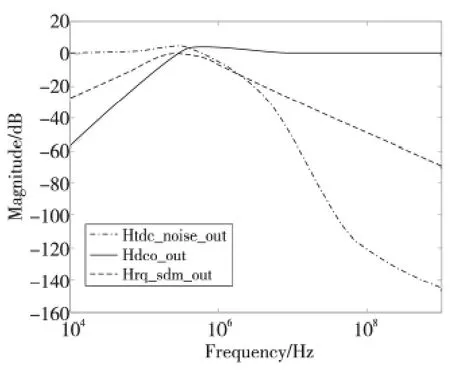

除了需要研究ADPLL 输入基准FREF 到输出的传输特性之外,还需要进一步研究ADPLL 系统中各个噪声源到输出的传输函数,从而能够有效地估算出整个系统输出的相位噪声。如图4所示,在整个ADPLL的s域线性模型中,一共包含四个噪声源。其中Hn,R为基准信号FREF 的相位噪声;Hn,TDC为TDC 电 路 的 输 出 量 化 噪 声;Hn,ΣΔ为ΣΔ 调制器的输出量化噪声;Hn,DCO则包含了DCO的量化噪声以及DCO 的相位噪声。

Figure 4 Noise model of the ADPLL图4 ADPLL的噪声模型

对于Hn,R,其到输出的传输函数如同式(3);对于Hn,TDC,其到输出的传输函数如式(7)所示,所对应的幅频响应曲线则如图5 所示,可以看出TDC具有低通特性。

对于Hn,ΣΔ,其到输出的传输函数如式(8)所示,所对应的幅频响应曲线则如图5所示,可以看出sigma-delta具有带通特性。

最后,对于Hn,DCO,其到输出的传输函数如式(9)所示,所对应的幅频响应曲线则如图5所示,可以看出DCO 具有高通特性。

从图5 中可以清晰地看出,当环路带宽很大时,由于TDC 的量化噪声到输出是低通特性,因此系统总的输出噪声主要来源于TDC(这里假设FREF的相位噪声非常好,对系统总的输出噪声影响不大);而当环路带宽很小时,由于DCO 的量化噪声和相位噪声到输出为高通特性,因此系统总输出噪声的主要来源则变为DCO 的噪声;另外,由于ΣΔ 调制器的量化噪声到输出是带通特性,因此应该合理地选定调制器的Dithering 频率以及ADPLL的环路带宽,从而使ADPLL 输出信号的相位噪声达到所需要的指标要求。

Figure 5 Transmission curves图5 各部分传输曲线

从图6 中可以看出(假定DCO 输出频率为2GHz),首 先,由 于TDC 的 精 度 较 高(10ps 左右),因此其量化噪声对于输出噪声的贡献很小;其次,由于ΣΔ 调制器的存在,DCO 的频率精度变得很高,因此DCO 的量化噪声对于输出相位噪声的贡献也很小。再者,由于环路带宽较小(fC=424kHz),因此在低频处(即环路带宽内)输出相位噪声主要来源于TDC 和DCO 共同的贡献,而在高频处输出相位噪声则都来源于DCO 自身的贡献;最后,正如前面所分析的那样,ΣΔ 调制器的量化噪声会使输出相位噪声在高频处抬高(在200 MHz左右),正因为ΣΔ调制器的Dithering频率为250MHz以及DCO 固有的一阶低通特性,才使其量化噪声在高频处对于输出相位噪声的贡献变的较小。

Figure 6 Impact of ADPLL elements on phase noise output图6 ADPLL各个模块对于输出相位噪声的贡献

5 时域仿真

使用Simulink 对ADPLL 的时序进行仿真,ADPLL 的锁定分为Acquisition 和Tracking 两步,Acquisition的调节精度为10ps,Tracking 调节精度为2ps。Acquisition调节是通过调整DCO中反相器的级数实现的,Tracking 是通过调节某一级反相器的负载实现。

DCO 的Simulink建模如下:

TDCO=KAcqNTWAcq+KTraNTWTra

其中,NTWAcq为相位误差的整数部分,NTWTra为相位误差的小数部分,KAcq为Acquisition阶段的调整精度10ps,KTra为Tracking阶段的调整精度2ps。

时域仿真波形如图7和图8所示,从时域仿真图上可以看出,基于该结构的全数字锁相环的稳定性很好,锁定状态下jitter就是精调的最小分辨率2ps。所以,理论上全数字锁相环的抖动性能可以做到与DCO 的最小调节精度一致。

Figure 7 NTW value of time-domain simulation图7 NTW 时域仿真值

Figure 8 DCO period of time-domain simulation图8 DCO 周期时域仿真值

6 结束语

本文提出了一款改进型的全数字锁相环结构,完全采用标准单元库设计,可使用EDA工具综合实现,具有设计周期短、可移植性强和稳定性好等优点。通过频域建模的方式对系统稳定性和噪声性能进行了分析,最后通过时域仿真的方法证明了该系统的功能正确性,实验表明该结构的抖动性能可以达到DCO的最小调节精度。下一步工作重点将设计一款高精度的DCO,实现最小调节精度为2ps。

[1] Staszewski B,Hung C-M,Maggio K,et al.All-digital phasedomain TX frequency synthesizer for Bluetooth radios in 0.13m CMOS[C]∥Proc of IEEE International Solid-State Circuits Conference(ISSCC’04),2004:272-273.

[2] Hsu C-M,Strayer M Z,Perrott M H.A low-noise,wide-bw 3.6 GHz digital sigma-delta fractional-N synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation[C]∥Proc of IEEE International Solid-State Circuits Conference(ISSCC’08),2008:340-341.

[3] Chang H H,Wang P Y,Zhan J H,et al.A fractional spur free all-digital PLL with loop gain calibration and phase noise cancellation for GSM/GPRS/EDGE[C]∥Proc of IEEE International Solid-State Circuits Conferenc(ISSCC’08),2008:200-201.

[4] Rylyakov A,Tierno J,Turker D,et al.A modular all-digital PLL architecture enabling both l-to-2GHz and 24-to-32GHz operation in 65nm CMOS[C]∥Proc of IEEE International Solid-State Circuits Conference(ISSCC’08),2008:517-632.

[5] Staszewski R B,Hung C-M,Leipold D,et al.A first multi-gigahertz digitally controlled oscillator for wireless applications[J].IEEE Transactions on Microwave Theory and Techniques,2003,51(11):2154-2164.

[6] Tonietto R,Zuffetti E,Castello R.A 2 MHz bandwidth low noise RF all digital PLL with 12ps resolution time-to-digital converter[C]∥Proc of Euroup Solid-State Circuits Conference(ESSCIRC),2006:150-153.