一种分布式纳秒级精度时频同步系统设计

2015-03-16王小青

包 健,王小青

(总参谋部第六十研究所 江苏 南京 210016)

在大量的时频设备中存在同步的要求,特别是一些分布式设备对时基同步有着更高的要求,如GPS系统对每颗在轨卫星的同步;某些科研试验及测量测试过程中同样需要同步,如在频率测量时为了消除测量误差我们会对信号源和频率计进行同步。同步的方法和方式各有不同,可以通过无线介质传输同步信号,也可以通过有线介质传输同步信号;可以通过主站分发同步信号,也可以在分布设备中分别使用更高稳定度的时基。文中设计的是一种基于有线介质的主从站[1]分布式高精度同步系统。

1 系统概述

该系统采取了一种主从站分布式射频发射的方案实现高精度的同步,这种方式的自主性和稳定性相对较高,不像GPS授时同步方式会受GPS卫星限制和无线链路相位脉冲模糊特性的影响。系统中各从站发射信号的上升沿相位差控制在5 ns以内,发射设备采用5MHz的信号作为从站时基。同步误差控制原理如图1所示。

图1 误差控制精度示意图Fig.1 diagram of the error control accuracy

从站间5 ns的同步精度的实现需要从站同主站间的同步误差必须控制在2.5 ns内,为了达到这一要求,主站稳定度最低要求为2.5×10-9/s。同时考虑所采取的数字测频技术对时间的要求,大约每10 s进行一次主从站间的频率同步和上升沿相位误差测量。这样稳定度就要提高一个数量等级,即-10次方量级[2]。

2 系统硬件设计

2.1 主从站同步方式与时基选择

主站通过有线屏蔽介质分发同步信号到各个从站的同步方式,这种方式可以有效避免无线通信方式中可能存在的强电磁干扰。

主站选择短期稳定度、飘移等指标控制在1×10-11/s量级的铷原子钟[3]作为时基信号;从站选择短稳指标每10 s漂移[4]小于2.5 ns的高稳晶体振荡器[5]作为同步前的时基信号。这种主站采用高精度时基,从站采用低精度时基的方式,可以有效地降低整个系统的成本。

2.2 主站工作原理

主站的功能是生成同步信号。主站的铷原子钟输出信号经过放大整形、增加驱动能力后作为同步信号输出到各个从站,其工作原理框图如图2所示。

图2 主站工作原理结构图Fig.2 Structure diagram of themaster station’swork principle

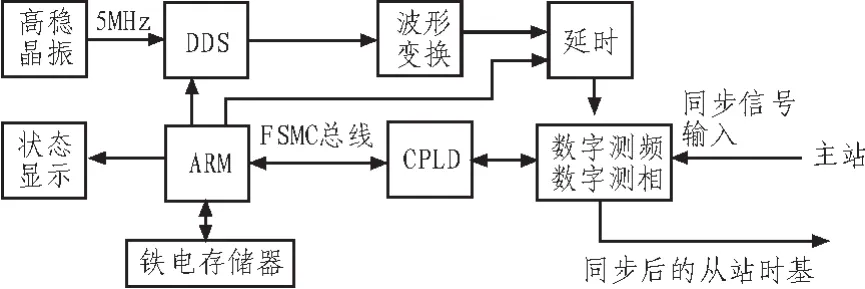

2.3 从站工作原理

从站接收主站的同步信号,并将从站的高稳晶体振荡器输出信号作为DDS芯片的参考信号。CPU采用ST公司的STM32F407芯片ARM处理器,利用FSMC总线从CPLD周期性的读取相频差计数数据并计算,然后通过改变相位增量的方式修改DDS输出信号的频率,实现和主站的频率同步,并通过控制延时元件进行相位调节,其实现原理框图如图3所示。

图3 从站工作原理结构图Fig.3 Structure diagram of the slave station’swork principle

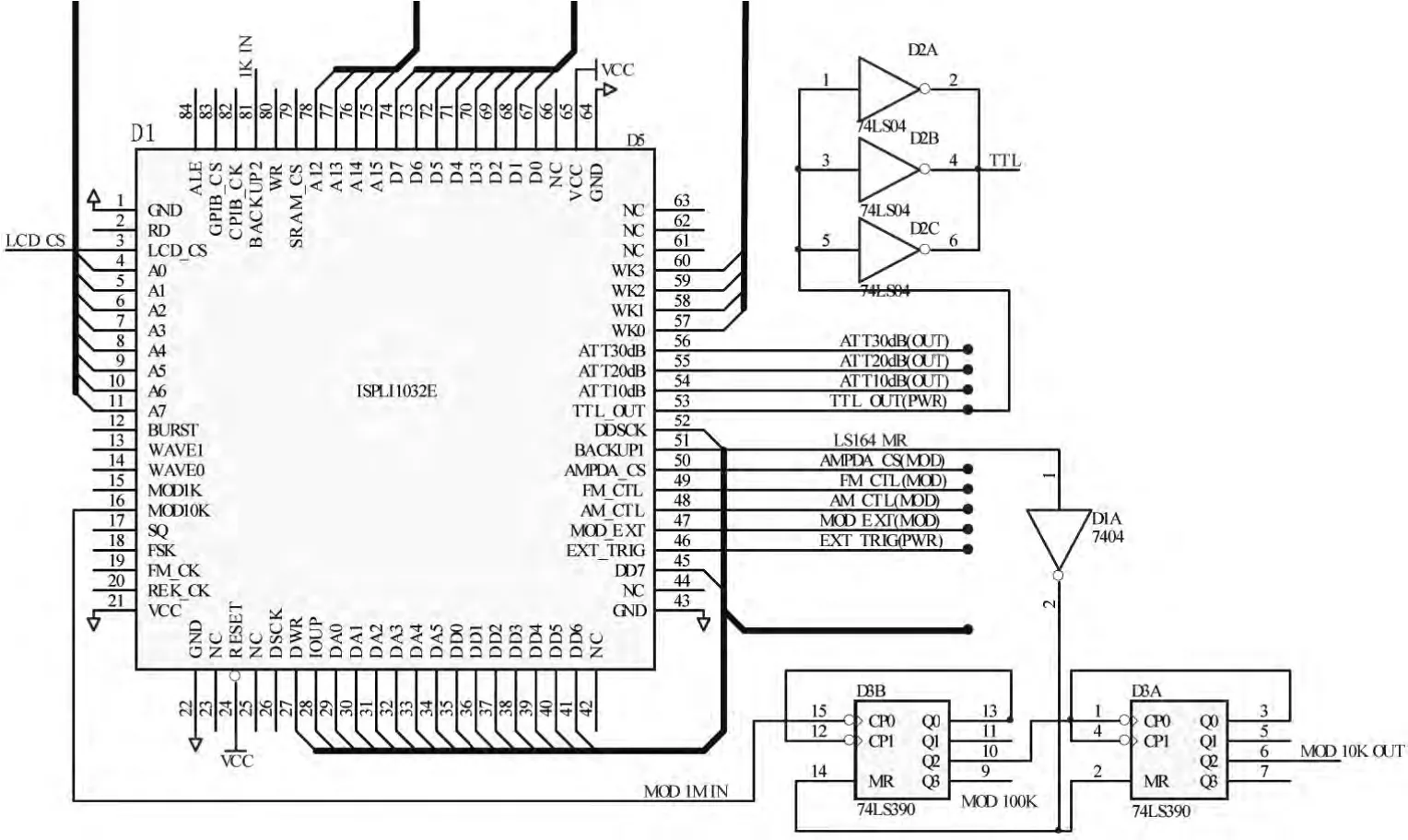

CPLD采用Lattice公司的ispli1032E芯片实现,用于测量同步信号和本从站信号之间的频差和相差;此芯片共有84脚,具体芯片脚定义如图4所示。

图4 CPLD引脚定义图Fig.4 diagram of CPLD pin definitions

2.3.1 模拟内插法等精度频率测量实现

该系统设计中的关键点在于是否能将主从站之间的频率误差测量和调节的范围控制在100μHz以内。系统中使用的等精度频率测量时序原理如图5所示。

等精度测量方法通过计数闸门[7]的设计实现了时基(T)计数器同步于事件(E)计数器,保证了测量精度。但传统的等精度测量误差引入的一个途径就在图5的T1和T2处。我们发现T计数器并没有完全同步于事件,从而产生了不完整的计数脉冲,局部放大后如图6所示。

图5 等精度测量的时序Fig.5 Sequence in time of the same accuracy frequencymeasurement

图6 测量误差引入点Fig.6 Entry points of themesurement error

在引入内插法前提高等精度频率测量的精度一般有两个途径:1)提高计数时钟频率;2)延长闸门时间。以100 MHz时钟,1s闸门为例,理论测量精度只有1×10-8。模拟内插法的引入就是为了对T1和T2误差时间进行测量,在T计数器的时间中去除,从而提高测量精度。这种方法的原理是对误差时间进行放大,然后对放大后的误差计数,完成计数后再缩小相应的倍数,从而计算出误差时间。

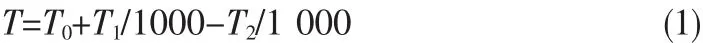

系统中采用电容充放电方法实现模拟内插。CPLD计数模块采用计数法测得时间间隔T0,并对展宽1 000倍并整形后的扩展信号时间间隔的T1和T2脉冲进行采样计数,再由CPU对计数进行计算,就可以得到实际信号的时间间隔,如式(1)所示。

模拟内插电路实现原理框图如图7所示。

图7 模拟内插实现原理图Fig.7 diagram of the simulate interpolationmethod

将输入同步信号经整形处理后作为图5中的闸门控制信号,用来测量主站同步信号和从站时基信号的上升沿误差,然后通过延时元件进行调整,从而提高测量精度。在引入内插模块后能在同等时钟和闸门条件下提高3个数量级别的测量精度。

2.3.2 DDS调频电路实现

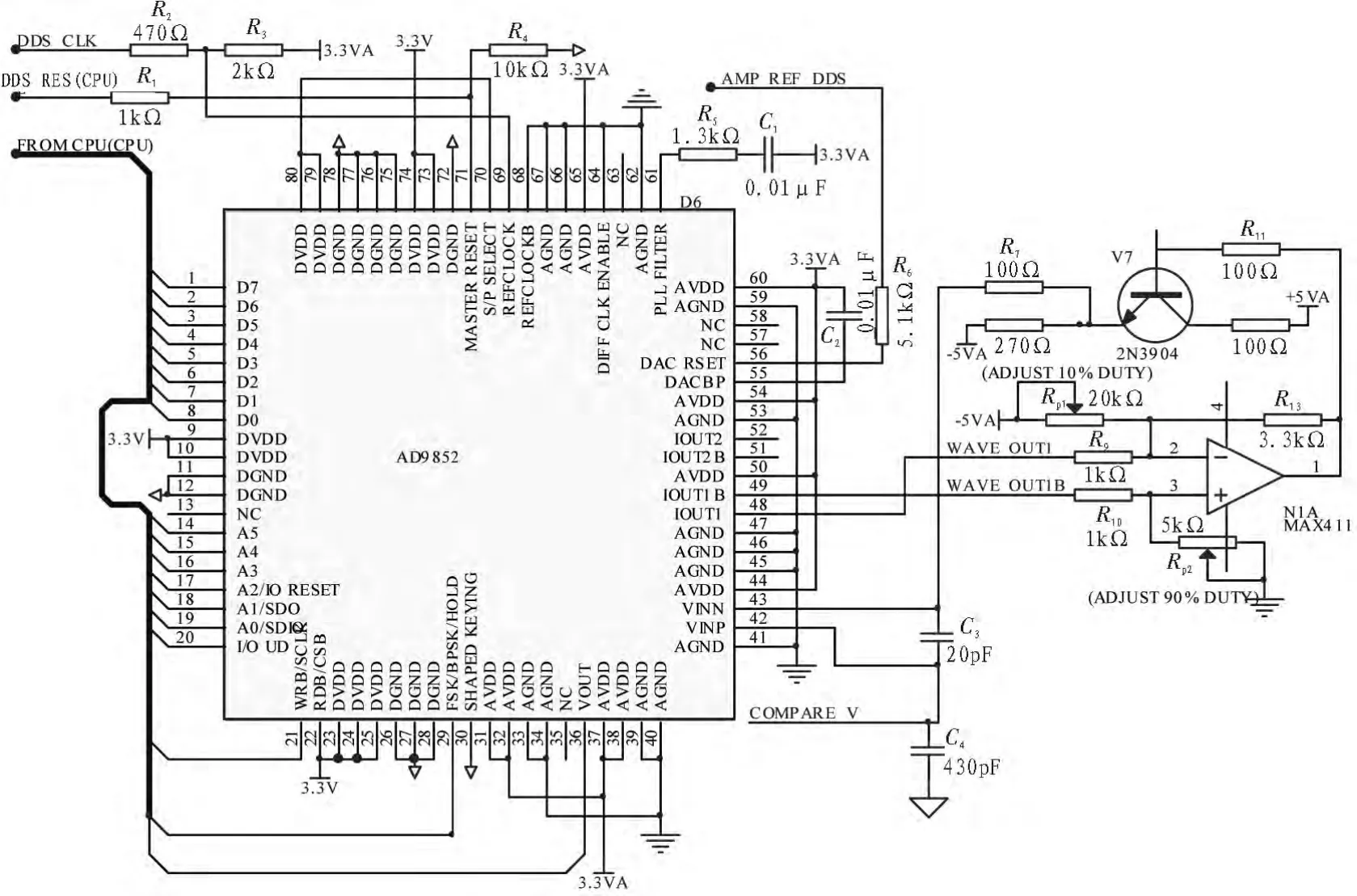

随着器件技术的发展,DDS[8]的相位累加器位数已经很高,相位累加器的位数越高合成信号的频率分辨率越高。在本系统中我们选择一款48位相位累加器的AD9852芯片,可以提供1μHz的频率分辨率。当我们测量出主站同步信号和从站时基信号的频率差后,通过修改DDS的输出信号频率来消除主站和从站之间的频差。在本系统中我们可以把主站和从站间的频率误差缩小到100μHz以内。

DDS的正弦波输出信号需经过内部的超高速比较器转换成数字方波信号才能供CPLD芯片测量。本系统中方波是以正弦波为源,接入AD9852内部比较器的负端(VINN),而正端(VINP)参考电压为零电位,这样就可输出标准的方波,其关键原理图如图8所示。

3 软件设计

在频率测量的过程中需要不断进行动态修正,这是由于:1)频率测量不可能零误差,主从站之间的信号还是存在一个微小的频差;2)同时无论是铷原子钟还是高稳晶体振荡器都存在频率漂移现象。因此从站软件运行过程中也需要不断的测量修正频差,调节信号的相位差,才能实现长期同步。从站软件循环工作流程为初始化→预设闸门1S→脉冲计数→取数计算→相频设置→铁电存储→送显→脉冲计数……。

图8 DDS调频原理图Fig.8 diagram of the DDS frequencymodulation

同步运行期间,若主站同步信号丢失,从站则调用正常同步周期内测得的相频差参数进行动态修正;若主站同步信号丢失且从站死机重启,从站初始化时将读入重启前保存于铁电内的相频差参数进行动态修正。这使得系统能在同步中断的一定时间内还能保持在系统要求的同步误差范围内。

4 结论

这种主从站工作方式的分布式时频同步系统能有效避免强电磁干扰,从站成本低,不受GPS卫星限制和无线链路相位脉冲模糊的影响,从站间同步精度在5ns以内,是一种有效的高精度时频同步的方法,达到了设计要求,具备良好的工程应用价值。

[1]谢春胜.系统间实时同步问题的研究 [J].电子对抗技术,2002,17(6):32-33.

[2]Barnes JA.Characterization of frequency stability[J].IEEE transaction on instrumentation and measurement,1971,20(2):146-160.

[3]李孝辉,吴海涛,高海军,等.用Kalman滤波器对原子钟进行控制[J].控制理论与应用,2003,20(4):551-552.

[4]王志田.频率稳定度测量系统的参考频率源[J].宇航计测技术,1987(5):25-31.

[5]Sullivan D B,Allan DW,Howe D A,etal,ed.Chara cteriza-t ion of Clocksand Oscillator[M].NISTTechnology Note,1990.

[6]黄盛霖,沈聪辉,赵晓娟,等.利用最佳分频实现高精度频率测量[J].兵工自动化,2011,30(9):68-69.

[7]陈芳红,张志文.基于NiosII改进的多周期同步频率测量系统设计[J].仪表技术与传感器,2014(12):56-58.

[8]刘昱,史玉玲,柳莹,等.基于AD9851的正弦信号发生器设计[J].电子设计工程,2009,17(7):14-16.