基于ADS的三阶电荷泵锁相环的研究及仿真

2015-03-16孙越强杜起飞

赵 雪 , 孙越强 , 杜起飞

(1.中国科学院 空间科学与应用研究中心,北京 100190;2.中国科学院大学 北京 100190)

锁相环是一个能够实现闭环相位跟踪的系统,它能够自动跟踪和对比两个频率的相位差,并通过反馈作用达到调节输出信号相位的目的,最终将环路输出锁定在输入频率。基于该特性锁相环已广泛应用于通信、雷达、导航技术、计算机及生物医疗等领域。其中,电荷泵锁相环(Charge Pump Phase-Locked Loops,CPPLL)具有易集成、低功耗、低抖动、无相差锁定等优点,成为当今最热门的锁相环结构之一。

在锁相环的设计过程中,环路带宽是最为重要的参数。本文以三阶电荷泵锁相环为例,首先从理论上分析了环路带宽与环路捕获性能、环路输出总相位噪声之间关系,接着利用ADS仿真软件搭建锁相环电路模型进行仿真验证,最后就如何选择环路带宽的问题进行探讨。

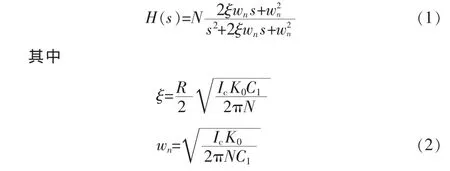

1 环路基本相位模型

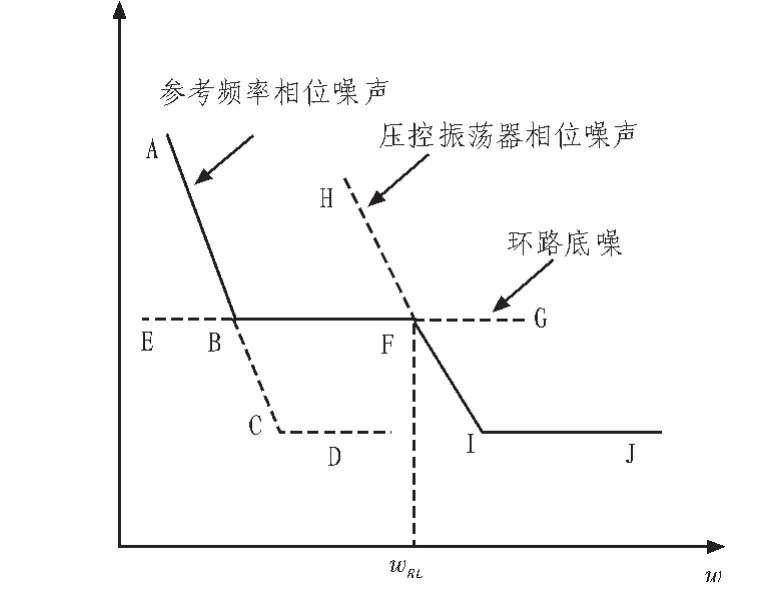

锁相环是一个相位反馈控制系统[1],主要由鉴相器(PD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)和分频器(DIV)构成。图1(a)是典型的三阶电荷泵锁相环电路结构。图1(b)是电荷泵锁相环线性相位模型。该环路的闭环传递函数为:

式(1)中,ξ、wn表示环路系统参数,ξ为阻尼系数,wn为无阻尼振荡频率。式(2)中,Ic为电荷泵充放电电流大小,K0为压控振荡器的压控灵敏度,N为分频比,R和C1为环路滤波器的电阻值和电容值。在不同的情况下,环路带宽的表征方式有所不同[2]。它是锁相环最重要的性能参数之一,通常采用wn来表示锁相环环路带宽的大小。

2 环路捕获性能

图1 三阶电荷泵锁相环相关模型Fig.1 The related models of three order charge pump phase-locked loops

捕获时间是评估环路捕获性能的重要指标,它是指环路从开始到锁定状态所经历的时间,包括频率捕获时间和相位捕获时间。在实际应用中,锁相环在诸如开机、换频或由开环到闭环时,一开始环路总是处于失锁状态,因此环路需经由失锁到锁定的捕获过程[3]。

结合图1(a)所示模型,三阶电荷泵锁相环的捕获时间的一般表达式[4]:

其中,Tf为频率捕获时间,Tθ为相位捕捉时间,wi为参考输入频率。

由式(3)可以看出,环路的捕获性能同系统参数ξ和wn有着密切联系。若要改善环路的捕获性能,使捕获时间变小,可以通过增大环路带宽实现。但是,增大环路带宽与提高环路滤波性能相矛盾。因此,在进行锁相环设计时,环路滤波性能和捕获性能之间需要折中考虑。

3 环路相位噪声模型

相位噪声是电荷泵锁相环的一个重要指标,它是指在系统内各种噪声作用下所表现的相位随机起伏,相位的随机起伏必然引起频率的随机起伏,由于频率的起伏比较快,又称之为短期频率稳定度[5],即相位噪声在时域的表现。在电荷泵锁相环中,噪声来源很多,在进行线性分析时将噪声均看作外部输入,其等效噪声模型如图1(c)所示。

运用线性叠加原理,可得到输出相位噪声为[6]:

其中,θni(s)为参考频率相位噪声;θnp(s)为电荷泵鉴相器相位噪声,即“环路底噪声”;θnv(s)为压控振荡器相位噪声。环路闭环传递函数 H(s)为低通型函数,误差传递函数 He(s)为高通型函数。因此,参考频率相位噪声θni(s)和电荷泵鉴相器相位噪声θnp(s)属于低通型噪声,而压控振荡器相位噪声θnv(s)属于高通型噪声。

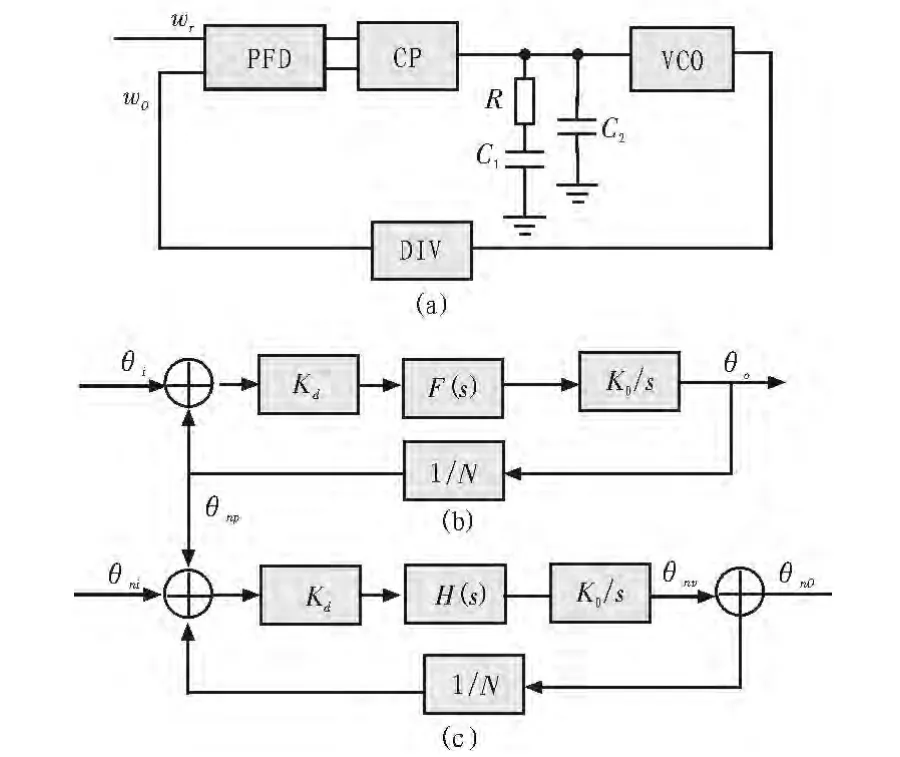

如图2所示ABFIJ段为环路输出总相位噪声曲线。环路输出低通型相位噪声低频段主要受参考频率相位噪声的影响,即图中的AB段;低通型相位噪声的远端主要取决于环路底噪声,即电荷泵鉴相器相位噪声,此类噪声在环路带宽内呈现白噪声特性,即图中的BF段;环路输出高通型相位噪声主要取决于压控振荡器相位噪声,即图中的FIJ段[7]。

由式(4)可知,减小环路带宽,有利于抑制低通型相位噪声;反之,增大环路带宽,有利于抑制高通型相位噪声。因此,环路带宽应存在一个折中的最佳值,可以使环路输出总相位噪声最小。低通型相位噪声和高通型相位噪声的交点F点对应的角频率即是最佳环路带宽wBL。

图2 最佳环路带宽示意图Fig.2 diagram of the optimal loop bandwidth

4 基于ADS的仿真与分析

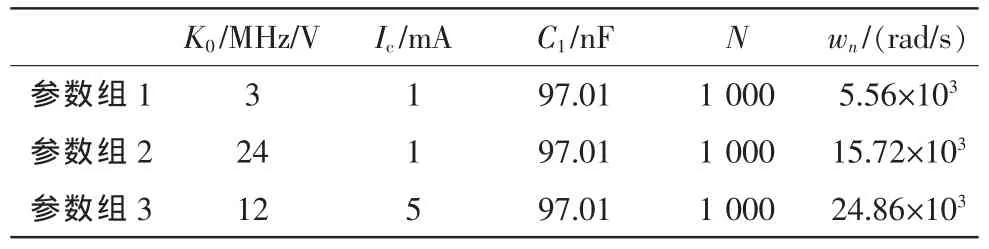

为了进一步验证环路带宽和环路捕获性能、环路输出总相位噪声的关系,本文在ADS仿真软件中搭建环路模型对三阶电荷泵锁相环进行仿真。本次仿真分别采用三组不同的电路参数,根据式(2)可以得到每组参数对应的环路带宽wn的大小,如表1所示。

表1 三组仿真电路参数Tab.1 Three groups of circuit simulation param eters

4.1 环路捕获性能仿真

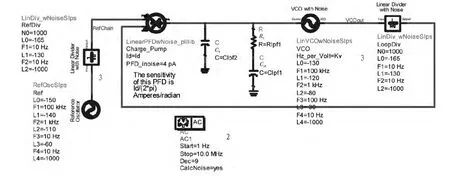

当锁相环路的输入频率发生变化时,会产生瞬时频差,进而产生相位差。鉴于锁相环的相位负反馈功能,环路会根据相位差及时调节误差电压,误差电压经过环路滤波器后转变为控制电压,控制压控振荡器VCO去跟踪输入频率的变化。瞬态响应仿真可以反映锁相环输出频率由压控振荡器自由振荡频率到锁定频率的时域变化,其仿真电路模型如图3所示。在ADS软件的可仿真周期内,调节输入频率,通过仿真还可得到锁相环能够锁定的频率范围。

图3 瞬态响应仿真电路模型Fig.3 diagram of transient response simulation circuitmodel

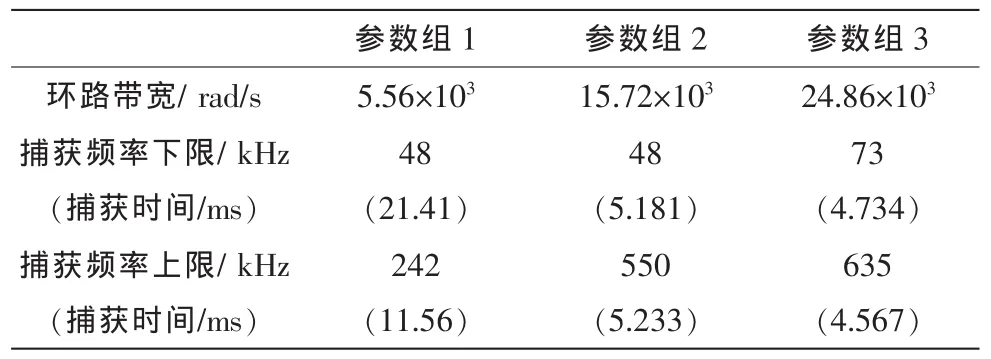

不同环路带宽下环路的捕获频率范围和捕获时间汇总如表2所示。由表中数据可知,环路带宽越宽,系统能够捕获的频率范围越大。这3组仿真所用到的压控振荡器自由振荡频率均为w0=240 kHz,输入频率与压控振荡器自由振荡频率的差值被称为“环路固有频差”。对比参数组1和参数组2的仿真结果,在捕获48 kHz的频率下限时,带宽越宽,系统捕获时间越小,捕获速度越快。对比参数组2和参数组3的仿真结果,在环路带宽为15.72×103rad/s的情况下,锁相环捕获550 kHz需要5.233ms,而在环路带宽为24.86×103rad/s的情况下,锁相环捕获635 kHz仅需要4.567ms,显然也可以得出上述结论。综上所述,本次仿真结果表明,环路带宽越宽,锁相环的捕获频率范围越大,捕获时间也越短,捕获性能越好。但是,环路带宽与锁相环滤波特性密切相关,环路带宽越大意味着环路滤波性能越差。在实际工程设计中,环路的滤波性能和捕获性能需要根据实际应用折中考虑。

4.2 环路相位噪声仿真

环路噪声主要来源于输入参考频率相位噪声、电荷泵鉴相器相位噪声和压控振荡器相位噪声。仿真基于ADS软件搭建的电路模型,如图4所示,对环路带宽与环路输出总相位噪声之间关系进行验证。3组参数仿真结果如图5(a)、(b)、(c)所示,其中PN_PFD_only为电荷泵鉴相器相位噪声,PN_Ref_only为参考频率相位噪声,PN_VCO_only为压控振荡器相位噪声,PN_Total为输出总相位噪声。仿真验证了理论分析结果,即环路输出相位噪声在低频段主要受参考频率相位噪声和电荷泵鉴相器相位噪声的影响,在高频段主要受压控振荡器相位噪声的影响。

表2 捕获性能仿真结果汇总Tab.2 Sim ulation results of capture perform ance

图4 环路输出总相位噪声仿真模型Fig.4 diagram of output phase noise simulation circuit

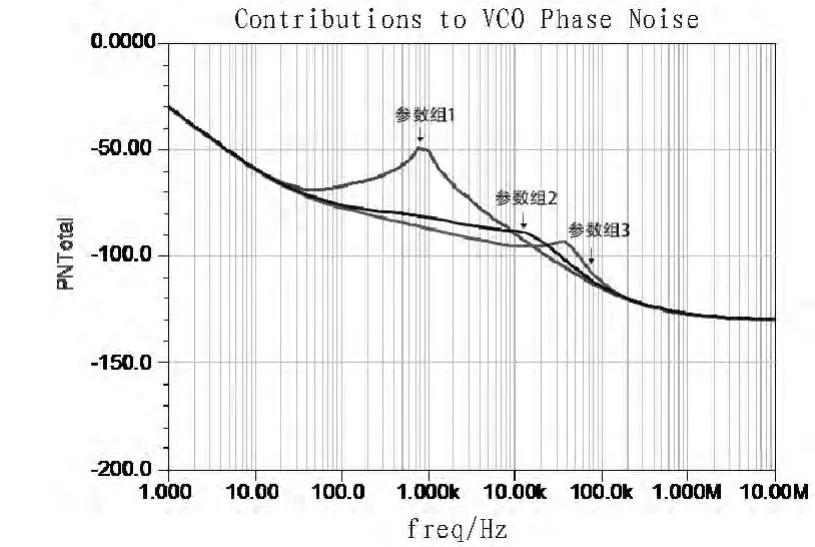

仿真得到的3条曲线中图5(b)的环路输出总相位噪声曲线与图2的理想曲线基本相符。

当实际环路带宽小于最佳环路带宽时,在频率大于实际环路带宽且小于最佳环路带宽处,压控振荡器相位噪声占主导地位且大于低通型相位噪声,输出总相位噪声突然上升,使得输出总相位噪声曲线上出现“尖峰”,且在774.3 Hz处达到最大值,如图5(a)所示;当实际环路带宽大于最佳环路带宽时,在频率大于最佳环路带宽且小于实际环路带宽处,环路低通型相位噪声占主导地位且大于压控振荡器相位噪声,输出总相位噪声曲线在27.83 kHz处出现“凹陷”现象,如图5(c)所示。

图5 环路输出总相位噪声仿真结果Fig.5 Simulation results of output phase noise

通过对比仿真结果与理想曲线可知,在实际设计过程中,可根据输出总相位噪声曲线的特点来判断环路带宽取值是否合理。

如图6可知,环路带宽小或大对于噪声的总抑制性能均不理想。如参数组1条件下,环路带宽小,环路对高通型噪声抑制性能较差;参数组3条件下,环路带宽大,环路对低通型噪声抑制较差。不同的环路噪声模型均存在最佳的环路带宽使环路输出总相位噪声功率最小。在实际应用中,环路噪声模型不同,最佳环路带宽取值也不同。若低通型噪声对环路影响较大,可以适当减小环路带宽;若高通型噪声对环路影响较大 ,可以适当放宽环路带宽。

图6 不同环路带宽下输出总相位噪声曲线汇总Fig.6 Simulation results of the output phase noise with different loop bandwidth

5 结 论

环路带宽的选择对于锁相环电路设计至关重要。借助三阶电荷泵锁相环模型基于ADS仿真对比理论分析可知:不同的环路噪声模型均存在最佳的环路带宽,环路带宽的选取不仅要从降低环路总相位噪声的角度出发,还应综合考虑环路捕捉频率范围和捕获时间。通过对比仿真的环路输出总相位噪声曲线与理想曲线来判断环路带宽是否合理,结合对环路捕获性能的要求,可以达到进一步优化环路带宽的目的。

[1]百创.高性能低噪声锁相环分析与设计[D].国防科学技术大学,2009.

[2]Floyd M.Gardner.Phaselock Techniques[M].人民邮电出版社,2007.

[3]郑继禹,张厥盛,万心平.锁相技术[M].西安电子科技大学出版社,2011.

[4]冯伟平.一种基于CMOS工艺的电荷泵锁相环芯片的设计[EB/OL].[2015-03-16].http://wenku.baidu.com/view/f842c77 002768e9951e73857.htm l.

[5]张建斌.锁相与频率合成[M].科学出版社,2012.

[6]李泽鹏,高玉良,张路.有源二阶锁相环路滤波器设计[J].空军雷达学院学报,2011(6):192-195.

[7]吴文伟.选择低相位噪声频率合成器的最佳带宽[J].电信快报,2000(12):25-28.