基于FPGA的AD采样设计*

2015-03-14许孟杰刘文臣

许孟杰 刘文臣 刘 云

(1.武汉数字工程研究所 武汉 430074)(2.大连船舶重工集团有限公司 大连 116000)

基于FPGA的AD采样设计*

许孟杰1刘文臣2刘 云1

(1.武汉数字工程研究所 武汉 430074)(2.大连船舶重工集团有限公司 大连 116000)

随着现代通信技术的发展,AD信号的实时采样和有效处理在数字化信号接收机的设计中起到重要作用[1]。提出了一种基于FPGA的AD采样设计,给出了同步采样时钟设计方案及FPGA对AD7656的相关配置方法,并对采样数据进行了正弦载波调制和低通滤波处理,最终在Matlab中显示处理后的数据,结果显示该设计方案简单有效,通用性较强。

FPGA; AD7656; AD采样; Matlab仿真

Class Number TP336

1 引言

随着电子技术的发展,嵌入式系统结构的复杂化,现代工业生产和科学研究越来越青睐简单高效的数据采集系统。在本研究中,多通道AD7656采样芯片实现对模拟信号的转换,该芯片最高采样率250KHz;FPGA提供逻辑控制,虽然以传统的DSP或单片机作为CPU的AD采样系统控制简单,但它们不适合完成对复杂的外围电路的逻辑控制,而且软件运行速度较低,而FPGA的电路设计易于软件仿真,节约开发成本和周期,可同时进行采样控制和信号的处理[2]。FPGA接收ADC采样后的高速数据流存入FIFO缓存,同时读取FIFO内数据进行正交变换和低通滤波,最后输出滤波数据给外围信号处理机。

在设计研究初期,很难有实际硬件环境供调试分析,所以采用MODELSIM与Matlab联调的方式,分析原始数据和FPGA输出信号的幅值和频率特性。

2 系统硬件整体设计

AD采样控制的核心部分采用Xilinx公司的XC7A200T-FBG676[3]型FPGA实现对直接数字频率合成器AD9851和采样芯片AD7656的配置。整个系统的硬件结构如图1所示。

由于AD7656芯片对模拟电压的转换范围为以内,所以用于采样的6路模拟信号进入AD7656之前需要低通射随处理,模拟信号通过AD8512来完成电压射随后,经过一个RC网络低通滤波处理才送入到AD7656的输入端,以一路模拟信号为例,相应的低通滤波电路[4]如图2所示,在本设计中有六路相同的低通滤波电路。

图1 系统的硬件结构

图2 低通滤波电路

FPGA配置AD7656控制端口CONVSTA、CONVSTB、CONVSTC及/CS执行模数转换过程,数字信号从三个端口din0~din2输出,每个端口均可进行独立配置是否启动转换,一次转换结束输出两路16bit串行数据,采样后的串行数字信号进入FPGA先转为并行数据存储于FIFO缓存,再进行正交变换和滤波处理,最后输出给后续信号处理机。CLK5610输出两路时钟信号,一路40MHz的时钟输入到FPGA作为系统时钟源,用作FPGA内部IP核时钟驱动;一路时钟作为AD9851的参考时钟输入,AD9851在FPGA的配置下通过内部比较器转化为标准方波再输出给FPGA,该时钟信号稳定度高,可在线编程,被作为AD7656采样时钟源和FPGA读采样数据的时钟。

3 FPGA模块化设计

3.1 AD7656控制设计

AD7656芯片可工作在3路串行模式和16位并行模式下,串行工作模式与并行工作模式由管脚SER/PAR、DB0/SELA、DB1/SELB、DB2/SELC共同决定,具体如表1所示[5]。

表1 AD7656的工作方式

其中16位并行模式下,DB0/SELA、DB1/SELB,DB2/SELC为低三位的数据线。设置采样芯片工作在3路串行输出模式,在设计这些信号时,直接以+5V进行拉高,其中3路串行模式设计的时序如图3所示,AD7656的一次转化完成时间t=Tconv(模数转化时间)+Tacq(串行输出及其他时间)。根据AD7656芯片手册上的要求,Tconv=3μs,Tacq(min)=550ns,Tquit(min)=150ns,已知AD7656采一帧数据计算出的最大采样率为250KHz(4μs),在设计中设定其最大采样率为200KHz(5μs),每完成一次转换输出32bit串行数据,由150ns+32≥2μs,可得到最终基本上确定为18MHz,也即FPGA输出给AD7656的采样时钟,该时钟是由CLK5610输出的一路参考时钟经由AD9851转换,输出稳定度高的18Mhz的方波信号给FPGA,作为AD采样的输入时钟源SCLK。

FPGA控制CONVST端口产生上升沿,并保持高电平,模数转换开始,AD7656芯片BUSY引脚自动拉高表示繁忙状态,任何控制指令在BUSY为高电平期间无法被写入,经过大概3μs的转换时间,FPGA读取BUSY引脚状态为低时,表示AD芯片内部一次转换结束,可以再次写入控制指令,获取输出信号,此时FPGA将/CS拉低,通过采样时钟SCLK上升沿读取32bit数字信号,FPGA计算32个SCLK时间结束将/CS拉高,读数据结束,经过采样结束后的平稳时间段后,CONVST产生下降沿,并保持低电平,一帧数据的转换和读取结束,之后等待FPGA配置CONVST产生上升沿,新的转换重新开始。其中,AD7656芯片的三个CONVST端口均可独立控制,32个时钟状态读取的两路16bit数据,分别是AD芯片输入端两路模拟信号的转换结果,读取的数字信号存入FPGA的FIFO缓冲器,等待后续处理。

3.2 AD9851控制设计

由于FPGA在配置AD7656芯片和读转换数据过程中,对转换时间和控制状态有严格限制,所以需要性能稳定的时钟信号来满足采样时序要求[6]。AD9851主要提供具有较高精度频率和相位的脉冲信号,CLK5610时钟源输入参考时钟,AD9851在FPGA的配置下,将参考时钟转换为采样所需要的18Mhz稳定时钟,DATA0~DATA7是AD9851的8位并行方式数据接口,WCLK和FQ_UP为控制字写入AD9851的控制信号接口,RESET为AD9851的复位信号接口。AD9851包括40位寄存器,其中32位作为频率字,5位作为相位调节字,同时还有6倍频乘法器使能和掉电功能。这些寄存器能够以串行或并行方式载入,8位并行装载控制字功能分配如表1[7]所示,FPGA通过对DATA0~DATA7端口数据的写入来编程40位控制字,实现稳定方波信号的输出。

图3 AD7656的工作时序图

WordData[7]Data[6]Data[5]Data[4]Data[3]Data[2]Data[1]Data[0]W0Phase-b4(MSB)Phase-b3Phase-b2Phase-b1Phase-b0(LSB)Power-DownLogic0*6×REFCLKMultiplierEnableW1Freq-b31(MSB)Freq-b30Freq-b29Freq-b28Freq-b27Freq-b26Freq-b25Freq-b24W2Freq-b23Freq-b22Freq-b21Freq-b20Freq-b19Freq-b18Freq-b17Freq-b16W3Freq-b15Freq-b14Freq-b13Freq-b12Freq-b11Freq-b10Freq-b9Freq-b8W4Freq-b7Freq-b6Freq-b5Freq-b4Freq-b3Freq-b2Freq-b1Freq-b0(LSB)

输出方波信号频率与系统时钟、频率字的关系如式(1):

fout=(ΔPhase×系统时钟)/232

(1)

其中ΔPhase是十进制表示的32bit频率字,系统时钟可以是直接输入的参考时钟,或者6倍频的输入时钟,当参考时钟为180MHz的情况下,要求输出18MHz的采样时钟,设定相位字为0,使能6倍频,由上式计算得出,则FPGA对AD9851芯片写入的40位控制字应该如下:

W0=00000001

W1=10000000

W2=00000000

W3=00000000

3.3 FPGA内部结构设计

经AD7656采样出来的离散时间信号,在FPGA内部进行正弦载波调制和滤波,再输出给后续信号处理机,例如DSP的进一步处理。以一路16bit采样数据为例,FPGA内部具体数据流程如图4所示。

图4 FPGA内部结构图

从AD7656读取的16bit串行数据转换为16bit并行信号存入到第一级FIFO中,第一级FIFO输出16bit数据分别与和相乘,根据离散傅里叶变换的相关特性,时域相乘,在频域实现频谱搬移,其中载波频率的值由CORDIC核的输入角度决定,由于采样频率为200KHz,设定CORDIC核输入数据长度为N,若取载波频率为,则输入角度与及之间的关系如式(2)所示:

(2)

经乘法器输出的两路16bit并行信号分别输入到FIR编译器进行卷积运算,输出信号取高16位作为有效数据经下一级FIFO缓存输出给后续信号处理机处理。

设输入到FPGA的原始离散时间信号中心频率,经过正弦信号的载波调制,频谱搬移至频段,用通带截止频率为的低通滤波器滤出低频分量,为保证输出信号不失真,应该小于,否则输出部分会出现新的频率分量。如果设定载波频率为20KHz,则对该FPGA内部结构的分析可以得出,该系统可以滤出20KHz左右频率范围内的数据,具体范围视FIR滤波器通带边缘频率而定。

4 Matlab联调仿真分析

4.1 FPGA仿真分析

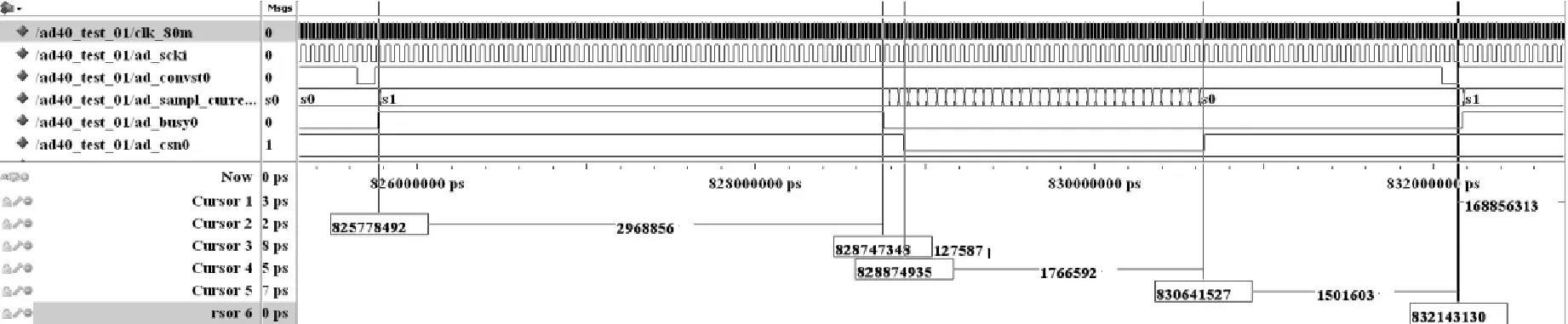

由于AD7656采样频率设置为200KHz,传输方式为串行输出模式,每帧数据采集两路共32bit信号,所以以18MHz的时钟读取16bit采样数据,读入到FPGA中进行正交变换和滤波处理,利用仿真软件MODELSIM输出的仿真波形如图5所示,控制端信号/CS、CONVST与采样时钟SCLK吻合AD7656时序要求。AD_BUSY端信号是仿真分析时输入的激励信号,AD_CONVST产生上升沿一段时间后,AD_BUSY产生约2968859ps的忙信号,约为3μs,等待一段时间,控制端AD_CS产生低电平,低电平保持时间约为1766592ps,由于读采样时钟AD_SCKI为18MHz,可以计算出AD_CS保持低电平期间经过的采样时钟个数,即一帧数据的采样个数为32,从读采样数据结束AD_CS变为高电平到AD_CONVST由低电平重新变为高电平期间经过的时间约为1501603ps,大于AD采样所需的最小保持时间,所以整个仿真时序满足采样需求。

图5 PFGA仿真时序图

由于MODELSIM仿真波形很难直观看出输入输出数据之间的相关性,因此将输出数据导出到Matlab中,分析幅频特性。

4.2 MODELSIM与Matlab联调测试滤波特性

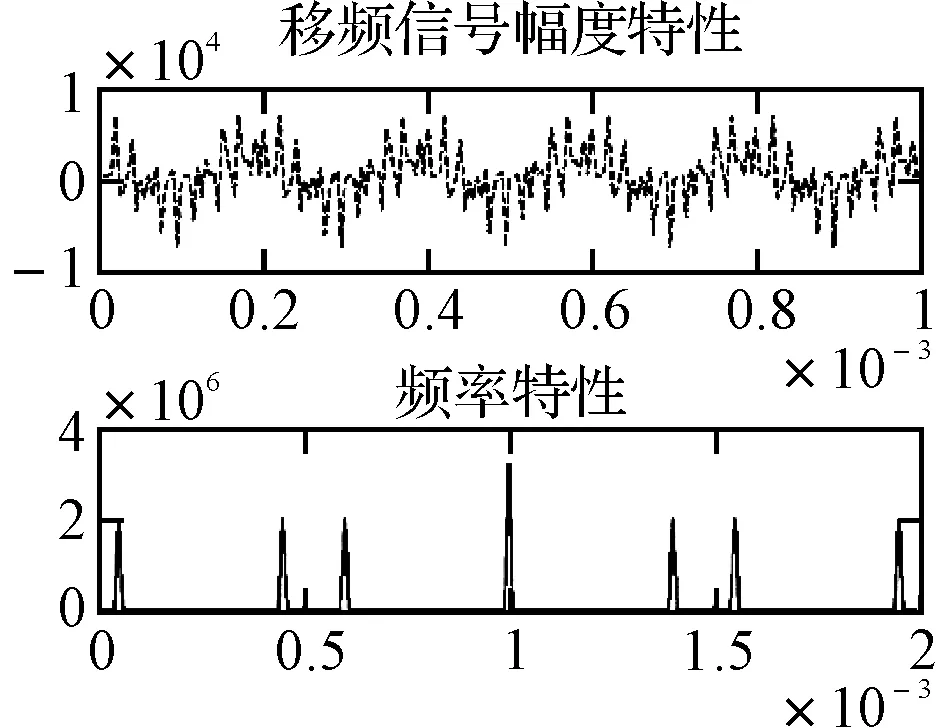

设置输入25KHz正弦信号与80KHz正弦信号叠加,假定80KHz信号为我们不希望有的杂波信号,模拟信号采样频率设置为200KHz,满足奈奎斯特采样定理[6],在Matlab中将采样的离散时间信号转化为16bit数据向量,存储于.txt文件中,利用文件I/O系统[8]导入到MODELSIM仿真系统中作为激励信号,该数字信号幅频特性如图6所示。

图6 带80kHz杂波的数字信号幅频特性图

图7 载波调制后信号幅频特性图

通过在FPGA中配置CORDIC核输入角度设置载波频率为20KHz,输入信号与载波信号时域相乘,频域卷积,实现频谱搬移,调制后的信号频谱图如图7所示。

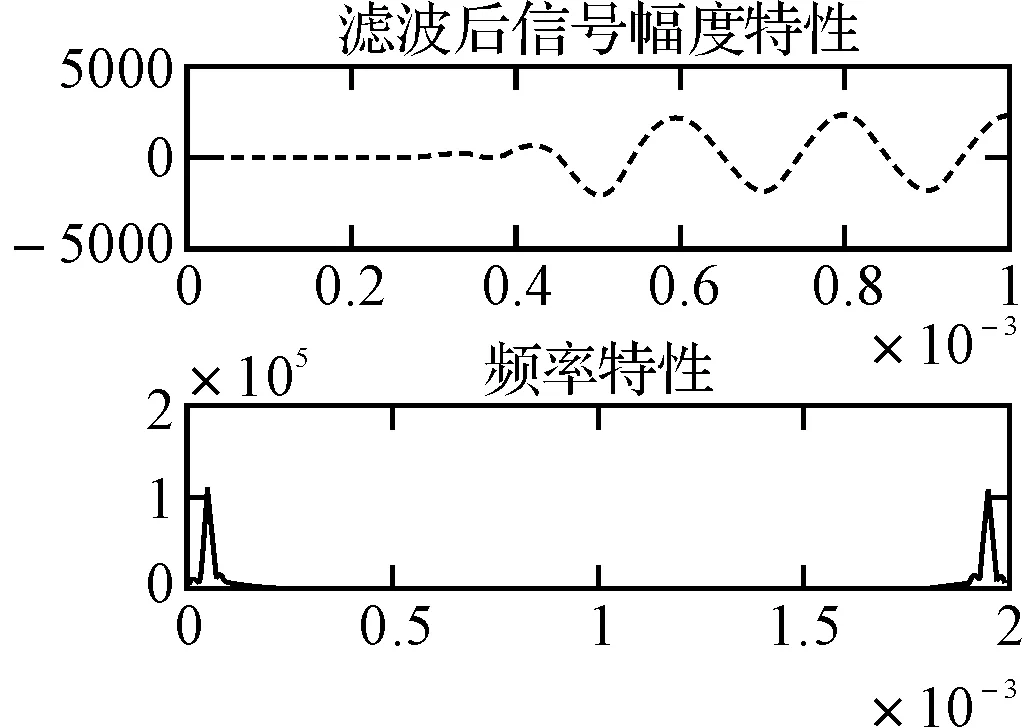

在FPGA中配置FIRCOMPILER核滤波特性,设置滤波器为低通滤波器,通带边沿频率为8KHz,阻带边沿频率为20KHz,输入信号采样频率为200KHz,滤波器系数通过在Matlab中调用KAISERORD窗函数自动生成,通过上图可以看出调制后的数字信号在8KHz以内的低频部分只有一个频率分量,经由配置好的FIR滤波器理论上可以将低频分量取出,如图8是我们在MODELSIM中仿真输出的结果:

图8 滤波输出信号幅频特性图

滤波后的幅度特性图有一段较长的平缓过渡带,产生的原因可以通过对传统单精度FIR滤波器卷积和定义分析,以及对输出数据有效位的处理得出。卷积和定义式[9]如式(3)所示,a(n)表示滤波器系数,宽度为20bit,x(n)表示输入的离散时间信号,宽度为16bit,N等于滤波器阶数,研究中N配置为167,y(k)表示卷积和也就是滤波器的输出值,输出最大精度值的宽度为36,当k较小时,输出y(k)值只是少数滤波器系数和,不能完全反应滤波器特性,且为了节约系统资源,在并不影响输出数据整体特性的前提下,取y(k)高16bit作为有效位输出,所以在输出幅度特性中,k较小时,卷积和较小,取得高16bit位为0,所以幅度特性图中有一段较长的零值曲线。

(3)

因此针对滤波器输出数据特性,可以在FPGA中加入延时采样输出模块,这样可以避免读取无效的滤波输出部分。

5 结语

提出了基于FPGA的多通道AD采样,针对采样芯片AD7656,详细描述了以FPGA作为控制器的采样设计,分析了借助DDS芯片AD9851输出稳定时钟信号的配置方案。考虑到硬件调试的条件限制,采用MODELSIM与Matlab联调的方式,在Matlab中生成理想的离散数字信号,写入到MODELSIM作为系统采样输入激励信号,FPGA仿真输出的数据不能直观显示滤波效果,将其导出到Matlab中,对比输入输出信号的幅频特性,分析滤波特性。实验证明该设计方案数据处理有效,且调试灵活、简单、通用性较强。

[1] 王志刚.基于FPGA的高速数字化接收机与处理技术[D].南京:南京信息工程大学,2009:1-2.

[2] 刘进军.多片AD并行数据采集技术的研究与实现[D].成都:电子科技大学,2009:34-36.

[3] XILINX. Artix-7 FPGAs Data Sheet[M/OL]. 2012. www.analog.com.

[4] 何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2010:79-116.

[5] ANALOG DEVICES Inc. AD7656-1 datasheet[M/OL]. 2008. www.analog.com,2014:1-6.

[6] ANALOG DEVICES Inc. AD9851 datasheet[M/OL]. 2004. http://www.analog.com.

[7] 贾非,郭瑜.基于AD9851型DDS的数字调制系统设计和实现[D].武汉:武汉大学,2008:57-60.

[8] 杜勇.FPGA/VHDL设计入门与进阶[M].北京:机械工业出版社,2010:187-209.

[9] ALAN V. OPPENHEIM, ALAN S. WILLSKY, WITH S. HAMID NAWAB.信号与系统[M].刘树棠,译.第二版.西安:西安交通大学出版社,2007:419-452.

[10] Janusz Mindykowski, Damian Hallmann, Romiald Maasnicki. Acquisition of data from ADC using FPGA: Metrology for Green Growth[C]//Gdynia: Gdynia Maritime University,2012:1-4.

Design of AD Sampling Based on FPGA

XU Mengjie1LIU Wencheng2LIU Yun1

(1. Wuhan Digital Engineering Institute, Wuhan 430074)(2. Dalian Shipbuilding Industry CD. Ltd, Dalian 116000)

Along with the development of the communication technology, Real-time AD Sampling and the effective processing play an important role in the design of digital signal receiver. A kind of AD Sampling based on FPGA is proposed, the design of the synchronous sampling clock and FPGA configuration method for the AD7656 is proposed, the sampling data are processed by sine carrier modulation and low-pass filtering. Finally, the processed data are shown in the Matlab. The experiment results show that the design is simple and effective, highly versatile.

FPGA, AD7656, AD sampling, Matlab simulation

2014年7月13日,

2014年8月27日

许孟杰,女,硕士研究生,研究方向:高性能信号处理。刘文臣,男,工程师,研究方向:压力表计量。刘云,男,硕士,研究员,研究方向:并行计算机技术。

TP336

10.3969/j.issn1672-9730.2015.01.030