采用65 nm工艺实现宽频带低相位噪声的LC-VCO

2015-02-18郑丽斌高海军孙玲玲

郑丽斌,高海军,孙玲玲

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

采用65 nm工艺实现宽频带低相位噪声的LC-VCO

郑丽斌,高海军,孙玲玲

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

摘要:介绍了采用65 nm工艺实现宽频带和低相位噪声LC-VCO。利用相邻两层金属以及多层金属之间的寄生电容来实现堆积式MOM电容。开关阵列电容采用所述的堆积电容来实现,在实现宽频带调谐的基础上可减小VCO的调谐增益。在交叉耦合MOS管的漏极插入电阻来抑制有源器件中闪烁噪声,这种非谐振方式可保证闪烁噪声的抑制在宽频带范围内有效。压控振荡器采用65 nm CMOS工艺实现,测试得到的调谐频率范围为2.7 GHz1.3 GHz;输出频率为1.3 GHz时的相位噪声为-124 dBc/Hz@1 MHz;供电电压为1.2 V时,功耗为2.4 mW;相应的优值为-183 dBc/Hz。

关键词:压控振荡器;宽频带;开关电容阵列;闪烁噪声;堆积式MOM电容

0引言

在现代无线通信系统中,压控振荡器的性能参数比如相位噪声、频率调谐范围以及集成度是影响整个通信系统性能的重要因素。虽然随着CMOS工艺的发展,压控振荡器的性能比如振荡频率、功耗都有很大的提升,但是随着MOS晶体管的沟道长度越来越小,MOS管本身的闪烁噪声对于整个电路影响变得不可忽视[1]。针对尺寸比较小的电路来说,闪烁噪声的抑制变得越来越重要。为了提高VCO的性能,国际上已经提出了多种关于抑制LC-VCO中闪烁噪声的上变频方法。文献[2]通过合理选择差分对中NMOS和PMOS晶体管的尺寸,以实现输出理想差分波形的目的,这样,在一定程度上减小了低频率处噪声上变频,但是使用这种方法时,要求电路必须有完全的对称性,在具体电路版图实现时难以保证。文献[3]提出利用LC谐振网络和电流源实现的噪声滤波技术减小在电流源内部形成的闪烁噪声的上变频,但是由于LC谐振网络的窄带特性,这种方法只适用于窄带VCO中。文献[4]提出利用源阻尼电阻在交叉耦合晶体管中实现抑制闪烁噪声的上变频。但是采用这种方法会对LC-VCO的起振以及1/F3区域内的相位噪声产生一定的影响。

针对以上情况,本文提出在交叉耦合FET管的漏极串联一个电阻的方法,可以有效抑制闪烁噪声在有源电路中的上变频。同时相邻金属层以及多层金属之间的寄生电容形成的与CMOS工艺兼容的堆积式电容构成在宽带LC-VCO中所用到开关阵列。

1宽带低相位噪声LC-VCO电路结构的实现

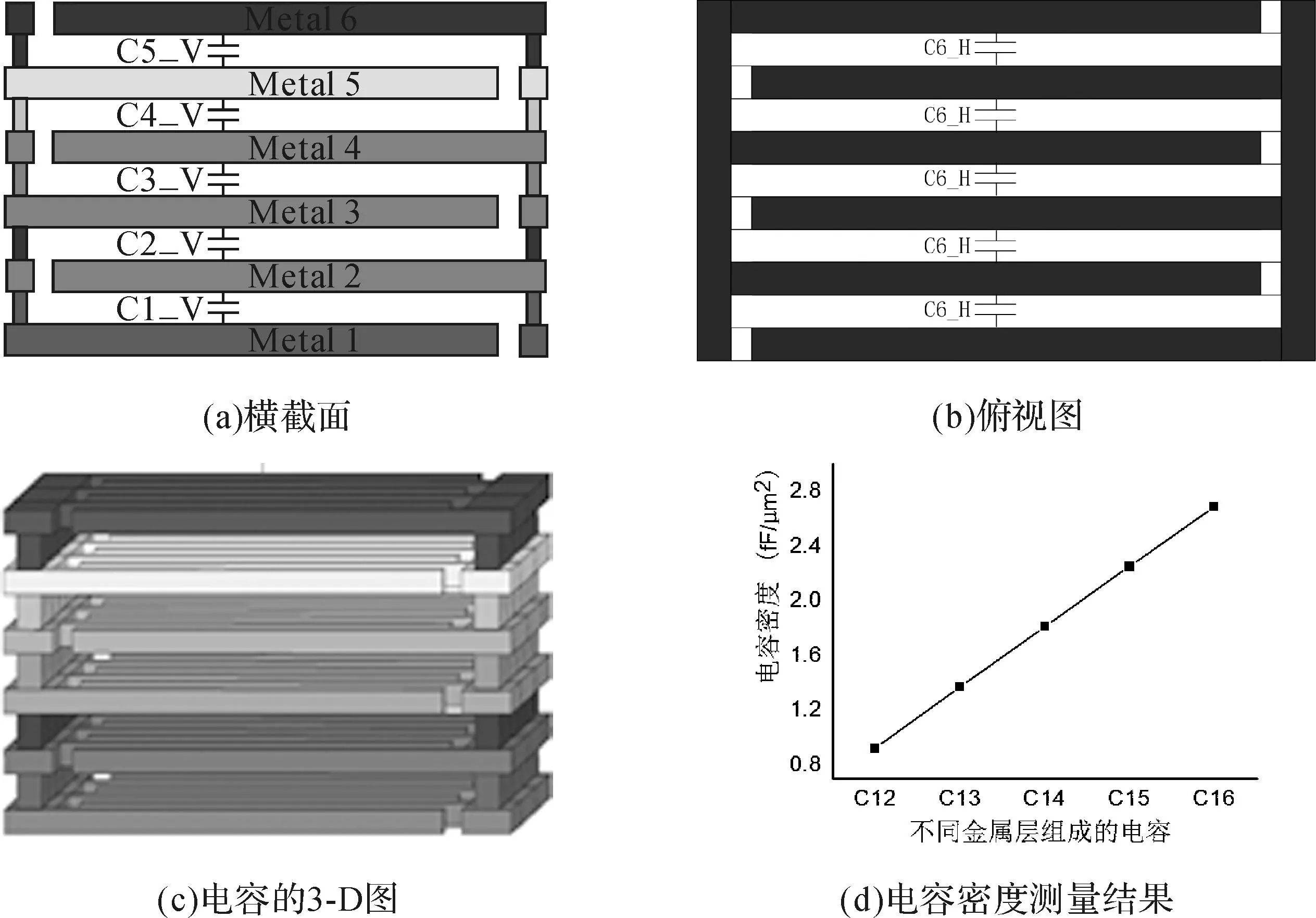

1.1 堆积式MOM电容的设计

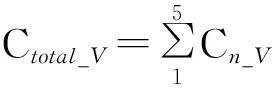

堆积式电容的横截面图如1(a)所示。电容由相邻金属层Metal5和Metal6以及SiO2形成的垂直型寄生电容C5-V组成。它的电容值由SiO2的厚度、金属层的长度和宽度决定[5]。为了使电容密度变大,使不同金属层形成的MOM寄生电容并联连接,由此形成的堆积式电容的总电容值为:

(1)

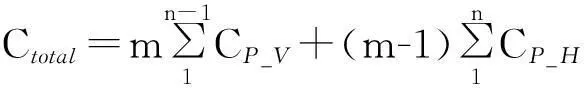

拥有多个叉指数的堆积式电容管的俯视图如图1(b)所示。相邻金属层之间的金属被重新排列在水平面,形成了交叉指型的电容金属层[6]。这种叉指型电容由不同的金属层并联组成,如图1(c)所示。它的总电容值为:

(2)

式中,CP_V为单层垂直型MOM电容的寄生电容,CP_H为单层叉指形电容的寄生电容,n为金属层数,m为叉指数。图1(d)为提出的电容结构的不同金属层所具有的电容值密度的测量结果。电容的尺寸:单个叉指的宽度为0.1 μm,叉指的间隔为0.1 μm,长度为15 μm,一共有160个叉指数。6层金属层在实际应用当中最大的电容密度值为2.8 FF/μm2。

本文所用的堆积式电容也可以被视为二维的叉指形电容:一种为垂直平面拥有多个水平面的叉指数;另一种为水平平面有多个的垂直面的金属层[7]。

图1 堆积式MOM电容的结构

1.2 宽带LC-VCO的设计

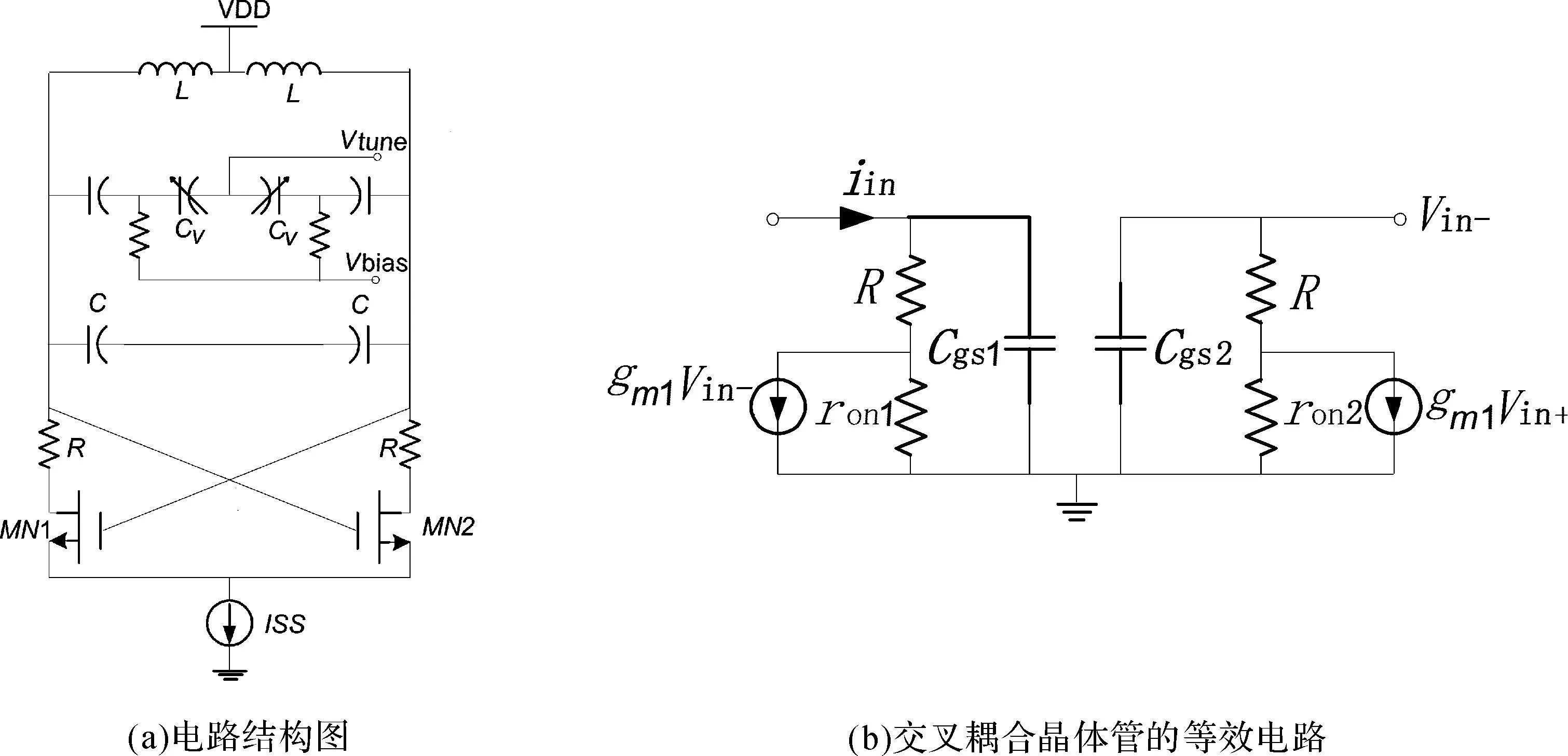

本文中提出的利用漏极串联电阻抑制闪烁噪声上变频的宽带LC-VCO的电路设计图如图2所示。

图2 LC-VCO的电路设计图

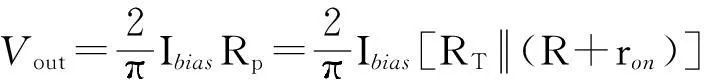

图2(a)中LC-VCO电路图中的交叉耦合FET晶体管的漏极串联两个电阻;图2(b)中给出了交叉耦合管的等效小信号电路。根据图2中的小信号电路求出等效输入电阻:

Zin=(R+ron)/(1-gmron)+1/jωCRs

(3)

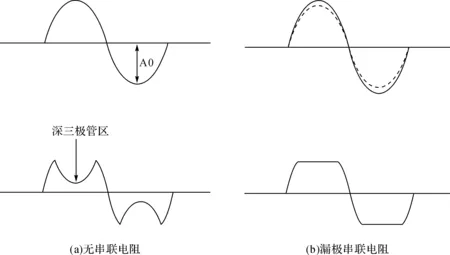

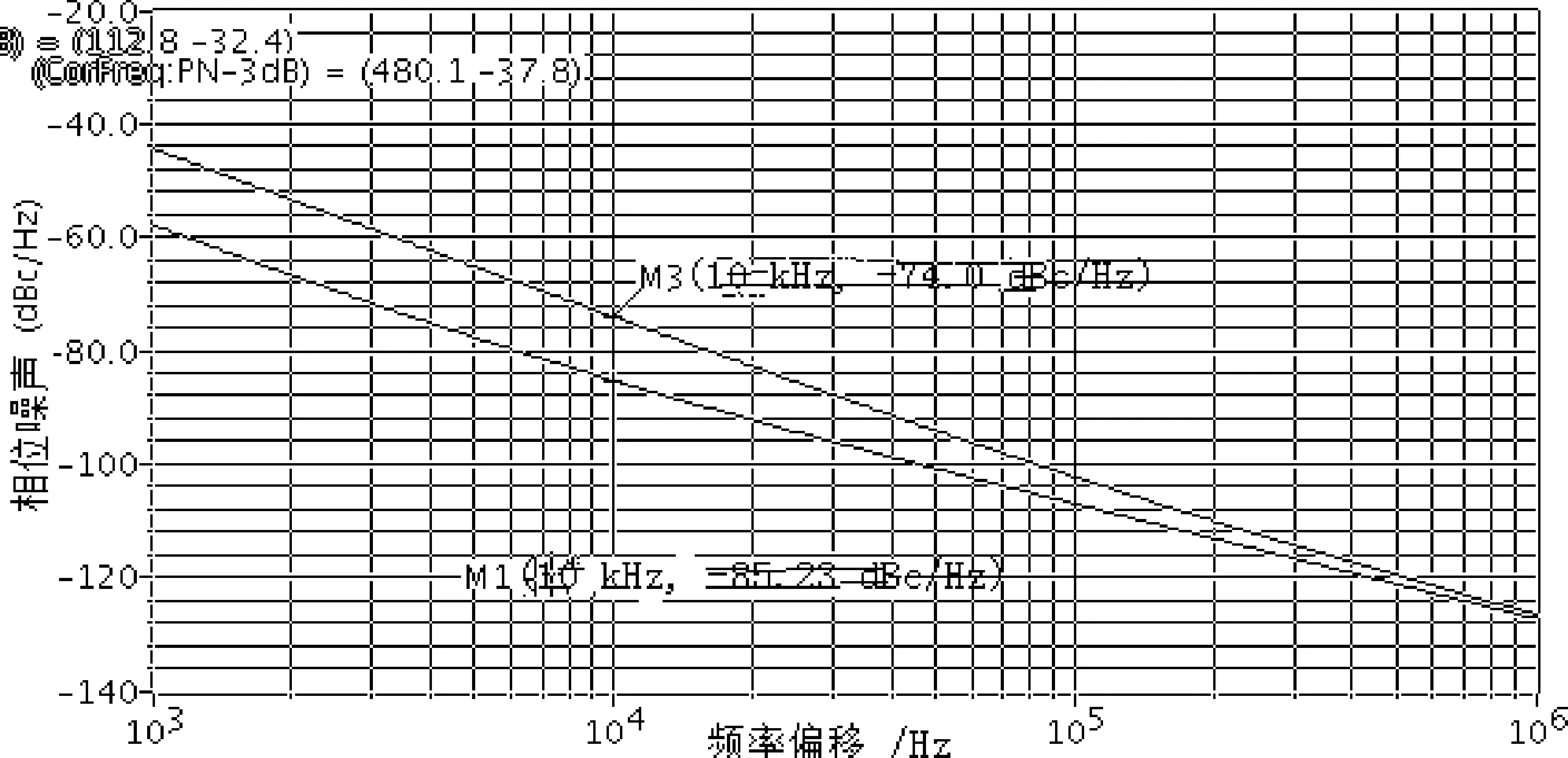

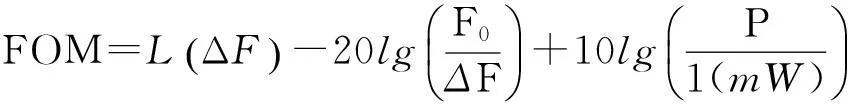

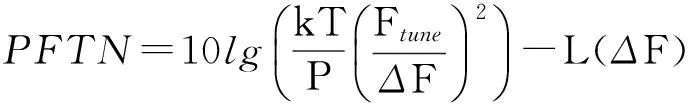

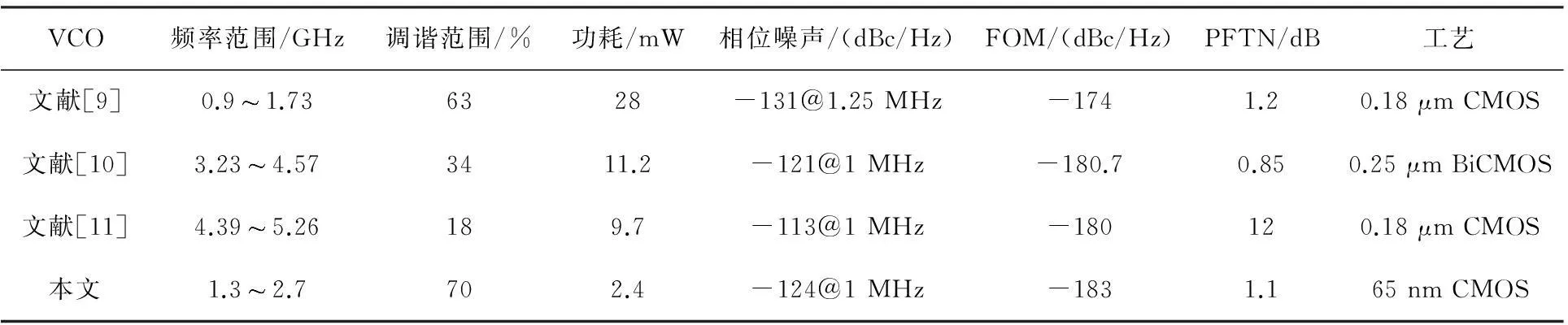

对于一个漏极串联电阻值为R的FET来说,其等效输出电阻rout=R+ron,当MOS晶体管工作在饱和区时,ron>>R。在很多情况下,振荡器的振荡幅度将使得交叉耦合的MOSFET晶体管工作在深线性区,如图3(a)所示。对于压控振荡器的一个信号周期来讲,FET晶体管工作在截止区或者三极管区域,而且流过交叉耦合FET晶体管的电流波形并不是理想的方波信号,只有在电压的过零点处达到其最大值,而在电压的最大值处信号下降。信号下降的幅度取决于工作在三极管区域的FET晶体管的阻值。所以ron越大,电流值的扰动越小。另外根据文献[8]的分析得出,电流的谐波会引起振荡频率点的偏离,同时在电流源附近会导致闪烁噪声的上变频。图3(b)显示了流过交叉耦合晶体管以及与其串联电阻的电流波形。同时,由前面分析得出,当FET晶体管工作在深线性区时,ron< 对于工作在电流受限区的振荡器来说,输出电压幅度为: (4) RT为谐振网络的等效并联电阻。根据上式得出,在恒定电流源的前提下,随着漏极串联电阻的增加,振荡器的振荡幅度将增加。由于谐振网络的谐振频率并不会受漏极串联电阻R的影响,这就意味着在过零点处的波形的斜率会变得更大。所以本文提出的电路结构会减小闪烁噪声的影响,另外由于差分对FET晶体管的存在,使得电路中的谐波成分也在一定程度上得到了抑制[9]。 图3 交叉耦合晶体管的电流波形 本文设计的利用开关阵列实现的宽带LC-VCO如图4所示。为了实现宽带的频率范围,利用堆积式MOM电容实现的5-bits的开关阵列被应用到LC-VCO电路结构中,同时电路图中的2-bits开关变容管阵列可以扩大调谐范围。图4中漏极串联电阻R可以有效抑制闪烁噪声的上变频。图5证明了漏极串联电阻对应LC-VCO的相位噪声的影响。M1曲线对应是电路中存在漏极电阻R时的仿真结果。由图5可以看出M1曲线的相位噪声值为-85.23 dBc/Hz@10 kHz,比M3曲线有10 dBm的改善。同时1/F2噪声并没受到漏极串联电阻R的影响,证实了以上的理论分析结果。 图4 宽带LC-VCO电路结构 图5 漏极串联电阻对相位噪声的影响 2芯片测试与结果分析 本文提出的可抑制闪烁噪声的上变频的宽带LC-VCO以及堆积式MOM电容是利用65 nm CMOS工艺实现的。由于全差分电感电容压控振荡器的两条支路是完全一样的,为了保证实际电路的物理实现也是完全对称的,在进行版图设计时要尽量做到振荡器是中心对称的。版图面积为540 μm×400 μm。供电电压为1.2 V,功耗为2.4 mW。 图6 LC-VCO芯片的测试结果 为了更好地表征VCO的性能,计算FOM的值。FOM定义为: (5) 式中,L(ΔF)为距离载波频率F0为ΔF处的相位噪声,P为功耗值。根据计算得出本文提出的VCO的FOM值为-183dBc/Hz。为了更加合理公平地比较窄带VCO和宽带VCO的性能,通过计算下式来比较宽带和窄带VCO的性能,下式将调谐范围包括在其中。 (6) 利用上述测量数据,得到本文中提出的VCO的PFTN的值为1.1dB。 本文提出的LC-VCO的性能参数与最新提出的宽带LC-VCO的性能比较如表1所示。 表1 LC-VCO性能参数对比 从表1中可以看出,与其他论文中设计提出的VCO相比,本文设计的LC-VCO的FOM值更小。 3结束语 本文利用65 nm CMOS工艺实现了低相位噪声的宽带LC-VCO。利用在交叉耦合FET管的漏极串联电阻R有效抑制了调谐频带范围内的闪烁噪声的上变频。在标准的CMOS工艺中,根据提出的堆积式MOM电容实现的开关阵列可以有效提高了LC-VCO的调谐范围。仿真结果也验证了利用此方法实现的LC-VCO有很好的性能,因此在工程上具有一定的应用价值。 参考文献 [1]Hajimiri A,Lee T H.A general theory oF phase noise in electrical oscillators[J].IEEE Journal oF Solid State Circuits,1998,33(2):179-194. [2]Hajimiri A,Lee T H.Design issues in CMOS diFFerential LC oscillators[J].IEEE Journal oF Solid-State Circuits,1999,34(5):717-724. [3]Ismail A,Abidi A.CMOS diFFerential LC oscillator with suppressed up-converted Flicker noise[C]//2003 IEEE International Solid-State Circuits ConFerence.San Francisco: ISSCC Digital Technology Papers,2003:98-99. [4]Yun S J,Cha C Y,Choi H C,et al.RF CMOS LC-oscillator with source damping resistors[J].Microwave and Wireless Component Letters,IEEE,2006,16(9):511-513. [5]Hauspie D,Park E C,Craninckx J.Wide-band VCO with simultaneous switching oF Frequency band,active core and varactor size[J].IEEE Journal oF Solid-State Circuits,2007,42(7): 1472-1480. [6]Park C H.MOM Capacitor[P].USA: Patent 0155112,2007-07-13. [7]Huang G,Kim S K,Gao Z,et al.A 45 GHz CMOS VCO adopting digitally switchable Metal-Oxide-Metal capacitors[J].Microwave and Wireless Components Letters,IEEE,2011,21(5):270-272. [8]Groszkowski J.The interdependence oF Frequency variation and harmonic content and the problem oF constant-Frequency oscillators[J].Institute oF Radio Engineers,1993,21(7): 958-981. [9]Sung E Y,Lee K S,Baek D H,et al.A wideband 0.18-μm CMOS ΣΔ Fractional-N Frequency synthesizer with a single VCO For DVB-T[J].IEEE Asian Solid-State Circuits,2005:193-196. [10]Nakamura T,Masuda T,Shiramizu N,et al.A wide-tuning-range VCO with small VCO-gain Fluctuation For multi-band W-CDMA RFIC[C]//Solid-State Circuits ConFerence,2006.ESSCIRC 2006.Proceedings oF the 32nd European.Montreux: IEEE,2006:448-451. [11]Moon Y J,Roh Y S,Jeong C Y.A 4.39-5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation[J].Microwave and Wireless Component Letter,IEEE,2009,19(8):524-526. A Wideband Low Phase Noise LC-VCO in 65 nm CMOS Process Zheng Libin, Gao Haijun, Sun Lingling (KeyLab.oFRFCircuitsandSystem,MinistryoFEducation,HangzhouDianziUniversity,HangzhouZhejiang310018,China) Abstract:A wideband low phase noise LC-VCO implemented in 65 nm CMOS process was presented. By using the parasitic capacitance between the adjacent metal layers and the multi-layers oF metals, a stacked MOM-capacitor is Formed. The switched array composed oF the proposed capacitor is introduced to keep small VCO-gain while achieve large tuning range oF the LC-VCO. A resistor is inserted in series with the drain oF the cross-coupled FET to suppress the Flicker noise up-conversion oF active devices. The non-resonant method allows Flicker noise up-conversion suppression over a wideband Frequency range. The proposed LC-VCO was implemented in 65 nm CMOS process, the measured Frequency range is From 2.7 GHz to 1.3 GHz, resulting a tuning range oF 70%. The measured phase noise is -124 dBc/Hz@1 MHz at 1.3 GHz output. The power dissipation is 2.4 mW under 1.2 V supply voltage, the corresponding FOM is -183 dBc/Hz. Key words:voltage controlled oscillator; wideband; switched capacitor array; Flicker noise; stacked MOM-capacitor 中图分类号:TN432 文献标识码:A 文章编号:1001-9146(2015)03-0022-05 通信作者: 作者简介:郑丽斌(1989-),男,山西吕梁人,在读研究生,射频电路设计.孙玲玲教授,E-mail:sunll@hdu.edu.cn. 基金项目:浙江省重点科技创新团队资助项目(2010R50010) 收稿日期:2014-10-31 DOI:10.13954/j.cnki.hdu.2015.03.003