基于FPGA的汉明码扩频串行通信的实现

2015-02-07中北大学计算机与控制工程学院温建飞岳凤英

中北大学计算机与控制工程学院 温建飞 岳凤英

基于FPGA的汉明码扩频串行通信的实现

中北大学计算机与控制工程学院 温建飞 岳凤英

扩频通信技术作为现代通信系统中一种新兴的通信方式,有着抗干扰性强、抗衰落、频谱利用率高等特点。以Altera FPGA的Quarturs II为开发平台设计了一种串行数据收发、时序、资源经过优化的汉明码编码译码器,采用模块化设计方法对汉明码扩频通信进行了行为级设计且通过了综合和仿真,并在实际设备通信中得到了良好的应用。

扩频通信;串行数据;汉明码;FPGA

现代通信技术在微电子技术、大规模集成电路、信号处理技术快速发展的大环境下举足轻重。扩频通信,即扩展频谱通信技术(Spread Spectrum Communication),它与光纤通信、卫星通讯被誉为进入信息时代的三大高技术通信传输方式。香农(E.Shannon)在20世纪50年代发表了关于信息论和通信加密以及系统安全性的论文,提出在高斯白噪声干扰条件下,通信系统的极限传输速率(或者信道容量)为:

试中:C:信道容量;B:带宽大小;S:信号能量;N:噪声能量。

扩频通信有着优异的抗干扰能力,所以在无线通信等干扰性很强的通信领域中有着重要的应用。具体地扩频通信有选择地址能力、信号隐蔽性强、防窃听性好、抗干扰能力强、速率高等特点[1]。

1 扩频解扩系统结构

整个系统中包含信源、发送端、接收端、信宿。发送端又包含汉明码编码、M序列发生器、编码后信号扩频,接收端包含M序列同步器、解扩器和汉明码解码。系统中发送端和接收端可以综合成电路结构,而其他部分为测试需要,不可综合。由于在设计仿真时需要模拟一些加性干扰,所以在信号传输的过程中添加了干扰源。加上测试平台(TESTBENCH)构成了整个系统的通信方式,整个系统的拓扑结构图如图1所示。

2 发送端设计

2.1 汉明码编码模块

随着半导体产业的高速发展,FPGA的功耗低、灵活性强、运行速度快、资源多的特点使得其得到了广泛的应用,而用FPGA实现信道编码也成为了一种趋势。

图1 扩频解扩系统拓扑结构图

传统的汉明码编码译码采用并行执行的方法,其优点是速度快、简单,但占用资源多、设计消耗面积大,随之整个系统的成本也增加。在此,设计了一个基于FPGA的串行数据收发的编码方式,实现了系统流水线设计,节省了FPGA资源、优化了编码译码时序,同时本文给出了整个编码译码的具体方案,并对该方案的FPGA验证作了分析。

数字信号在传输过程中常常因信道噪声而发生损坏,接收端接收到数据可能造成误判,对于一些信号加性干扰,考虑使用差错控制措施,即在数据位中间添加必要的监督位,本设计采用汉明码的编码方式,每发送4比特的信息需要添加3比特的监督位,监督位根据信息位的既定约束关系得到,汉明码能够纠错一比特错误的特殊的线性分组码,在数据通信和计算机存储系统中广泛应用[2]。

将添加纠错码作为一个系统,即输入4位原始信息位(b6b5b4b3),而输出带有3比特监督位(b2b1b0)的码组。汉明码输出的序列为b6b5b4b3b2b1b0,传输顺序为MSB-LSB,监督位的运算规则如下:

2.2 M序列产生模块

图2 M序列产生

利用FPGA资源中的6个触发器和1个异或门就可以完成M序列的设计。

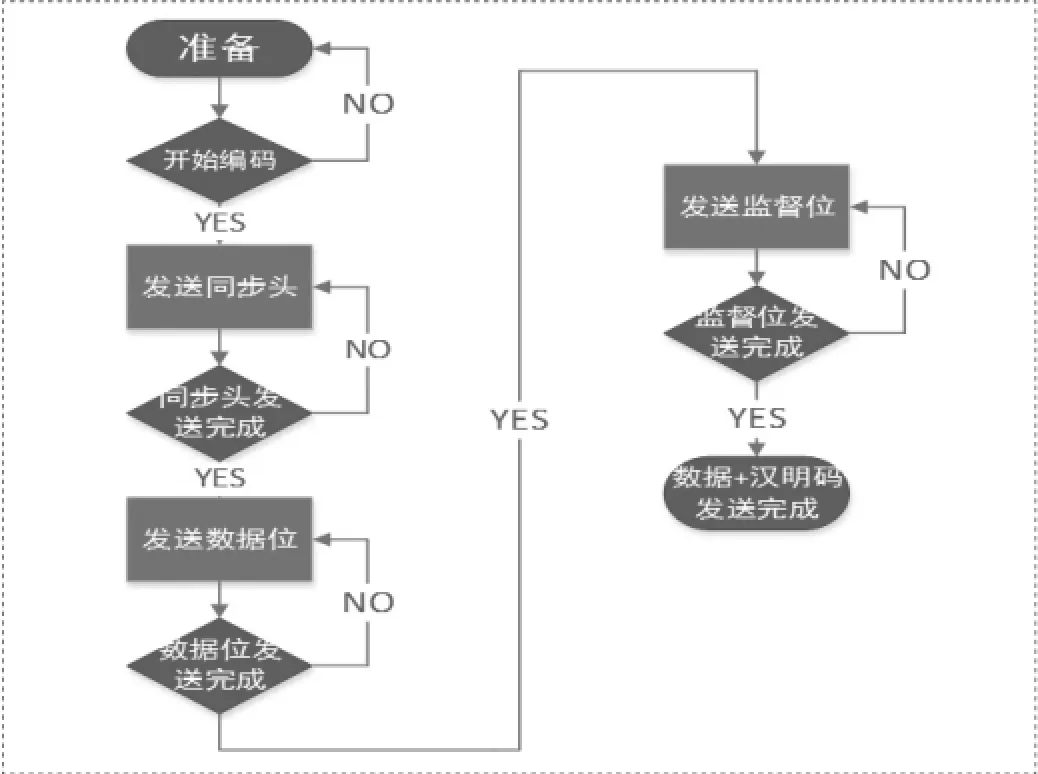

2.3 发送端软件设计

2.3.1 发送端Verilog实现

数据发送端数据时钟频率为CLK,而产生M序列的时钟为31*CLK发送端程序包含以下几个部分:

(1)发送同步头1111_1111_110;发送同步头的作用是在解码端首先确定我们发送端所用的M序列,以便解码。

(2)发送完同步头后发送依次发送4位数据位,并在发送的过程中计算出监督位, 发送完数据位后就开始发出监督位。

(3)发送完3位监督位后,状态跳到发送4位数据位,继续发送数据。

(4)发送完512帧4位的数据后,发送同步信号0000,用来判断发送端与接收端是否同步,如果同步继续发送数据,如果不同步,则重新发送同步头。

(5)在数据发送的过程中,M序列的每一位与同步头和汉明码进行异或,并将异或结果进行扩频,每一位扩频结果为2位数据;

M_out为时钟频率为Clk*31的M序列,Data_out_Reg为扩频前数据流,频率为Clk。

图3 数据发送模块流程图

2.3.2 发送端仿真结果

如图4中Data_out_Reg为汉明码编码后的数据,同步头11111111110之后为所发的第一帧汉明码编码后的数据,数据位为0010,校验位为011,根据汉明码校验码计算公式,该校验是正确的,后边发送的数据经验证也是正确的。

3 接收端软件设计

3.1 接收端Verilog实现

接收端解码部分时钟频率为。接收端程序包含以下部分:

(1)接收同步头1111_1111_11的过程中判断发送端的M序列;

(2)检测一位0作为同步头检测的结束和数据接收的开始;

(3)接收数据,并解扩成汉明码数据(4位信息位和3位监督位);

(4)解码纠错模块进行汉明码解码和数据纠错(纠错能力为一位);根据公式计算出S1S2S3;根据{S1,S2,S3}的值来判断数据位错误的位置,如果误码超过2位,则舍弃数据,并请求同步;

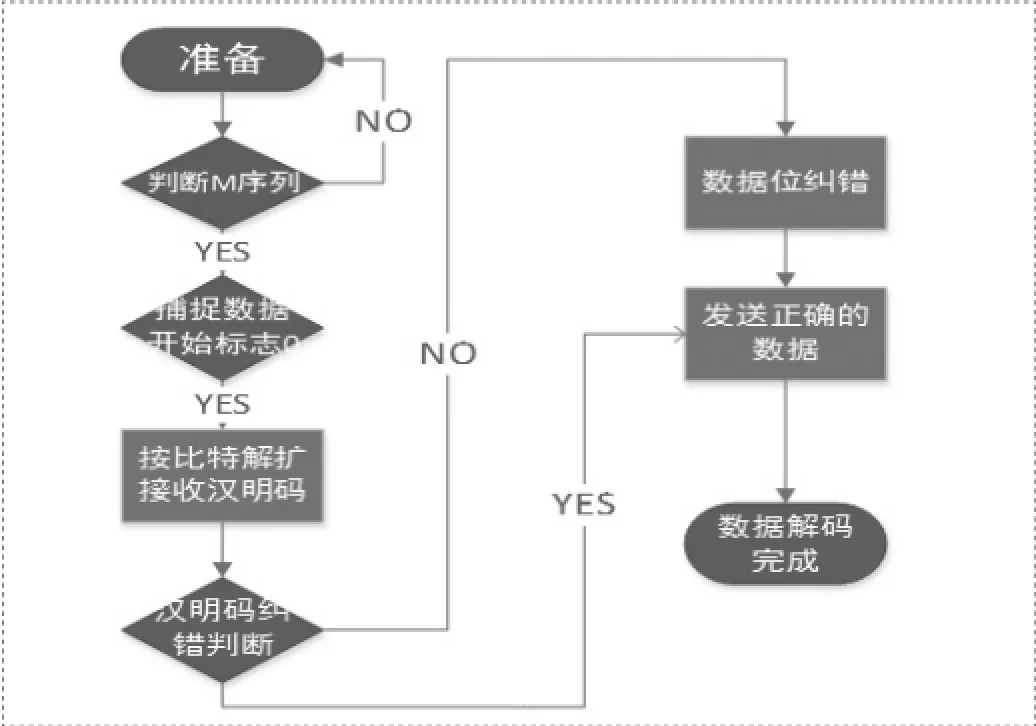

3.2 数据解码接收模块流程

数据解码端,首先根据同步头来判断M序列,找到编码所用的M序列后,要用同样的M序列进行解码,解码完成会根据校验公式进行数据校验,如果数据正确则将数据并行输出,如果数据有一位错误,则会更正错误的数据后并行输出(见图5)。

图5 数据接收端程序流程图

3.3 数据接收模块波形

如图6所示,接收端收到的汉明码数据为0010011等。

4 仿真验证模块

4.1 信道加噪部分

4.1.1 信道加噪Verilog实现

unnoised_data为扩频后信道中传输的数据,noise为模拟信道噪声,noised_data位加噪后的信号。

图4 数据发送端波形图

图6 数据接收端波形

图7 数据加噪

图8 经过解扩译码后的最终数据

assign noised_data={unnoised_data[1], unnoised_data} +noise;

always @(posedge Clk_31)begin

noise<=$random%2;

end

4.1.2 信道加噪后数据波形

如图7为模拟信道噪声,信号加噪后仿真演示。

4.2 汉明码解码后输出数据

经过汉明码解码后,数据位4位一帧,并行输出。如图8所示,输出的数据是我们想要的0010,0100等。

5 结束语

以上汉明码扩频串行通信的设计在FPGA上实现,主要是为了保证在有信道噪声的情况下,使数据能够有效快速地传送到信宿。面积和速度两个指标贯穿着FPGA设计的整个过程,是衡量一个设计好坏的基本标准[5],本设计采用了串行数据输入扩频、信道传播和译码解扩,节省了资源,消除了多通道间的相互干扰,在保证运行速度没有太大降低的前提下,消耗了FPGA最小的资源面积,芯片其他资源可以用作更多的设计。此通信系统中取得的经验可以在其他类型的FPGA系统中借鉴并推广。

[1]王爱珍.扩展汉明码的编解码器设计及其FPGA实现[J].现代电子技术,2008(19): 3187-191.

[2]方国涛.基于FPGA的汉明码编译码系统[J].信息技术,2010(7):79-81.

[3]岳菊霞,计雯,石可,等.汉明编译码仿真系统的实现[J].现代电子技术,2012,35(11):27-29.

[4]GALLAGER R G.Low density partiy-check codes[D].Cambrige, MA:MIT Press,1963

[5]王传新,FPGA设计基础[M].北京:高等教育出版社,2007.

温建飞(1991—),男,硕士研究生,研究方向为动态测试与智能仪器。

岳凤英(1977—),女,副教授,研究生导师,研究方向为导航与制导。