高可靠性的闪存字线驱动电路设计

2015-01-24张其笑胡玉青张炎峰

姜 伟,张其笑,胡玉青,张炎峰

(苏州大学 城市轨道交通学院,江苏 苏州 215000)

闪速存储器(Flash memory),简称闪存,是目前最先进的存储技术。目前,单块集成电路芯片上可以集成容量为几十GB的闪存,存储单元的面积已经减小到0.0025μm2,工艺节点也已下降到25 nm[1]。闪存具有的非易失、抗震和低功耗等特性使其广泛应用于各种存储系统中[2](手机、音乐播放器、相机等)。闪存的基本存储单元为一个堆叠栅晶体管,包括用于存储电荷的浮栅(floating gate)以及用于连接字线的控制栅(control gate),通过字线给控制栅施加一定的电压就可以对每个存储单元进行编程、擦除或读取。在对闪存进行编程和擦除的过程中常常需要用到高压,而字线驱动电路的作用就是要确保高电压能够正确地施加到存储单元的控制栅上。随着晶体管尺寸越来越小以及高电压对晶体管性能的退化作用,字线驱动电路将面临严峻的可靠性问题。本文分析了传统电平转换电路中存在的不足,提出了一种高可靠性的能够同时驱动正负高压的字线驱动电路,解决了传统结构中存在的电压竞争问题,同时提升了电路的带负载能力。

1 存储单元结构和擦写机制

闪存存储单元如图1所示,包括两个栅极:最上面是控制栅,用于施加适当的工作电压;内部是浮栅,用于存储电荷。通过电子注入浮栅,改变存储单元阈值电压来实现0/1的存储。阈值电压的变化可以用一个简单的等式来说明[3]:

其中,VT0是浮栅中没有电子时的阈值电压,Q是浮栅中总的电荷量,CFC是浮栅与控制栅之间的耦合电容。这样,存储单元就可以形成两种不同的逻辑状态,通过施加合适的读取电压Vread就可以被灵敏放大器准确地读出存储信息。

用于改变浮栅中的电荷的物理机制通常有以下两种:热电子注入(HCI)和Fowler-Nordheim隧穿[4]。擦除操作是在特定的电压偏置条件下将电子注入浮栅,需要注意的是,擦除操作是在同一个扇区上的所有存储单元中同时进行,而不是对特定的存储单元进行擦除。擦除完成后,存储单元的阈值电压升高。例如,通过FN隧穿效应进行擦除时,在控制栅上施加正高压,漏极接地,源极浮置。编程操作是在特定的电压偏置条件下使电荷脱离浮栅。例如,使用FN隧穿效应进行编程时,施加与擦除操作极性相反的电压:在控制栅上施加负高压。编程完成后,存储单元的阈值电压降低。两个阈值电压之间的差值称为阈值电压窗口。

图1 闪存存储单元与其转移特性曲线Fig.1 Flash memory cell and its transfer characteristic curve

2 字线驱动电路设计分析

通常,在编程和擦除时需要在字线上分别施加负高压和正高压,这就需要进行低电压与高电压之间的转换。实现这种功能的典型电路被称为电平转换电路。对于闪存电路来说,连接字线的电平转换电路就称为字线驱动电路[5]。

2.1 传统电平转换电路分析

传统的电平转换电路如图2所示,包括一个用于提供互补输入信号的反向器INV,两个交叉耦合的PMOS管MP1和MP2以及两个NMOS管MN1和MN2。电平转换电路的工作方式如下所述:当输入端IN输入低电平vss时,通过反相器INV后,晶体管MN2的栅极为电源电压vdd,晶体管MN2导通,输出端OUT被拉到低电平vss,使得晶体管MP1也导通。从而晶体管MP2的栅极电压(OUTb)被上拉到正高压vpp,致使晶体管MP2关断。因此,输出端OUT输出低电平vss。同理,当输入端IN输入高电平vdd时,OUTb端输出低电平vss,而OUT端输出正高压vpp。

图2 传统的电平转换电路Fig.2 The conventional level shifter

输入端IN由低电平vss翻转到高电平vdd的过程中,有一小段时间晶体管MP1与晶体管MN1是同时打开的,这时,输出端OUTb的电压是由MP1与MN1的导通电阻决定的[6]。因此,考虑到工艺偏差,必须精确设计MOS管的宽长比,减小PMOS管的尺寸保证导通电阻足够大,否则电路可能无法正常工作,影响电路可靠性。但如果PMOS管尺寸过小,又会导致对后级电路的驱动能力下降。所以,传统的电平转换电路存在着可靠性和驱动能力的权衡问题。

2.2 新型字线驱动电路设计

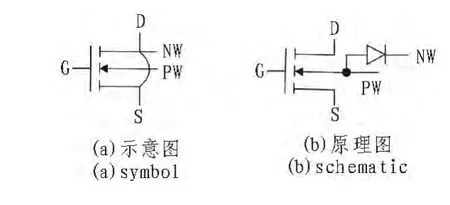

对闪存进行编程或擦除时,分别会用到负高压或正高压,传统的电平转换电路只能提供正压之间的切换功能。针对闪存电路的特殊性以及传统电平转换电路中存在的严峻的可靠性问题,本文提出了一种能够同时转换正高压与负高压的高可靠性的字线驱动电路,如图3所示。其中,MP1和MP2是高压PMOS管;MN1-MN4为三阱工艺的NMOS管,如图4所示,用于引入负压;CL是负载电容。VPPWL与VNNWL可以是电荷泵电路的输出电压,也可以是来自外部输入的正负高压。VWELL是n阱电压,AD是地址信号而ERASE是擦除/编程控制信号。

图3 改进的字线驱动电路Fig.3 The improved word line driver circuit

图4 三阱工艺NMOS管Fig.4 Triple-well NMOS

对闪存进行编程时,控制信号ERASE为低电平vss,n阱偏置VWELL接高电平vdd,正高压输入端VPPWL接高电平vdd,负高压输入端VNNWL首先接低电平vss,地址信号AD变为高电平vdd选中对应字线;反向器I2输出高电平vdd,使得MP2关断;由于ERASE接低电平,所以MP1开启,使得节点SGB(MN4的栅极)维持在高电平,致使MN4导通,输出端OUT(MN3的栅极)首先通过MN4被拉低到低电平vss;随后VNNWL接入编程所需的负高压vnn,输出端OUT通过MN4就被充电到负高压vnn用于编程操作。MN1与MN2起到稳定MN4栅极电压的作用,地址信号选定后,MN1与MN2的栅极都为低电平vss,同时关断,这样MN4的栅极就能被稳定在高电平vdd,而MN3的栅极OUT通过MN4放电到低电平vss,当负高压vnn到来时,OUT端迅速拉低,使得MN3管维持关断状态。MN1与MN2有效隔离了SGB节点(MN4的栅极)与下拉通路,解决了在负高压vnn到来后MN3与MN4的漏极电压竞争问题,提高了电路可靠性。另外,通过合理设计MN4管的尺寸,能够有效提升电路带负载能力。

对闪存进行擦除时,控制信号ERASE为高电平vdd,负高压输入端VNNWL接低电平vss,n阱偏置VWELL接正高压vpp,正高压输入端VPPWL接正高压vpp。通常闪存都是同一扇区一起擦除,所以同一扇区内地址信号都为高电平vdd,此时反向器I2也输出高电平vdd,使得MP2导通,OUT输出正高压vpp用于擦除操作。为了提高电路的带负载能力,必须加大MN4管的尺寸,这时就存在一个可观的栅漏耦合电容,MN4的栅极电压会被拉高,使MN4导通,OUT端输出的正高压vpp就会泄露并造成很大的漏电流。这里的解决措施是通过MN2和MN3的下拉通路对SGB节点(MN4的栅极)放电到低电平vss,使MN4保持关断状态,输出端OUT输出稳定的正高压vpp,提高了电路可靠性。

3 电路仿真结果分析

本设计基于SMIC 0.18μm浮栅工艺,正常工作电压vdd为1.8 V,低电平 vss为 0 V,负高压 vnn为-7 V,正高压 vpp为+7 V。地址信号的上升时间和下降时间都为0.1 ns,为了模拟真实编程/擦除周期时正负高压的施加情形,规定正负高压的建立时间为10 ns,用Hspice对图3所示电路进行仿真。晶体管尺寸如表1所示。

表1 晶体管尺寸Tab.1 The size of transistors

图5为编程状态下各电压波形图,其中负载电容为1 pF。如图所示,OUT端电压随着vnn的下降而降低,最终稳定在编程所需的-7 V电压。擦除电压波形跟编程电压波形只是最终输出电压OUT的极性不同,为+7 V,在此就不再累述。表2为编程状态下字线驱动电路的带负载能力[7-8],从表中可以看出,本设计具有较强的负载驱动能力,驱动3 pF的大负载时,传输延时也只有1.919 ns,相对于μs级的编程周期来说,可以忽略不计。

图5 编程状态下字线驱动电路电压波形图Fig.5 Waveforms for word line driver during program state

4 结 论

文中基于SMIC 0.18μm浮栅工艺提出了一种新型字线驱动电路,适用于闪存,其主要特点是采用隔离稳压技术,同时具备转换正高压和负高压的功能。电路仿真结果表明,该电路克服了电平转换电路中普通存在的电压竞争问题,工作时稳定可靠,并且具有较强的负载驱动能力。

表2 字线驱动电路的带负载能力Tab.2 The ability of d riving capacitive loads for the p roposed word line driver

[1]Pellizzer F,Bez R.Non-Volatile Semiconductor Memories for Nano-Scale Technology[C]//Nanotechnology(IEEE-NANO),2010 10th IEEE Conference on, Seoul, Korea,2010:21-24.

[2]Chang Y H,Huang PC,Hsu PH,et al.Reliability Enhancement of Flash-Memory Storage Systems:An Efficient Version-Based Design[J].Computers, IEEE Transactions on,2013,62(12):2503-2515.

[3]Ielmimi D,Spinelli S,Lacaita L.Recent developments on Flash memory reliability[J].Microelectronic Engineering,2005(80):321-328.

[4]Pavan P,Bez R,Olivo P,et al.Flash Memory Cells-An Overview[J].Proceedingsof the IEEE,1997,85(8):1248-1271.

[5]Ginez O,Portal J M,Aziza H.Reliability Issues in Flash Memories:An On-Line Diagnosis and Repair Scheme for Word Line Drivers [C]//Proceedings of the 14th IEEE IMS3TW,Vancouver,Canada,2008:1-6.

[6]Chow H C,Hsu C S.New Voltage Level Shifting Circuits for Low Power CMOS Interface Applications[C]//The 47th IEEE Midwest Symposium on Circuits and Systems, Berlin,Heidelberg,2004(1):533-536.

[7]刘磊.基于Msp430单片机的直流电子负载设计[J].电子科技,2013(2):25-27.LIU Lei.Design of DC electronic load based on Msp430 microcontroller[J].Electronic Science and Technology,2013(2):25-27.

[8]林臻,燕雪峰.一种面向负载平衡的主动复制技术[J].电子科技,2012(4):37-40.LIN Zhen,YAN Xue-feng.An active replication technology for load balancing[J].Electronic Science and Technology,2012(4):37-40.