基于Cyclon4的DVI/HDMI高清视频转换器

2015-01-15刘媛媛冯宏伟

刘媛媛 冯宏伟

(1.无锡科技职业学院机电学院,江苏 无锡 214028;2.江南大学,江苏 无锡 214122;3.无锡格林通安全装备有限公司,江苏 无锡 214073)

目前,常见的数字视频接口方式有LVDS、DVI及HDMI等。LVDS是一种低压差分信号接口,其支持速率仅有230Mbit/s(即SXGA分辨率);而且,LVDS视频接口无法提供内容保护机制。因此,LVDS视频接口主要应用在便携系统的小尺寸显示器上,不适用于大尺寸高分辨率的桌面显示器。

相对于LVDS,DVI/HDMI视频接口可达到UXGA分辨率,高于高清电视所需分辨率。同时,DVI可由HDCP实现内容保护功能,而HDMI自身包含HDCP内核。因此,DVI/HDMI视频接口已广泛应用于DVD播放器、有线/卫星电视机顶盒及高清电视等设备[1]。

笔者针对LVDS数字视频信号传输速率和分辨率不高的问题,以Cyclon4系列EP4CE40的FPGA为主控器件,结合DVI/HDMI的视频编码芯片TFP410PAP和AD9889B,设计LVDS到DVI/HDMI的高清视频转换器。

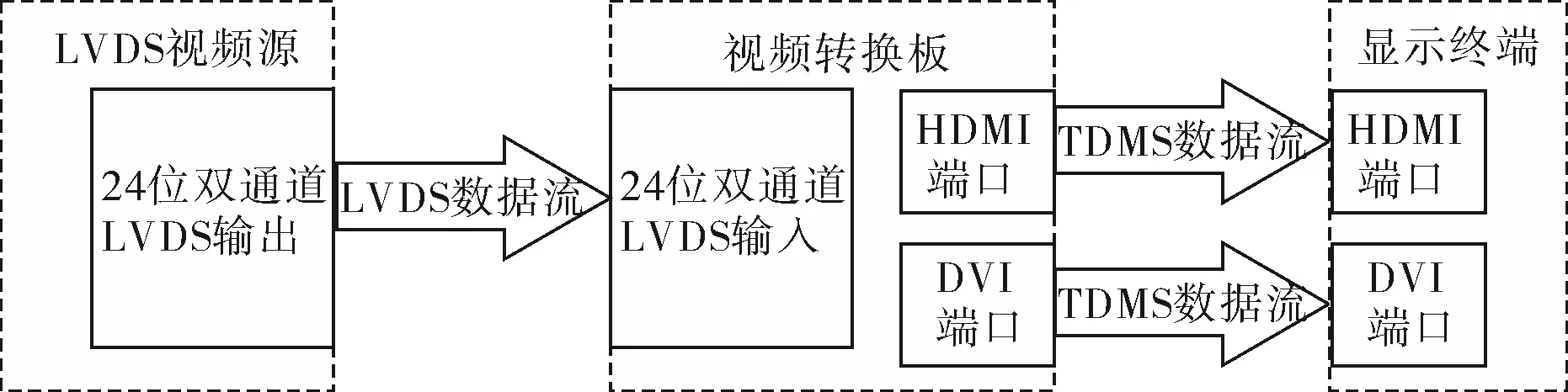

高清视频转换器整体方案如图1所示。该视频转换器以24位双通道LVDS信号作为待转视频源,采用双路方式传输,奇数路和偶数路数据各24位(即RGB数据共计48位),每个RGB基色信号为8位数据。

图1 高清视频转换器整体方案

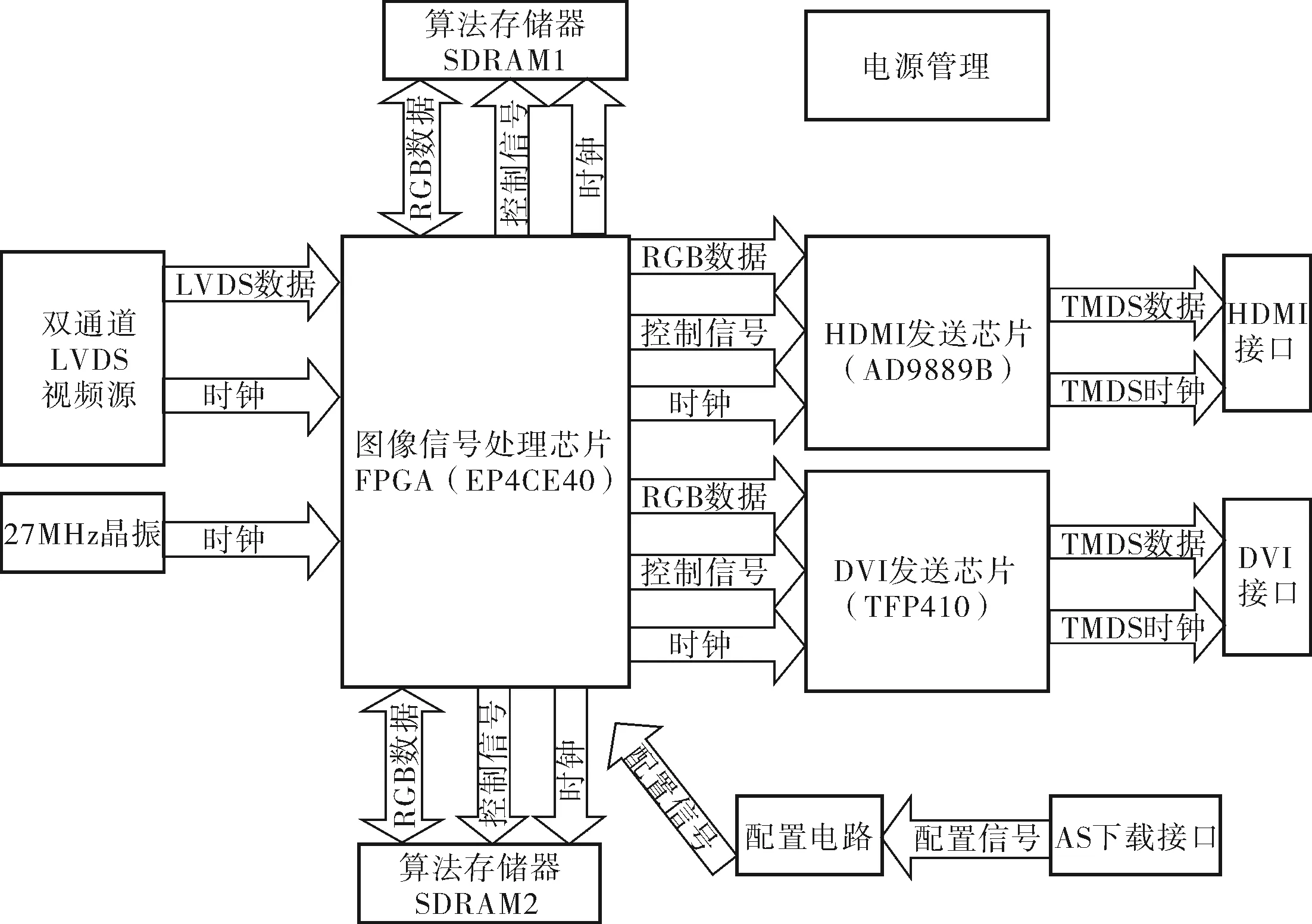

该视频转换器是以FPGA为主控芯片的硬件电路。FPGA内部的LVDS接收器实现对24位双通道LVDS低压差分信号的接收,然后把解码出来的并行图像数据按照对应关系将每个像素的色彩值解析到RGB空间,实现色彩空间的转换,并将每个像素转换后的RGB值存储在SDRAM中,依照视频输出所要求的分辨率,再从SDRAM中读取像素的RGB值,并将RGB值转换为TMDS的码元串行序列。由于TMDS链路是串行信息编码,根据TMDS链路的编码规则,链路上的码元传输率高达1Gbit/s,因此必须使用TMDS专用的发送芯片发送TMDS数据流,即像素的RGB值由FPGA从SDRAM中读取出来,依据标准VGA时序发送到TMDS专用发送芯片,然后经该芯片完成对每个像素RGB值的编码和并行到串行的转换,再将其发送到TMDS链路,最终提供给DVI/HDMI视频端口显示[2]。

2 硬件电路

视频转换器的硬件结构如图2所示。24位双通道LVDS信号通过输入接口送入FPGA主控芯片,FPGA主控芯片对该信号使用内部锁相环模块按1∶7的比率进行频率提升,并用串并转换器模块对其进行串并转换。当输入LVDS信号与标准LVDS视频信号校对相符且都有效时开始接收数据,在时钟对位后开始采集LVDS信号,并通过串并转换成两组24位RGB数据。

图2 视频转换器的硬件结构

2.1 FPGA芯片选型

考虑到DVI/HDMI的图像分辨率较高,必须保证TMDS发送芯片与FPGA之间的传输带宽在100MHz以上,因此FPGA的运行速率要足够快。同时因FPGA和外围设备之间的交互比较多,所以要求FPGA有足够多的引脚。由于采用的晶体振荡器的时钟频率为27MHz,无法满足传输速率所要求的100MHz以上,因此需要FPGA内部带有锁相环。此外,为满足转换器的脱机工作,需要保证FPGA具备配置芯片。另外,考虑到转换器的占用面积和版本升级,要求FPGA具有足够丰富的内部资源。

综合考虑,最终选用Cyclon4系列型号为EP4CE40的FPGA。该FPGA具有高速LVDS I/O端口,其运行速率可达640Mbit/s,低速LVDS I/O端口的运行速率也有311Mbit/s;共有484个引脚,其中包括328个可用引脚;4个锁相环;支持串行配置芯片;逻辑单元有39 600个;存储空间为1 161 216bit[3],完全满足视频转换器对FPGA的要求。该FPGA还具有滤波器、颜色空间转换及图像编码器等成熟的IP内核,相比于纯软件的串行工作方式,该FPGA硬件的流水线和并行工作方式在速度上有很大优势。同时,采用该FPGA作为主控器件,可极大地提高视频转换器的灵活性,不仅可以实现数字信号的转换,还可以利用FPGA的可配置性轻松实现在线升级和维护,能够极大地提升视频转换器的实用价值[4,5]。

2.2 DVI/HDMI解码发送芯片外围电路

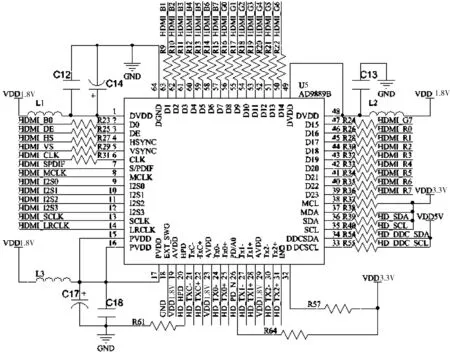

HDMI发送芯片采用高清多媒体HDMI1.3接口发送芯片AD9889B。AD9889B支持像素带宽在25~165MPixel/s的TMDS链路,支持高达1 080p的高清电视格式和高达UXGA分辨率(1 600×1 200,60Hz)的图像。该芯片具备HDCP支持功能,可实现对HDCP1.2协议所规定的受保护内容的传输。另外,其外围配置电路较少,设计灵活性较高,通过配置引脚连接到FPGA,即可完成在不同工作方式下的多种配置。AD9889B的外围电路如图3所示。

图3 HDMI发送芯片AD9889B的外围电路

DVI发送芯片采用可兼容DVI1.0规范的视频编码芯片TFP410PAP。与发送芯片AD9889B一样,TFP410PAP支持像素带宽在25~165MPixel/s的TMDS链路。通过接收FPGA发送的24位并行视频数据、时钟和控制信号,TFP410PAP内部的TMDS模块将其转换成3路RGB数据信号和一路时钟信号。TFP410PAP具有状态引脚配置和I2C总线配置,其外围电路如图4所示。

3 FPGA功能

3.1 LVDS信号的RGB解析

根据VSEA标准的数据时序(图5),输入处理模块在检测到HSYNC同步信号后开始计数,并开始计算Backporch的长度,由于每种图像格式的Backporch长度是确定的,计算得到Backporch的值也就可以确定输入视频的格式。在Backporch计数后,便可以得到一帧视频的有效像素,此时处理模块会将有效数据存入缓存[6]。

传入FPGA的LVDS视频信号是一对4组7位信号,信号要在SDRAM中缓存,然后再对其进行数据读取。在内部频率进行倍频后,在串并转换器的作用下,将解串器所接收的重复串行模式的每种组合传送至FPGA内部,来读取LVDS视频信号。从两组28位信号中依次读取像素时钟信号、行场同步信号、数据使能信号和两组24bit的RGB数据信号,完成对LVDS信号的RGB解析。

3.2 SDRAM的读写控制

SDRAM读写控制模块负责在系统上电时初始化SDRAM。待SDRAM初始化后,控制模块再接收外围模块的控制信号,并根据信号向SDRAM发出相应的读写操作命令,保证数据的正确写入、读出和SDRAM的刷新。

图4 DVI发送芯片TFP410PAP的外围电路

图5 VSEA标准的数据时序

首先将LVDS信号经过串并转换后的第一帧图像的奇数场数字视频信号数据依次存入SDRAM1中,如图6中的W1,同时FPGA通过算法的控制,对输入的每行数字信号进行复制,此时SDRAM2处于视频输出状态R1。若SDRAM2中无数据,输出状态表示等待,同时也不进行数据写入。然后,当奇数场数据写入SDRAM1完成时,控制切换到对SDRAM1的数据进行读取,即图6中的R2状态;接着将偶数场数据写入SDRAM2中,即图6中的W2,在偶数行视频数据输入的同时对数据进行复制,使偶数场转换为一帧完整的图像。依此类推,通过这种“乒乓操作”的方式使SDRAM1和SDRAM2分别工作在读与写的状态,并通过FPGA对视频数据进行复制处理,从而确保视频场数据为逐行的帧数据。

图6 双SDRAM读写控制示意图

3.3 DVI/HDMI解码芯片的TGMS信号发送

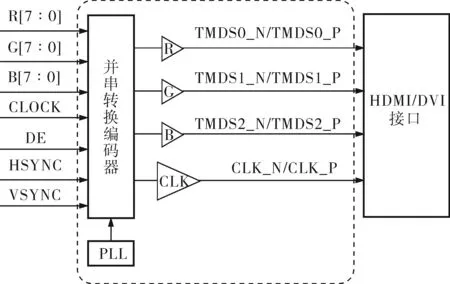

DVI/HDMI发送模块分别根据DVI/HDMI行同步信号的时序,向SDRAM控制器发出读入RGB像素信号请求,通过“乒乓操作”读写的控制,两个SDRAM中存储的RGB值交替向DVI/HDMI发送模块输出[7]。发送模块发送的RGB数据,一路送DVI发送芯片TFP410PAP并转换为TMDS信号输出,另一路送HDMI发送芯片AD9889B并转换为TMDS信号输出。TMDS数据链路的结构如图7所示。

图7 TMDS数据链路结构

在TMDS数据链路结构中,FPGA将R、G、B共3组各8位的视频数据、时钟和控制信号传送给包含3个独立编码器的TMDS发送芯片,每个编码器负责对一组视频数据进行编码。10bit编码后的码元从并行数据转换到串行数据,然后按最低位到最高位的顺序被发送到TMDS链路上,从而保证视频数据、时钟和控制信号可同步发送给显示终端。

4 结束语

Cyclon4系列EP4CE40的FPGA作为DVI/HDMI高清视频转换器的主控器件,承担LVDS视频数据流的解析、色彩空间转换、存储器的读写控制及DVI/HDMI发送芯片的控制等多种任务,提高了系统的集成度。笔者提出的视频转换器DVI/HDMI视频接口可达UXGA分辨率,高于高清电视所需分辨率,确保了高清信号的输出。另外,视频转换器接口采用信号差分对传输,发送和接收数据都为压差信号,传输线缆的长度对信号影响较小,具备远距离传输及抗干扰能力强等优点,具有较高的实用价值。

[1] 张彦梅,柴芳娇.基于FPGA的高速图像采集系统[J].北京理工大学学报,2010,30(9):1117~1120.

[2] 向守坤,黄启俊,江冠群,等.基于FPGA的ITU-R BT.656数字视频转换接口系统[J].电子测量技术,2009,32(4):113~117.

[3] 赵东方,李雄,于心亮,等.基于FPGA的数字视频转换接口的设计与实现[J].电子产品世界,2007,(10):160~161.

[4] 何振琦,李光明,张慧琳,等.高速图像采集系统的研究及FPGA实现[J].计算机应用,2010,30(11):3094~3096.

[5] 梁义涛,唐垚,史卫亚,等.基于Cyclone IV的Camera Link-HDMI高清视频转换器设计[J].电子技术应用,2013,39(5):12~14.

[6] 卿启新.基于FPGA的LVDS视频信号转换系统设计实现[D].广州:华南理工大学,2011.

[7] 刘翠萍.长线传输中数字视频格式转换接口的设计[D].哈尔滨:哈尔滨理工大学,2009.