基于柔性PI基底的氧化物IGZO TFT器件工艺及特性研究

2015-01-06陈龙龙张建华李喜峰石继锋

陈龙龙,张建华,李喜峰∗,石继锋,孙 翔

(上海大学新型显示技术及应用集成教育部重点实验室,上海 200072)

基于柔性PI基底的氧化物IGZO TFT器件工艺及特性研究

陈龙龙,张建华,李喜峰∗,石继锋,孙 翔

(上海大学新型显示技术及应用集成教育部重点实验室,上海 200072)

讨论了基于柔性PI基底上的底栅型TFT器件工艺,通过工艺优化解决了双层结构干刻速率不同造成的下切角形状。本文TFT器件是基于氧化物IGZO为有源层,栅绝缘层采用Si3N4/SiO2双层结构,采用两次补偿曝光、干刻方式消除干刻引入的下切角形状,有效解决了薄膜沉积引入的断线风险。实验结果表明,经过SEM断面观察,干刻后双层结构taper角度适合TFT器件后续沉膜条件,柔性基底上制作的TFT器件迁移率达到14.8 cm2/(V·s),阈值电压Vth约0.5 V,亚域值摆幅SS约0.5 V/decade,TFT器件的开关比Ion/Ioff>106。通过此方法制作出的器件性能良好,满足LCD、OLED或电子纸的驱动要求。

柔性;薄膜晶体管;铟镓锌氧化物;迁移率

1 引 言

随着AMOLED显示技术的快速发展, AMOLED显示技术相较于AMLCD显示技术,表现出更加优秀的显示特性,如响应速度更快、更加轻薄、颜色更鲜亮等[1-3]。玻璃基板是最常用于AMOLED及AMLCD显示屏制造的基板,其具有表面平整度高、透明、材料性能稳定等优点。同时,柔性显示技术将是未来显示技术发展的重要方向,但由于玻璃基板硬度较大,不能满足柔性显示屏基底可挠曲的要求,因此柔性基底的需求被着重提出。目前柔性显示研发所使用的基底较多采用塑料、金属薄膜、超薄玻璃、聚酰亚胺(PI)等材料,可制造出较传统基底更轻薄、可弯屈的柔性显示屏[4-6]。同时,为了实现柔性显示技术,柔性显示技术的开发希望直接与传统基于玻璃基板的工艺制程相兼容,直接使用传统AMOLED显示技术工艺设备及工艺制程,只需对部分工艺流程进行低温工艺优化。目前AMOLED显示技术不断发展,TFT背板有源层驱动材料技术不断进步,基于IGZO氧化物半导体的TFT器件因其迁移率高(10 cm2/(V·s))、制备工艺温度低、受可见光影响小和可以制作成透明器件等优点而备受关注[7-11],所以基于IGZO氧化物TFT技术是AMOLED显示技术尤其是柔性显示技术的优选方案之一。在本文中我们将讨论基于IGZO氧化物的AMOLED柔性基底显示屏TFT基板的制造工艺,柔性基底选用PI基底,提出优化的柔性基板上的IGZO氧化物TFT基板制造工艺;并通过优化栅绝缘层工艺以及干法刻蚀工艺,从而制造出良好的TFT器件性能。

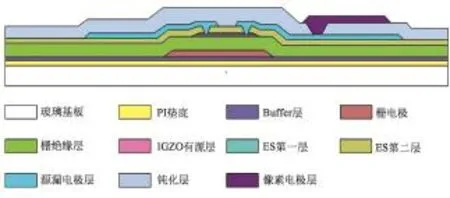

图1 柔性PI基底TFT器件结构示意图Fig.1 Schematic diagram of the flexible PI substrate TFT device structure

2 样品制备

本文所提及的柔性基板TFT器件结构示意图如图1所示。PI层的厚度为15μm,PI层制备首先利用旋涂机将PI材料旋涂在200 mm×200 mm×0.7 mm的玻璃基板上,然后在220℃下高温固化60 min,形成带有PI膜层的柔性基底;利用此方式形成的柔性PI基底上的TFT工艺制程可以兼容现有玻璃基板上TFT工艺制程,在整套TFT工艺制程结束之后,采用激光剥离等方式将PI柔性基底与玻璃基板剥离。本文研究了PI柔性基底上TFT器件性能,PI柔性基底未从玻璃基板上剥离。TFT工艺制程之前,为了保证TFT器件材料的粘附性以及制作好的TFT器件对空气环境水、氧的隔离效果,我们在PI柔性基底上生长Buffer层来达到上述目的;Buffer层采用双层结构,利用ULVAC CME-200E型PECVD连续生长厚度分别为150 nm的Si3N4层、厚度为150 nm的SiO2层,薄膜沉积工艺温度为150℃。接着利用ULVAC SME-200E型磁控溅射机在Buffer层之上溅射厚度为100 nm的钼金属、50 nm的ITO复合层作为栅电极层材料,通过光刻等工艺形成栅电极图形;由于钼金属材料与绝缘层在干法刻蚀中的刻蚀选择比较小(~1∶3),干法刻蚀气氛会损失钼电极层金属甚至于将钼电极刻蚀殆尽,为了解决干刻对栅电极层金属的影响,我们用生长ITO膜层作阻挡层的方法来解决如上问题:ITO膜层几乎不受干刻工艺的影响,后续源漏电极层同样采用此工艺及膜层结构。接着利用PECVD沉积栅绝缘层并采用双层结构,分别连续沉积厚度为250 nm的Si3N4层、厚度为50 nm的SiO2层。之后再利用磁控溅射设备在常温下溅射IGZO膜层,溅射功率设定300 W,Ar与O2流量比值为50∶5 SCCM,膜层厚度为50 nm;为了保护IGZO膜层免受到水、氧以及工艺中酸刻蚀液等的影响,在IGZO膜层溅射之后先用PECVD在150℃下先沉积一层厚度为50 nm的SiO2层作为刻蚀阻挡层ES第一层,通过光刻工艺制作出有源层岛结构光刻胶图形,先通过干刻工艺刻蚀去除掉岛结构之外的SiO2层,再用草酸刻蚀IGZO膜层,形成有源层结构。接着利用PECVD沉积一层厚度为150 nm的SiO2层作为刻蚀阻挡层ES第二层,通过干法刻蚀露出有源层,形成下一步源漏电极层的电极接触孔。接着用磁控溅射设备沉积双层源漏金属电极层,生长膜层结构与工艺条件、各膜层厚度都与栅金属层相同,对其光刻、湿法刻蚀形成源漏电极图形。下一步再用PECVD沉积一层厚度为200 nm的SiO2膜作为TFT器件的钝化层,沉膜完成之后进行光刻以及干法刻蚀工艺,制作形成接触孔图形。最后一步使用磁控溅射设备沉积一层ITO膜层作为像素电极层。为了使器件性能更加稳定,我们将基板在250℃大气氛围下退火2 h,之后对TFT器件性能作测试。

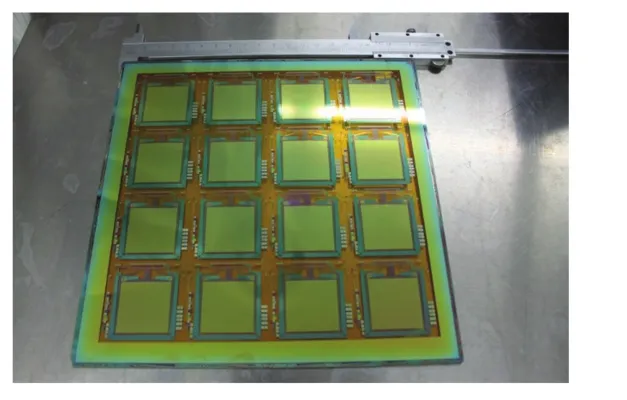

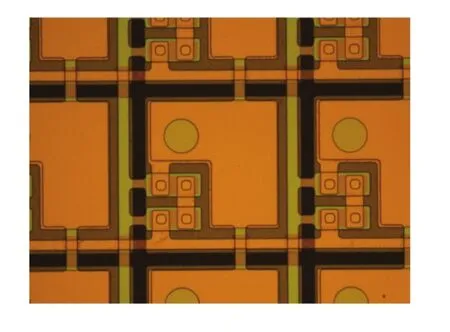

制作完成的柔性基板如图2所示,文中基板流片曝光工艺利用上海大学与上海微电子装备有限公司(SMEE)合作研发的AMOLED投影曝光机,曝光视场为44 mm×44 mm,每片柔性PI基底之上通过stepper投影曝光方式可同时制造16片显示屏,制作完成的像素区域图形如图3所示。

图2 柔性TFT基板流片工艺完成后图片Fig.2 Flexible substrate of TFT device after the fabricated process

图3 像素区光学显微镜图形Fig.3 OM picture of the pixels

3 实验结果与讨论

3.1 钝化层及栅绝缘层干刻工艺讨论

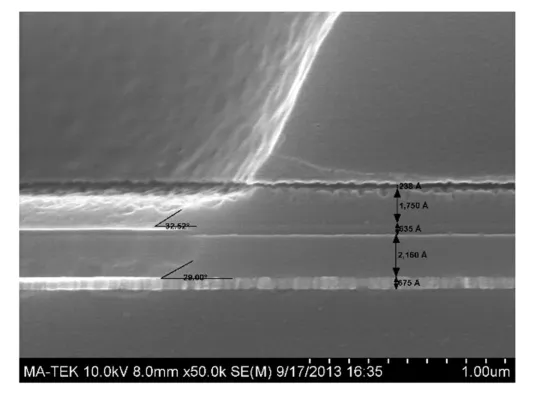

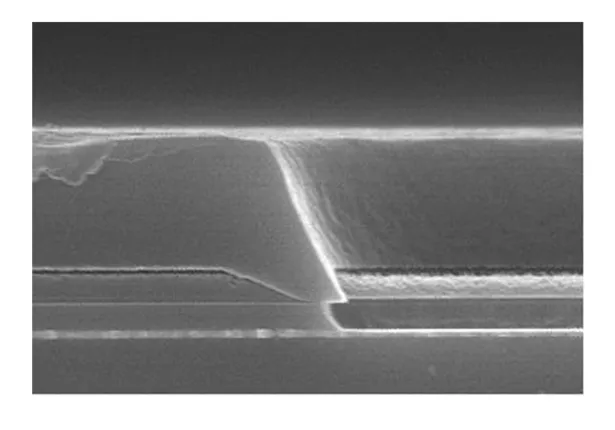

图4 未优化工艺前可见明显的undercut形Fig.4 Undercut shape formed before process optimized

图5 优化工艺后形成较好的taper角度Fig.5 Good taper angle formed after optimization of the processs

在钝化层沉积之后,进行干刻工艺对其刻蚀,一方面通过刻蚀将像素电极上的接触孔打通,可以使源漏电极金属与像素电极的ITO层形成电连接;另一方面,在TFT器件测试区域,通过本次干刻工艺之后,将源漏电极金属测试块与栅电极金属测试块暴露出来,可以对器件性能进行测试。文中所提及的TFT器件栅绝缘层采用双层结构,即Si3N4/SiO2结构,Si3N4具有较高的介电常数,用作栅绝缘层具有好的绝缘性;但由于IGZO在与Si3N4膜层接触会劣化TFT器件性能, 而IGZO与SiO2膜层接触则没有此问题,因此我们选择双层结构膜用作栅绝缘层。但是Si3N4膜层与SiO2膜层的刻蚀选择比较大,刻蚀速率分别为7.1 nm/s以及1.8 nm/s,通过传统的一次曝光、干刻之后,通过SEM观察接触孔断面,如图4所示;从图中可以看出,由于Si3N4膜层的干法刻蚀速率较快,Si3N4膜层刻蚀完成之后形成明显的下切角形状(undercut),ITO电极层沉积之后会出现断线风险,因此针对此双层工艺,我们对曝光干刻工艺进行了优化:钝化层SiO2膜层及栅绝缘层之上的SiO2膜层同时干刻,曝光时在标准曝光剂量(25 mJ/cm2)基础上增加曝光剂量(100 mJ/ cm2),使接触孔图形显影之后孔径稍微变大(单边增加~0.2μm),对此膜层进行干法刻蚀、剥离光刻胶;接着再次曝光,采用正常剂量曝光,接下来对栅绝缘层SiNx膜层进行干法刻蚀,刻蚀完成后即实现了接触孔的制作,如图5所示,从图中可以明显看出,SiO2膜层与Si3N4膜层之间的taper角度平滑适合ITO膜层的沉积,而不会出现电极层断线风险。

3.2 TFT器件性能

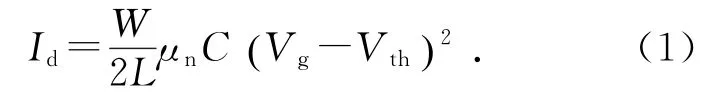

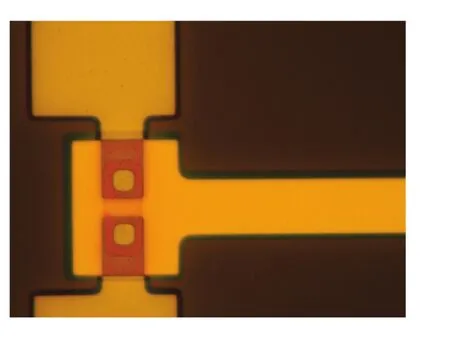

图6所示的图形为TFT器件性能测试用TEG结构,器件W/L=6μm/10μm,根据饱和区电流方程式(1)所示:

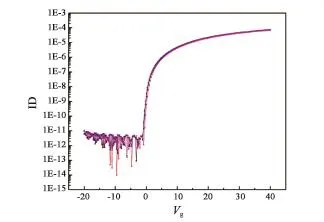

图7所示为TFT测试器件的I-V转称特性曲线,可以推算得到饱和迁移率μn约为14.8 cm2/(V·s),阈值电压Vth在0.5 V左右,亚域值摆幅SS接近0.5 V/decade,TFT器件的开关比Ion/Ioff>106。

图6 TFT测试器件OM图形Fig.6 OM picture of TFT test structure

图7 TFT器件性能I-V特性曲线,Vd=10.1 VFig.7 I-V curves of TFT device,Vd=10.1 V

4 结 论

本文讨论了基于PI柔性基底上的TFT器件制造工艺,采用氧化物IGZO作为TFT器件有源层,通过改进曝光、干刻等工艺,解决了在栅绝缘层双层结构即Si3N4/SiO2复合层膜的干法刻蚀由于刻蚀速率不同导致的undercut现象,避免了薄膜沉积后断线风险;同时,通过对此优化的TFT器件结构及工艺,所制备的TFT器件饱和迁移率μn达到14.8 cm2/(V·s),阈值电压Vth在0.5 V左右,亚域值摆幅SS接近0.5 V/decade,TFT器件的开关比Ion/Ioff>106,器件性能良好,满足LCD、OLED或电子纸的驱动要求。

[1] Wu C C,Theiss S D,Gu G,et al.Integration of organic LED′s and Amorphous Si TFT′s onto flexible and lightweight metal foil substrates[J].IEEE ELECTRON DEVICE LETTERS,1997,18(12):609-612.

[2] Zhou L S,Wanga A,Wu S C,et al.All-organic active matrix flexible display[J].Applied Physics Letters,2006, 88(8):083502.

[3] Jeong J K,Jin D U,Shin H S,et al.Flexible full-color AMOLED on ultrathin metal foil[J].Ieee Electron Device Letters,2007,28(5):389-391.

[4] Plichta A,Weber A.Ultra-thin flexible glass substrates[C].Proc.Mater.Res.Soc.Symp.,2003,769:H9.1-H9.10.

[5] Cheng I C,Kattamis A,Wagner S.Stress control for overlay registration in a-Si:H TFTs on flexible organicpolymer-foil substrates[J].J.Soc.Inf.Display,2005,13(7):563-568.

[6] Choi M H,Kim B S,Jang J.High-performance flexible TFT circuits using TIPS pentacene and polymer Blend on Plastic[J].Ieee Electron Device Letters,2012,33(1):1571-1573.

[7] Lim W,Jang J H,Kim S H,et al.High performance indium gallium zinc oxide thin film transistors fabricated on polyethylene terephthalate substrates[J].Applied Physics Letters,2008,93:082102.

[8] Chen C,Abe K,Kumomi H,et al.Density of states of a-InGaZnO from temperature-dependent field-effect studies[J].Ieee Transactions On Electron Devices,2009,56(6):1177-1183.

[9] Hsu H H,Chang C Y,Cheng C H,et al.Fully room-temperature IGZO thin film transistors adopting stacked gate dielectrics on flexible polycarbonate substrate[J].Solid-State Electronics,2013,89:194-197.

[10] Liu C,Wei M,Yang F,et al.Effects of electrode materials on the performances of IGZO-based thin film transistor [J].Chinese Journal of Luminescence,2014,35(11):1365-1369.

[11] Jia T Y,Zhan R Z,Dong C Y.Simulation of the stability of a-IGZO TFT-OLED pixel circuits[J].Chinese Journal of Luminescence,2013,34(9):1240-1244.

Process and properties of oxide IGZO TFT device based on flexible PI substrate

CHEN Long-long,ZHANG Jian-hua,LI Xi-feng∗,SHI Ji-feng,SUN Xiang

(Key Laboratory of Advanced Display and System Applications of Ministry of Education, Shanghai University,Shanghai 200072,China)

Bottom-gate structure TFT device technology on flexible PI substrate was discussed in the paper.Undercut shape of the double layer caused by the different dry etching rate was solved by the improvement of technics.The TFT device was based on IGZO as active layer,and Si3N4/SiO2double layer structure was employed as gate insulator,undercut shape introduced thin film deposition break risk was effectively solved using two times of exposure compensation.The experimental results show that,the taper angle of double-layer structure after dry etching which was observed using SEM was suitable for following film deposition of TFT devices.The mobility of TFT on flexible PI substrate reaches 14.8 cm2/(V·s),threshold voltage of Vthis about 0.5 V,subthreshold swing(SS)is about 0.5 V/decade,and ratio of Ion/Ioffis upper 106.TFT device performance by this method is good,and meets the driving requirements of LCD,OLED or electronic paper.

flexible;TFT;IGZO;mobility

TN321.5

A

10.3788/YJYXS20153005.0796

1007-2780(2015)05-0796-05

陈龙龙(1982-),男,山西朔州人,硕士,工程师,主要从事光电显示新型技术方面的研究。E-mail:llchen@shu.edu.cn

2014-11-06;

:2015-02-15.

上海市科学技术委员会项目(No.13111102200)

∗通信联系人,E-mail:lixifeng@shu.edu.cn