基于双TLB的二进制翻译访存性能优化

2015-01-01王振华靳国杰

李 晖,王振华,靳国杰

(1.中国南方电网有限责任公司,广州510623;2.中国科学院大学计算机与控制工程学院,北京100049;3.中国科学院计算技术研究所,北京100190;4.龙芯中科技术有限公司,北京100190)

1 概述

二进制翻译技术是一种直接翻译并运行可执行程序的二进制代码的技术,是实现不同指令集架构(Instruction Set Architecture,ISA)兼容的重要手段。在二进制翻译技术中,代码翻译前的平台叫客户机(Guest),代码翻译后的平台叫宿主机(Host)[1]。通过将客户机二进制代码翻译到宿主机平台,二进制翻译器可以在宿主机上模拟运行客户机平台的程序,从而实现对客户机体系结构的兼容。

龙芯处理器[2]是由中科院计算所是研制的MIPS兼容处理器,生态环境还很脆弱。通过使用二进制翻译技术,龙芯可以模拟运行为X86架构编写的程序,从而以较低的成本实现对X86指令系统的兼容,达到扩大自身的软件生态的目的。因此,研究二进制翻译技术对龙芯有重要意义。

然而,二进制翻译的客户机访存模拟代价较高。在二进制翻译系统中,客户机的访存指令在模拟执行时要进行3次地址转换:

(1)二进制翻译器将客户机虚拟地址(Guest Virtual Address,GVA)转换成客户机物理地址(Guest Physical Address,GPA)。

(2)二进制翻译器将客户机物理地址转换成宿主机虚拟地址(Host Virtual Address,HVA)。

(3)宿主机将 HVA转换成宿主机物理地址(Host Physical Address,HPA)。前2次地址转换带来了大量的软件开销。例如,在龙芯上使用动态二进制翻译器QEMU[3]运行X86软件时,一条X86访存指令需要用十多条MIPS指令来模拟。

本文分析在龙芯上运行X86软件的性能,指出客户机访存性能是主要的性能瓶颈,提出一种软硬件结合的性能优化方法。该方法通过在龙芯处理器中增加能直接进行X86虚实地址转换的硬件,消除二进制翻译器的访存地址转换的软件开销。

2 背景介绍

2.1 QEMU 概览

QEMU是一个支持多种指令系统的二进制翻译器,在客户机程序运行时对执行到的代码片断进行翻译并运行。QEMU支持的客户机指令系统包括X86,PowerPC,ARM和SPARC,支持宿主机指令系统包括X86,PowerPC,ARM,SPARC,Alpha和 MIPS。

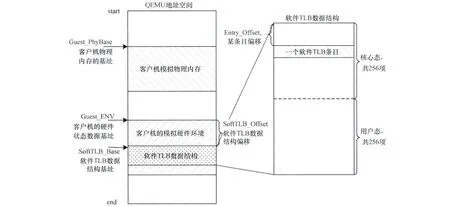

在QEMU这样的二进制翻译器中,客户机的物理内存使用宿主机的虚拟内存模拟,如图1所示。因此,执行访存指令翻译后指令时,访存地址要经过3次转换。二进制翻译器在做第1次地址转换时要查询客户机的页表,做第2次地址转换时要查询目标机物理地址(Guest Physical Address,GPA)到本机物理地址(Host Physical Address,HVA)的映射表。第3次地址转换由宿主机硬件地址转换装置宿主机翻译后备缓冲(Host Translation Look-aside Buffer,HTLB)完成。TLB是页表的高速缓存,用于快速地转换地址。使用TLB可以消除查询多级页表带来的软件开销,从而提高访存性能。HTLB做第3次地址转换时分2种情况:HTLB命中时,由HTLB直接转换;HTLB不命中时,宿主机查询自身的页表完成地址转换。前2次地址转换通过软件查询完成,因此,存在大量开销。第3次地址转换由HTLB完成,当运行具有高TLB命中率的访存密集型应用时,TLB不命中时引发的软件处理开销可忽略不计。

图1 QEMU软件TLB数据结构

2.2 QEMU软件TLB机制

作为一个二进制翻译器,QEMU精心设计了一套软件TLB机制,可以较快地将GVA转换成HVA。这套机制包含2个部分:(1)用来存放GVA到HVA映射关系的数据结构,由QEMU自动维护;(2)用来访问GVA-HVA映射的算法,在客户机访存指令翻译后代码执行时使用。

2.2.1 QEMU的软件TLB数据结构

QEMU的软件TLB数据结构存储在客户机模拟硬件的数据区中。该软件TLB采用直接相联结构,包含256项特权态表项和256项用户态表项。特权态访存使用特权态表项转换地址,用户态访存使用用户态表项转换地址。每个GVA只会被映射到一个唯一的表项。每个表项中都存储了3个客户机虚拟页面基址(Guest Virtual-page Base,GVB)的值和一个HVA与GVA的差值addr_end。

3个GVB分别是:读操作的虚拟地址GVB_read,写操作的虚拟地址GVB_write,可执行代码的虚拟地址GVB_code。这3个地址分别控制着其对应的客户机虚拟页面的读、写、可执行权限。根据一个访存操作的类型,软件TLB地址转换算法会取出3个地址中的一个,将其作为GVB,继续转换地址。由于客户机的物理内存是在QEMU虚拟内存中划分的一段连续空间,因此GPA和HVA之间拥有简单的数学关系:HVA=Guest_PhyBase+GPA。从而使得二进制翻译器不需要维护GPA-HVA映射。

2.2.2 QEMU的软件TLB地址转换算法

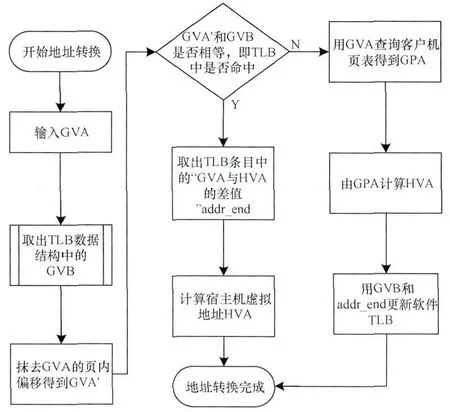

QEMU的软件TLB地址转算法的主要工作是将GVA转换成HVA,具体步骤如图2所示。

图2 软件TLB地址转换算法流程

该算法分为两部分:快速检索和慢速检索。快速检索用于查询软件TLB,它被嵌入到访存指令的翻译后指令中。慢速检索用于查询客户机页表,在快速检索失败后调用。因此,每次执行访存指令的翻译后代码时,都会运行快速检索来查询软件TLB,如果TLB命中,从软件TLB中取出addr_end;如果TLB不命中,模拟X86的页表查找操作。快速算法是图2中从开始到结束,并且TLB命中的路径,慢速检索是TLB未命中后接下来的3步。

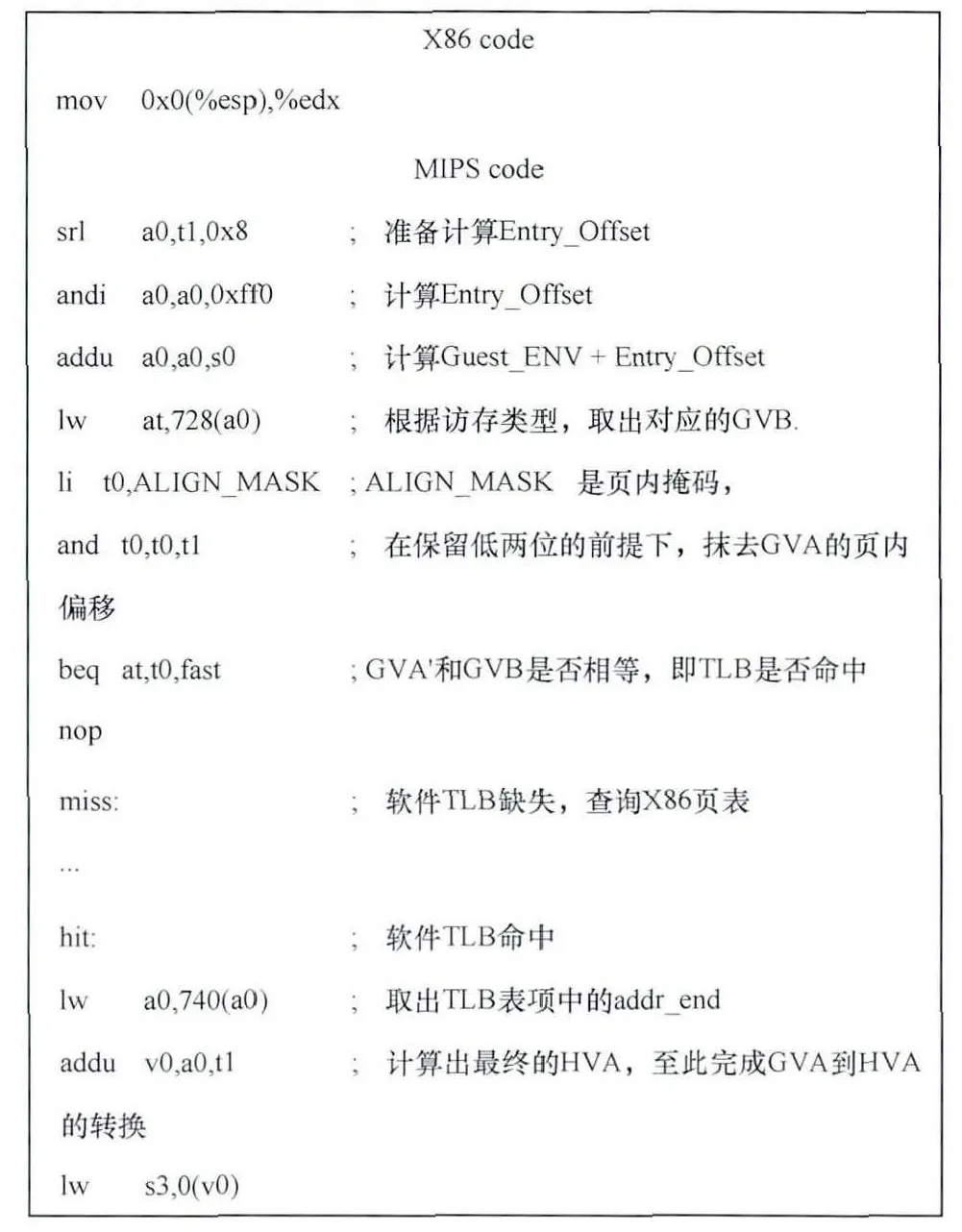

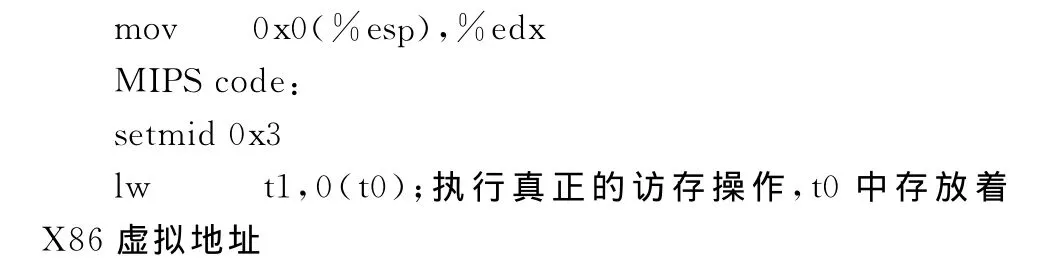

由于软件TLB的地址转换算法步骤较多,因此相对于使用硬件TLB做地址转换,QEMU采用的软件TLB做地址转换的代价仍然很高。在龙芯上模拟运行X86时,QEMU会将一条X86访存指令翻译成十多条MIPS指令。图3展示了一个访存指令的翻译实例和每条指令的具体操作含义,它和图2中快速检索过程对应。而一个常规的应用程序中,有30%左右的指令是访存相关指令[4]。这导致在翻译后代码中,有70%的指令是为了作地址转换,代价太高。因此,在二进制翻译系统中,客户机访存模拟的性能有着巨大的可挖掘空间。

图3 访存指令翻译后的代码实例

2.3 客户机访存模拟的优化方法

虚拟机的客户机访存性能低下,针对这一问题有3种改进方法,即模拟客户机TLB、影子页表(Shadow Page Table)和 硬 件 辅 助 (Hardware-assisted)优 化方法。

2.3.1 模拟客户机TLB的优化方法

模拟客户机TLB通过缓冲客户机页表来快速完成GVA-GPA转换,是一种纯软件优化方法。这种机制往往和指令翻译系统紧密结合,对客户机透明,且易于实现的方案。如2.2节所述,QEMU采用的就是模拟客户机TLB方法。

2.3.2 影子页表优化方法

影子页表中存储了GVA-HPA映射,将原本需要3次查询的地址转换合并为一次。影子页表的每个表项,都由运行于内核态的虚拟机监视器(Virtual Machine Monitor,VMM),经过3次地址转换得到。在客户机运行时,部分影子页表的表项会被缓存在HTLB。在后续访存中,如果GVA命中HTLB,客户机访存的速度可匹敌宿主机访存。内存开销大是影子页表的主要缺陷,因为VMM要为每个客户机进程维护一个影子页表。内核虚拟机(Kernel-based Virtual Machine,KVM)是一个采用影子页表的典型方案[5]。

2.3.3 硬件辅助优化方法

硬件辅助优化方法依赖于在处理器中增加新的硬件支持[6-8]。随着虚拟化技术逐渐普及,以Intel为代表的处理器厂商都为自己的产品增加了虚拟化硬件支持功能。

Intel扩 展 页 表 (Extended Page Table,EPT)[9]、AMD 嵌 套 页 表 (Nested Page Table,NPT)[10]是用于X86平台的客户机访存加速方案,它们的主要特点是用硬件实现了二级地址转换和客户机页表搜索器。二级地址转换通过在HTLB中同时缓存GVA-HPA映射和HVA-HPA映射实现,HTLB可以直接执行GVA-HPA转换。客户机页表搜索器在客户机TLB缺失时启动,通过自动检索客户机页表将GVA转换成HVA,再通过检索宿主机页表将HVA转换成HPA,最后将GVA-HPA映射加入HTLB中,以便下次访存时使用。这2种方案对虚拟机的性能提升都非常显著,AMD NPT使访存性能提升了42%,Intel EPT使访存性能提升了48%[11]。

IBM在Power架构上提出了虚实地址转换(Logical to Real Address Translation,LRAT)方案[12]。这种方案在处理器中增加了一个类似TLB的装置,即LRAT,其中存储着GPA-HPA映射。在该系统中,HTLB中也缓存了GVA-HPA映射,客户机TLB缺失例外由客户机和硬件协同处理。首先,客户机查询自身页表得到GVA-GPA映射;其次,客户机尝试将这对映射写入HTLB;再次,处理器用GPA检索LRAT得到HPA;最后,处理器将GVA-HPA映射更新到TLB中。LRAT方法将系统性能提高了232%。

Intel和AMD的技术适用于硬件管理TLB的体系结构,IBM的技术适用于软件管理TLB的结构。但这些方案都只能应用在相同ISA虚拟化系统中。目前尚未出现针对不同ISA虚拟化环境的客户机访存性能优化的硬件辅助手段。

3 软硬件结合的访存性能优化

针对QEMU这类二进制翻译器在转换客户机访存地址时性能低下的问题,本文提出一种硬件辅助访存性能优化方案,大幅提升了客户机的访存性能。该方案主要包含4部分:

(1)在处理器中增加支持直接将GVA转换为HPA的客户机专用TLB,从而消除QEMU软件TLB做地址转换的开销。

(2)通过在处理器中增加客户机的专用访存指令,从而将客户机访存指令和宿主机访存指令区分开,使得客户机的访存指令能直接将GVA作为访存地址。

(3)针对上述2项硬件支持,优化了二进制翻译器的指令翻译规则,大幅降低了访存指令的翻译后指令规模。

(4)新增的TLB引入了客户机TLB例外。本文设计了一套软件机制来处理这种例外,从而保障二进制翻译系统正常运行。

3.1 用于转换客户机地址的TLB

从QEMU的例子可以看到,即使采用了精心设计的软件TLB机制,二进制翻译器在为客户机做访存地址转换时还是有很高的额外开销。为了降低这种开销,一种直观的思路是使用硬件TLB直接将GVA转换成HPA,从而在TLB命中时将三步转换整合成一步。因为客户机地址转换由硬件TLB完成,所以可以完全消除软件开销。

3.1.1 直接使用HTLB存在的难题

然而,对于不同ISA虚拟化系统来说,直接使用HTLB来转换地址存在困难。一个体系结构的地址空间机制通常是该体系结构的特性,同一个虚拟地址在2种体系结构中的地址转换规则有可能是不同的。这种差异使得HTLB将无法将GVA转换成HPA。

例如,在MIPS中,虚拟地址和物理地址总是不同的,并且,最高位为1的地址只有核心态可以使用。而对于在X86上运行的Linux来说,32位虚拟地址空间映射分为2段:0x0000_0000-0xBFFF_FFFF是用户地址空间;0xC000_0000-0xFFFF_FFFF是内核地址空间。它们总是由TLB作地址转换。可见,当在 MIPS上模拟运行 X86时,因为0x8000_0000-0xBFFF_FFFF地址段在 MIPS中是不经过TLB转换的,所以不能使用HTLB将X86虚拟地址转换成MIPS物理地址。

为了解决使用HTLB将GVA转换成HPA存在的困难,可以在客户机硬件中增加专门用于将GVA转换成HPA的客户机专用地址转换装置GTLB(Guest TLB)。GTLB将二进制翻译器软件TLB和HTLB的地址转换工作合并。通过使用GTLB,客户机访存指令的翻译后指令在GTLB命中的情况下,地址转换次数从3次减少到1次,完全消除了二进制翻译器软件TLB带来的开销。

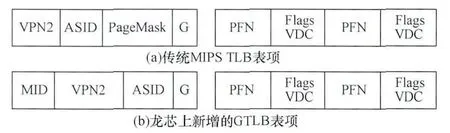

3.1.2 MIPS架构的传统TLB

龙芯的TLB表项结构如图4所示。传统的MIPS体系结构TLB表项包含5个重要的域,结构如图 4(a)所示。VPN2:虚页号 (Virtual Page Number),在地址转换时,虚拟地址的第12位决定取出哪一个PFN(Physical Frame Number),为0时取出第1个,为1时取出第2个;ASID(Address Space IDentifier):地址空间标识符,通常被操作系统用来标识进程;PageMask:页面掩码,用来控制被映射的页面大小;G(Global):全局位,当该位被置为1时,TLB表项匹配时总是将ASID域视为匹配的;PFN:物理帧号;Flags:页面属性位(包含3个描述页面权限的属性:V表示该页在内存中没有对应的物理页,D表示该页允许写入,C表示该页Cache(高速缓存)算法)。

图4 龙芯的TLB表项结构

对于每次地址转换,传统TLB的输入是<VPN2,PageMask,ASID>,转换成功时输出是<PFN>,转换失败时会触发TLB例外。

3.1.3 支持客户机地址转换的GTLB

本文通过结合MIPS的TLB结构特点和QEMU软件TLB的特点,在龙芯处理器上实现了一套能够将X86虚拟地址直接转换成MIPS物理地址的硬件装置GTLB,其表项结构如图4(b)所示。和传统的MIPS TLB相比,GTLB有2点不同:

(1)GTLB表项没有单独的PageMask域,而是增加一个用于描述所有页面掩码的寄存器GTLB_PageMask。由于X86中所有页面大小一致,因此可以为整个GTLB设置一个统一的PageMask来描述X86的页面大小。

(2)在每个GTLB表项中增加了一个机器标识符(Machine IDentifier,MID)域,用来区分 MIPS和X86的地址空间。在实际应用中,MID为0或1时表示该表项的地址属于MIPS地址空间,MID为2或3时表示该表项的地址属于X86地址空间。其中,MID为2时表示X86特权态;MID为3时表示X86用户态。

3.2 客户机专用指令

新增的GTLB简化了从GVA到HPA的地址转换,消除了二进制翻译器的地址转换开销。与此同时,由于硬件拥有2套地址转换装置,即HTLB和GTLB,对于任意一条访存指令,处理器要判断使用哪一套TLB来完成地址转换工作。为了解决这个问题,在处理器中增加了一个新的客户机专用指令SETMID。该指令用于指定下一条指令是否是客户机访存指令。如果是,处理器就使用GTLB作地址转换,否则使用HTLB。

3.3 指令翻译规则优化

通过在硬件上增加GTLB和客户机专用访存指令SETMID这2项支持,客户机的访存指令经过简单的格式转换就可以在宿主机上执行。

通过改造QEMU的软件TLB算法,可以完全消除翻译后指令在检索QEMU软件TLB数据结构的步骤,大大降低访存指令翻译后指令规模。对于一条常规的X86访存指令,新的翻译规则将其翻译成SETMID+Load/Store指令对。其中,X86访存指令的访存地址直接作为MIPS的访存地址来使用。下面是一个X86的用户态访存指令及其翻译后指令实例:X86code:

作为对比,图3是优化指令翻译规则之前的代码。可以看到,原本需要数十条MIPS指令才能模拟执行的X86访存指令,现在只需要2条MIPS就可以模拟执行。优化后访存相关的翻译后指令规模仅为优化前的20%,效果显著。

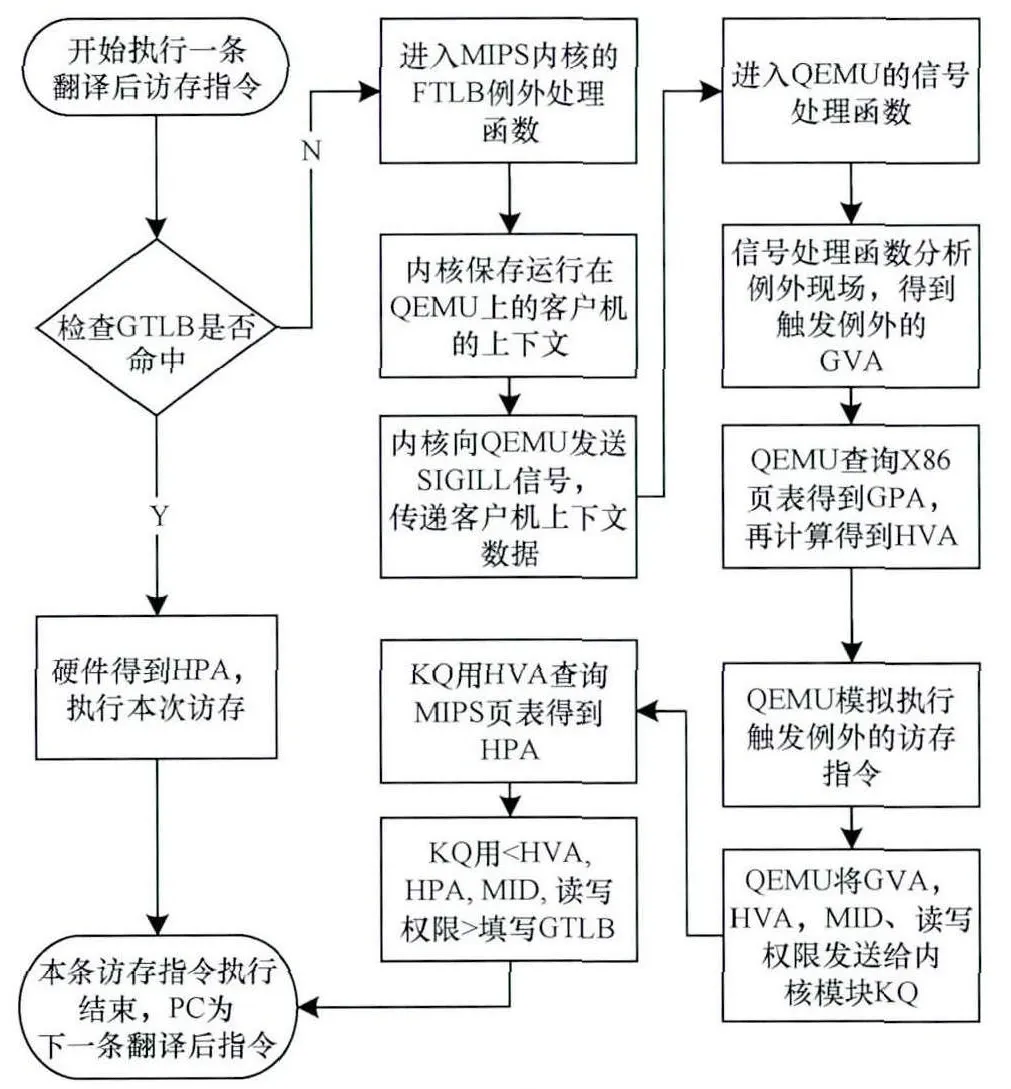

3.4 客户机的TLB例外处理

在增加客户机专用TLB、增加客户机访存相关指令、优化二进制翻译器的同时,客户机TLB例外出现了。能否处理好客户机TLB例外是决定这套硬件辅助优化方案成败的关键。

3.4.1 处理客户机TLB例外存在的困难

在传统的MIPS体系结构中,TLB例外分为3种:(1)TLB miss,TLB缺失例外,当TLB中找不到访存地址对应的表项时发生;(2)TLB invalid,TLB无效例外,当访存地址所在页面不再物理内存中时发生;(3)TLB modify:TLB修改例外,当一个store指令尝试修改只读页面里的数据时发生。TLB miss有独立的例外入口,TLB invalid和TLB modify共享例外入口,这3种例外在内核中有各自独立的处理程序。

和传统的MIPS TLB例外类似,龙芯中新增的GTLB也有3种例外,即 GTLB miss,GTLB invalid,GTLB modify。为这3个例外编写新的例外处理程序存在一定的困难,因GTLB的例外无法由内核或QEMU单独处理。因为软件在修改GTLB时,至少要满足2个条件:(1)有用来更新GTLB表项的数据,主要是GVA和HPA;(2)有更新GTLB的权限,即软件运行在核心态。对内核来说,它拥有更新GTLB的权限,拥有GVA,但没有与之对应的HPA。对QEMU来说,它拥有GVA到GPA的映射关系,即X86页表,也拥有GPA到HVA的映射关系,但没有HVA到HPA的映射关系,即MIPS页表。同时,QEMU运行在用户态,没有修改GTLB的权限。因此,GTLB的例外需要内核和QEMU协作才能处理。

3.4.2 处理客户机TLB例外的软件系统

为了处理GTLB例外,本文设计了一套软件系统,主要分为3个部分:

(1)支持GTLB例外处理的定制版Linux内核:在GTLB例外入口处编写函数,该函数的作用是保存运行时上下文,通过内核的信号机制向QEMU发送SIGILL信号,将例外现场信息传递给QEMU。由于该函数放置在GTLB例外入口处,因此只有以SETMID为前缀指令的访存指令触发GTLB例外时才会执行。

(2)支持处理SIGILL信号的QEMU:修改后的QEMU接管了SIGILL信号,因此,当内核向QEMU发送SIGILL信号时,会调用QEMU中的信号处理函数。在SIGILL信号的处理函数中,QEMU分析内核传递过来的例外现场,调用相关函数查询X86页表得到GPA,再将GPA转换成HVA,最后将GVA,HVA,MID等信息通过proc文件系统传递给内核模块KQ(Kernel Qemu)。

(3)辅助QEMU修改GTLB的内核模块KQ:KQ接收到来自QEMU的GTLB操作请求,如若是添加GTLB表项请求,则用HVA查MIPS页表得到HPA。至此,用来修改GTLB的数据已经齐备。接下来,如果是删除GTLB表项请求,就删除掉GVA,MID对应的GTLB表项;如果是添加GTLB表项请求,则用GVA,HPA,MID和读写权限更新GTLB。

GTLB miss例外的处理流程如图5所示。

图5 GTLB miss例外的处理流程

从左开始第1列是硬件的相关步骤,第2列是内核的相关步骤,第3列是QEMU的相关步骤。GTLB modify例外拥有类似的处理流程;而GTLB invalid例外不会发生,因为GTLB miss例外在处理时已经真正执行了访存指令,所有GTLB表项对应的页都已经在物理内存中分配。

通过使用这套软件系统,GTLB例外被完善地处理,使得客户机访存指令翻译后指令在优化后能正常执行,从而为大幅提高客户机的访存性能提供保障。

4 实验结果与分析

4.1 实验平台和方法

本文在EVE硬件仿真加速平台上建立软硬件系统环境,在客户机中运行性能测试程序,从而评估二进制翻译性能。EVE是Synopsys公司的快速硬件仿真系统,它使得在芯片流片前验证整个软硬件系统的功能和性能成为可能。

测试的硬件平台是龙芯3A1500处理器,这款处理器包含了针对X86客户机的硬件支持,包括X86专用的GTLB和指令SETMID。软件平台包括优化了访存指令翻译机制的QEMU、支持GTLB例外处理的Linux内核和辅助QEMU修改GTLB的内核模块KQ(Kernel Qemu)。运行的客户机性能测试基准程序包括:用于测试峰值访存性能的memcpy,用于测试平均性能Linux内核。由于仿真平台的运行速度较慢,在客户机中运行SPECCPU2000这样的测试程序耗时约长达数月,因此本文没有测试。

测试过程包含4步:(1)在EVE上启动 MIPS的Linux内核;(2)在 MIPS内核中启动QEMU;(3)在QEMU中启动X86的Linux;(4)在X86的Linux上运行X86性能测试基准程序,获得测试分值。

性能对比方法是,通过在EVE上运行优化前和优化后的二进制翻译系统,分别在客户机Linux中运行各项测试,对比优化前Origin配置和优化后Optimize的数据,分析优化成果。2种配置的差异在于二进制翻译系统是否启用了硬件辅助优化功能来加速客户机地址转换。

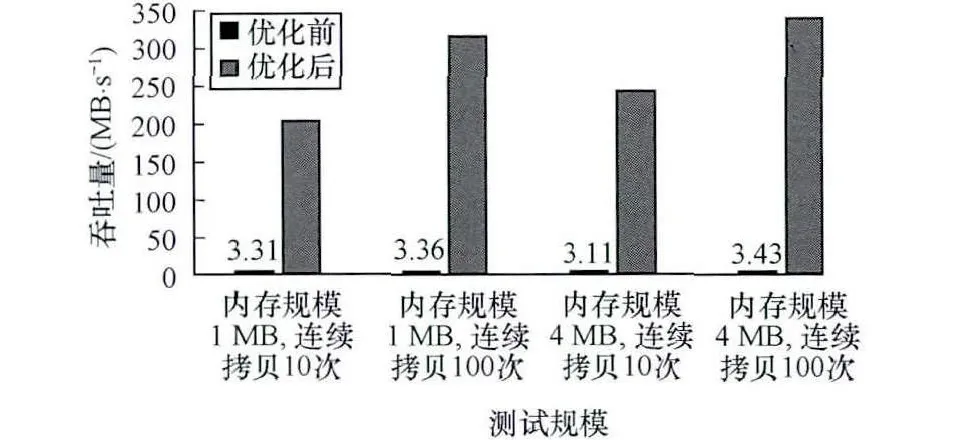

4.2 内存拷贝性能测试

内存拷贝性能测试基于C库中的Memcpy函数编写,测试配置为拷贝内存大小为X的数组Y次。

图6的实验结果表明,在不同的配置下,优化后的内存拷贝性能为优化前的100倍,优化效果极其突出。

图6 内存拷贝性能测试

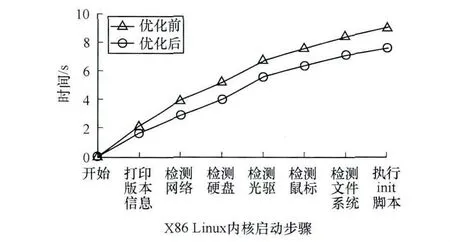

4.3 Linux启动时间

Linux在工业界应用极为广泛,本文采用其启动花费的时间来评估系统的平均性能。2种配置的Linux内核启动时间如图7所示。

图7 Linux内核启动时间测试

可以看到,优化后Linux内核启动时间缩短了19.12%,优化效果明显。

5 结束语

本文分析了龙芯二进制翻译系统性能,指出了其性能瓶颈在于客户机访存,设计一套软硬件结合的客户机访存性能优化方案,并测试了优化后系统的性能。该方案以用硬件TLB转换客户机地址为思路,以双重硬件TLB为特征。优化后的系统完全消除了客户机地址转换过程中的软件开销。实验结果表明,优化后内存拷贝性能提升了100倍,Linux内核启动时间缩短了19.12%,优化效果明显。本文方案是在不同ISA虚拟环境中,用硬件实现客户机地址转换,对其他处理器平台的客户机性能优化有借鉴意义。

随着二进制翻译中客户机访存性能的优化空间被硬件辅助方案挖掘得所剩无几,该领域的热点研究方向将转向I/O设备模拟,特别是图形显示加速器的模拟。如果I/O模拟的性能取得显著成果,虚拟化技术的应用将会得到进一步普及。

[1]James S,Ravi N. Virtual Machines: Versatile Platforms for Systems and Processes[M].San Francisco,USA:Morgan Kaufmann Publishers,2005.

[2]Hu Weiwu, Zhang Fuxing, Li Zusong.Microarchitecture of the Godson-2Processor[J].Journal of Computer Science and Technology,2005,20(2):243-249.

[3]Bellard F.QEMU,a Fast and Portable Dynamic Translator[EB/OL].(2010-11-21).http://laokaddk.blog.51cto.com/368606/743624/.

[4]Hennessy J L,Patterson D A.Computer Architecture:A Quantitative Approach[M].5th ed.San Francisco,USA:Morgan Kaufmann Publishers,2011.

[5]Kivity A,Kamay Y,Laor D,et al.KVM:The Linux Virtual Machine Monitor[EB/OL].(2011-10-19).http://www.techrepublic.com/resource-library/whitepape rs/kvm-the-linux-virtual-machine-monitor/.

[6]Ebciogˇlu K, Altman E R. DAISY: Dynamic Compilation for 100%Architectural Compatibility[C]//Proceedings of the 24th Annual International Symposium on Computer Architecture.New York,USA:ACM Press,1997:26-37.

[7]Chernoff A,Herdeg M,Hookway R,et al.FX!32:A Profile-directed Binary Translator[J].IEEE Micro,1998,18(2):56-64.

[8]Dehnert J C,Grant B K,Banning J P,et al.The Transmeta Code Morphing Software:Using Speculation,Recovery,and Adaptive Retranslation to Address Real-life Challenges[C]//Proceedings of International Sym-posium on Code Generation and Optimization: Feedback-directed and Runtime Optimization.Seattle,USA:IEEE Computer Society,2003:15-24.

[9]张雪兰,谭毓安,李元章.RIntel 80X86/Pentium汇编语言程序设计[M].3版.北京:北京理工大学出版社,2009.

[10]Bhargava R,Serebrin B,Spadini F,et al.Accelerating Two-dimensional Page Walks for Virtualized Systems[J].ACM SIGOPS Operating Systems Review,2008,42(2):26-35.

[11]Bhatia N.Performance Evaluation of AMD RVI Hardware Assist[EB/OL].(2009-03-17).http://www.yellow-bricks.com/2009/03/17.

[12]Chang Xiaotao,Franke H,Ge Yi,et al.Improving Virtualization in the Presence of Software Managed Translation Lookaside Buffers[C]//Proceedings of the 40th Annual International Symposium on Computer Architecture.New York,USA:ACM Press,2013:120-129.