低功耗可配置的USB 3.0设备控制器IP核设计

2015-01-01蒋进松修思文严晓浪

黄 凯,林 威,蒋进松,胡 腾,修思文,严晓浪

(1.浙江大学a.电子信息技术与系统研究所;b.超大规模集成电路设计研究所,杭州310027;2.中国计量学院光学与电子科技学院,杭州310018)

1 概述

USB因具备热插拔、易扩展的特点,在计算机外设接口中得到了广泛应用。随着科技不断发展,各式各样的新设备不断涌现,尤其是多媒体格式和大容量存储器的普及,大幅提高了对传输速率的要求。传统 USB 2.0[1]协议的最大带宽只有480Mb/s,已经远不能满足用户的需求。于是,新一代USB传输协议——USB 3.0[1]应运而生,其传输带宽高达5.0Gb/s,已成为目前研究的热点。随着集成电路集成度的不断提高,功能日趋复杂,基于知识产权(Intellectual Property,IP)重用的片上系统(System on Chip,SoC)设计方法已成为集成电路设计的主流。因此,对实现各种类型的支持USB 3.0接口的外设产品而言,USB 3.0设备控制器IP不可或缺。

基于USB 3.0设备控制器IP的可重用性,可将其集成到目标芯片中,从而提高芯片设计效率,降低设计风险。在USB 3.0设备控制器设计中,IP的可配置性是提高可重用性的关键[2]。IP的可配置性主要体现在接口和功能上。接口可配可以简化集成的复杂度;功能可配可以在性能和成本之间取得良好的折中。同时,随着SoC系统规模的不断增大,芯片的功耗也是设计者需要关注的指标,尤其是对移动设备的功耗指标要求更高。为了满足芯片的功耗指标,对USB 3.0设备控制器进行低功耗设计是非常必要的。USB 3.0协议支持全双工工作,在单方向传输时,另一通道处于空闲状态。USB在某些链路状态下,处于空闲状态而没有进行包的传输。如何减少这些空闲状态的功耗是关键。

本文设计一种灵活可配、低功耗的USB 3.0设备控制器。USB 3.0设备控制器支持系统总线可配、物理层接口可配、端点属性可配、缓冲可配以及低功耗策略可配,增强了IP可重用性。采用门控时钟和门控电源2种低功耗策略减少功耗。使用IP-XACT标准[3]对USB 3.0设备控制器进行封装设计,使其可快速集成到目标系统中,并自动生成仿真平台。

2 协议分析

USB 3.0协议向下兼容 USB 2.0协议,因此USB 3.0设备控制器(简称U3DC)应实现高速和超高速两部分[4]。高速部分的实现技术已成熟,本文不作详细介绍。本文设计的U3DC,实现了超高速部分的协议层和链路层,通过标准的PIPE(Physical Interface for PCI Express)接口与第三方物理层相连完成超高速功能。图1为USB 3.0协议层和链路层的数据通道示意图。

图1 USB 3.0协议层和链路层的数据通道

超高速链路层主要负责链路管理并确保数据的正确传输。对于设备到主机(IN)的传输,链路层从协议层接收包头(Packet Header,PH)或数据。链路层向包头插入头包帧标识(HPSTART)、CRC16和链路控制字(Link Control Word,LCW)组成头包(Header Packet,HP),向数据插入 CRC32、数据包载荷帧起始标识(DPPSTART)和帧结束标识(DPPEND)组成数据包载荷(DATA Packet Payload,DPP),并通过仲裁器向物理层选择输出头包、数据包载荷和链路命令(Link Command,LC)[5]。对于主机到设备(OUT)的传输,链路层负责提取、解析链路命令,并检测包的正确性,流程如图2所示。链路层还定义了链路训练状态机,主要用于链路状态和功耗管理。按照USB 3.0协议的规定,链路训练状态机共12个状态。其中,U0状态为普通运行状态;U1,U2,U3为空闲状态,链路之间无包传输;U3状态又称挂起状态,其退出时间比U1,U2的退出时间更长。

图2 链路层接收流程

超高速协议层定义了在主机和设备端点(endpoint)之间的通信规则。协议中定义了2种包结构:头包和数据包载荷;4种包类型:链路管理包(Link Management Packet,LMP),事务包(Transaction Packet,TP),数据包(Data Pack,DP)和同步时间戳包(Isochronous Timestamp Packet,ITP)。其中,数据包由数据包头(Data Packet Header,DPH)和数据包载荷构成。LMP,TP,ITP,DPH均属于头包。协议层还定义了4种传输类型:控制传输,批量传输,中断传输和同步传输。控制传输用于设备的枚举过程,其余3种传输用于设备的功能实现。协议层对接收到的包进行类型判定后,再对头包剩余字段进行解析处理,若为数据包头,则开始接收数据包载荷。协议层根据处理信息,生成相应的包进行响应,如成功接收数据包后生成ACK TP进行响应。

3 控制器设计

U3DC总体架构如图3所示,主要分为三部分:应用层接口单元,同步模块和USB功能模块。应用层接口单元负责控制器功能模块和系统之间的通信。USB功能模块负责完成除物理层之外的高速协议和超高速协议。U3DC共有以下4个时钟域:应用层接口工作时钟域(bus_clk),高速协议部分工作时钟域(mac2_clk),超高速协议部分工作时钟域(mac3_clk)以及低频率的挂起时钟域(sp_clk),由时钟/复位单元模块负责内部时钟和复位的管理。由于应用层接口单元与USB功能模块的工作时钟在不同的时钟域,因此需要同步模块进行同步。同步模块中包含多路数据选择器,根据USB工作的速度模式来决定数据流走向。

图3 USB 3.0设备控制器架构

USB 3.0设备控制器架构主要包含以下部分:

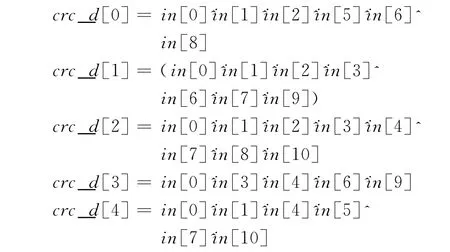

(1)超高速协议部分。链路层由链路控制单元、发送单元和接收单元组成。发送单元和接收单元负责发送和接收数据。链路层确保数据正确性的措施之一是CRC校验。CRC5,CRC16和CRC32分别用于检查链路控制字、头包包头和数据包净负载的正确性。在USB 3.0协议中,数据最高带宽可达5.0Gb/s,CRC串行生成方法并不能满足实时性,本文采用并行设计方法。CRC5余数初始值为5’h1f,其生成多项式为:G(X)=X5+X2+1。

推导出CRC5的余数多项式表达式为:

其中,in[10:0]为链路控制字中除CRC5之外的11位链路控制信息。对于CRC16和CRC32C,每次输入32位数据,得出的余数作为下一次的余数初始值,经过多次计算得出最终余数。虽然并行设计方法带来了额外的硬件开销,但提高了性能。

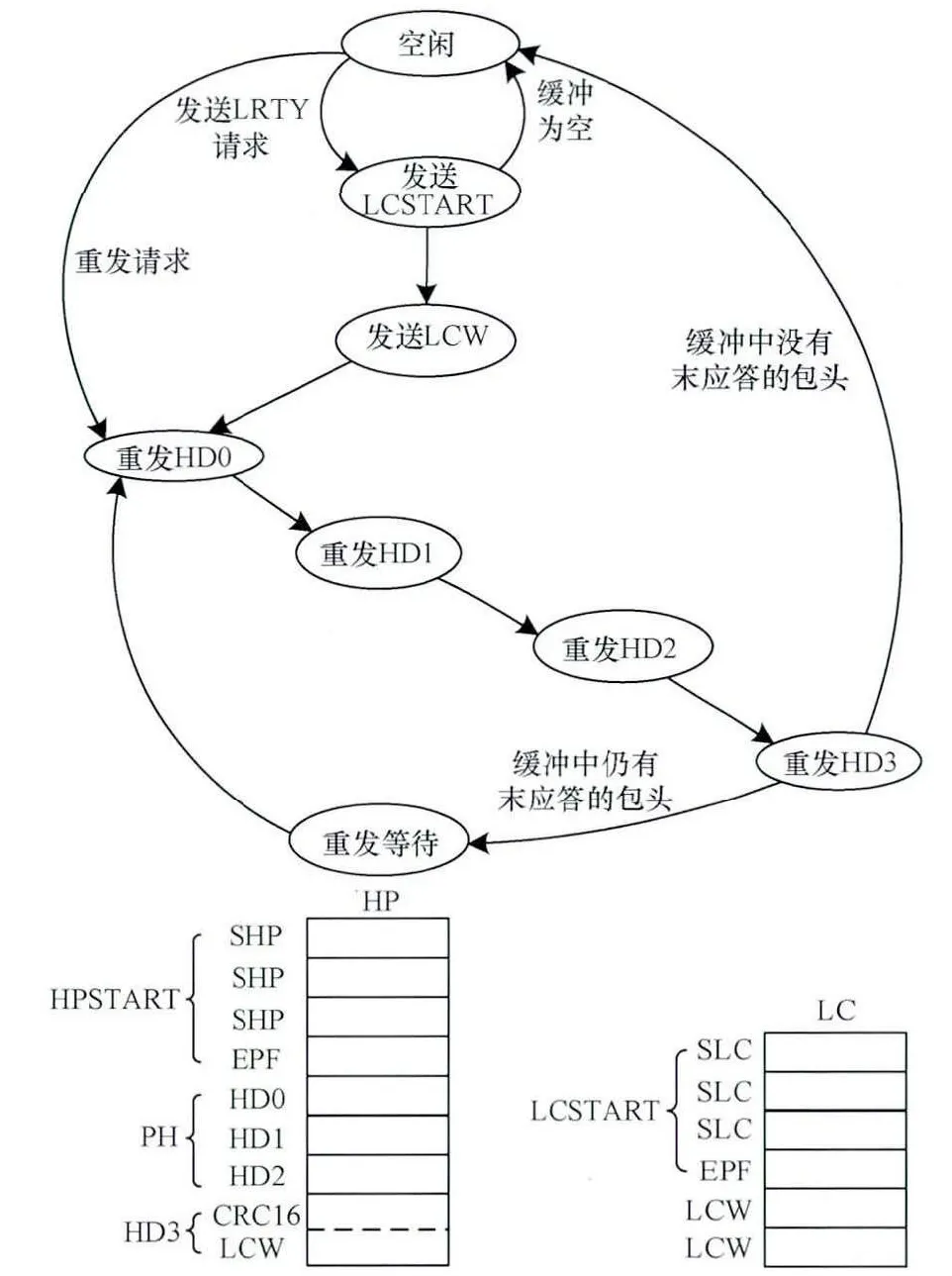

链路控制单元由链路训练状态机、低功耗控制器和重发控制模块组成。当进入U1,U2,U3状态时,低功耗控制器通知发送单元和接收单元不再进行包传输。为了能够存储4个未收到应答的包头,在重发控制模块中实现一个4个包头大小的重发缓冲[6]。为了能够定位需要重发的包头位置,重发缓冲除了需要读、写指针外,还需要额外的定位读指针来指向第一个未收到应答的包头。当收到LBAD命令或进行恢复操作,重发控制器须发送未应答的头包。图4显示了重发控制器的状态机。

根据4种传输类型,端点可分为:控制端点,批量端点,中断端点和同步端点。U3DC支持端点个数可配,最多可支持16个IN端点和16个OUT端点。端点0固定为控制OUT端点,端点1固定为控制IN端点。其余端点属性支持软件可配,通过对端点属性的判定,选择相应的控制逻辑。端点属性可配虽然增加了硬件开销,但增强了应用的灵活性。协议传输层中的发送和接收传输引擎分别负责所有端点的IN传输和OUT传输,控制引擎负责传输管理,并将传输状态更新到应用层接口单元。

图4 重发控制器状态机

(2)应用层接口单元。总线带宽有限会降低U3DC性能以及增加等待功耗。增加先入先出(First In First Out,FIFO)缓冲可有效地提高总线性能。缓冲根据协议传输状态进行读写,又约束协议传输层的传输,即协议传输层和缓冲管理单元共同实现了协议层。缓冲由双端口的RAM组成,其尺寸可根据端点支持的最大包尺寸和突发操作个数进行配置,其中发送缓冲的个数可配。当进行IN传输时,U3DC将数据预取到发送缓冲中以提高性能,但若此时有n个有效的IN端点,控制器将无法判断主机从哪个IN端点获取数据,因此缓冲管理单元需要配置n个发送缓冲。当进行OUT传输时,调度控制单元根据接收缓冲剩余空间对主机的请求进行响应。当接收缓冲剩余空间小于一个包尺寸时,调度控制单元将向协议传输层发送未准备(Not Ready,NRDY)请求;当调度控制单元从协议层接收到CRC32校验错误或者数据包负载丢弃标识(Data Packet Payload Abort,DPPABORT),存入接收缓冲的数据将被丢弃。

(3)可配置模块。为了能够快速集成到目标芯片中,U3DC在接口上支持系统总线可配和物理层接口可配。U3DC的总线主从接口支持硬件可配以及AHB/AXI总线[7]。为了达到一定的吞吐量,其数据位宽可根据系统频率进行配置。USB 2.0物理层接口单元支持硬件可配,支持UTMI(USB 2.0 Transceiver Macro Cell Interface)和 ULPI(USB 2.0Transceiver Macro Cell Low Pin Interface),且数据位宽支持8位、16位。USB 3.0物理层接口单元负责完成PIPE接口的控制时序逻辑,数据位宽支持8位、16位、32位。为了使U3DC的时序更容易收敛,USB 3.0链路层和物理层接口单元的数据宽度固定为32位,通过多路数据选择器实现位宽匹配,同时对物理层提供的pipe_clk时钟进行相应的分频。

4 低功耗设计

4.1 门控时钟

门控时钟策略是低功耗设计中最常用的技术之一,主要减小非工作状态逻辑的动态功耗[8]。U3DC包含高速模块和超高速模块,其中只有一个模块进行工作,另一个模块处于空闲状态。超高速模块分为发送和接收2个独立的通道,当只进行单一方向传输时,另一通道处于空闲状态。超高速模块还定义了U1,U2,U3 3种低功耗状态。在这3种低功耗状态下,超高速模块不进行数据传输,处于空闲状态。这些空闲状态使得通过门控时钟降低动态功耗成为可能。超高速工作模式下的门控时钟架构及其核心单元如图5所示。

图5 门控时钟架构及其核心单元

门控时钟架构主要包含以模块:

(1)超高速协议模块。当控制器工作在超高速模式下,链路层接收单元未收到来自物理层的有效数据时,处于空闲状态,工作时钟被屏蔽;链路层发送单元未收到来自协议层的有效数据或来自链路控制单元的发送链路命令请求时,处于空闲状态,工作时钟被屏蔽。在OUT传输中,链路层对收到的头包和数据包载荷进行检查后,将正确的包头和数据传到协议层中,此时接收引擎开始工作。在IN传输中,控制器不需等待主机的应答便可继续发送下一个数据包,因此整个过程中发送通道的工作时钟不被屏蔽。当控制器进入挂起模式时,mac3_clk切换成低频率的sp_clk以降低部分动态功耗。当工作模式切换成高速模式,超高速模块逻辑处于非工作状态,mac3_clk被屏蔽。

(2)应用层接口单元。根据总线带宽分配情况以及对缓冲空间是否达到阈值的判定对读写控制单元的工作时钟进行屏蔽和开启。当进行OUT传输时,接收缓冲接收主机发送的数据,而发送缓冲处于空闲,其时钟被屏蔽。当总线带宽较低时,可能导致OUT传输结束时,接收缓冲中仍有数据,需要读写控制单元继续将数据写到系统存储中。当进行IN传输时,发送缓冲的时钟一直开启。

4.2 门控电源

U3DC在挂起模式时,虽然通过降低工作频率可减少大部分动态功耗,但仍存在一定的动态功耗和静态功耗。而此时的U3DC只负责检测唤醒,大部分逻辑是空闲的。所以,在设计中采用了门控电源策略,以减少冗余逻辑的功耗。当采用门控电源策略时,U3DC会增加功耗管理单元。功耗管理单元与芯片中的电源管理单元配合工作完成进入、退出休眠模式(hibernation),其架构如图6所示。U3DC的工作电压为V1,功耗管理单元的工作电压为V2,可根据需求将V1断开。这2个电源域之间需添加隔离单元(isolation cell),以免U3DC重新上电时对功耗管理单元有所影响。当U3DC进入挂起模式时,可通过软件配置请求进入休眠模式,电源管理单元通知U3DC和功耗管理单元进入休眠模式,并等到功耗管理单元接管物理层接口后,将电源V1断开。进入休眠模式分2种情况:(1)与Host保持连接(connect),Device进入挂起模式;(2)Device检测到断开连接(disconnected)中断,进入挂起模式。退出休眠模式与进入休眠模式相对应。

图6 功耗管理架构

进入和退出休眠模式流程如图7所示。当Device与Host保持连接并进入挂起模式时,软件可配置U3DC进入休眠模式。首先,U3DC结束当前传输,并把端点信息和寄存器值存储到功耗管理单元中。完成信息存储后,功耗管理单元将接管物理层接口,并通知电源管理单元将U3DC的电源断开。当功耗管理单元检测到唤醒逻辑或软件配置退出休眠模式时,电源管理单元将恢复U3DC的电源。U3DC从存储单元中读取寄存器值用于控制器的初始化,读取端点信息用于恢复传输。而当U3DC在disconnect状态下进入休眠模式时无需存储信息,退出休眠模式时也不用读取任何存储信息。

图7 休眠模式切换流程

5 面向SoC的IP核设计

IP和平台复用可大大降低SoC的设计复杂度,业界提出了多种标准用于IP和平台复用的电子自动化设计。其中,IP-XACT标准因在IP可配置和系统平台搭建上的优越性得到了广泛应用。本文设计中采用IP-XACT标准,将U3DC进行封装,并利用SoC_Integrator(SI)[9]导入 USB库文件进行 USB配置、SoC系统集成以及仿真平台搭建。USB库文件包括USB IP-XACT xml文件、USB生成器、USB RTL代码模板以及USB验证模板。xml文件中描述了U3DC的物理层接口、总线接口以及配置参数。验证模板包括测试激励和测试IP(Verification IP,VIP)。

SoC集成流程如图8所示。首先。SI导入各个IP的xml文件,通过分析获取IP名和工艺信息,通过用户界面配置各个IP的参数,并更新其xml文件的配置信息。配置完成后,SI将各个IP的库文件拷贝到工作目录下,并调用IP生成器。USB生成器会根据配置信息进行以下操作:(1)生成目标RTL代码。根据配置参数,修改RTL宏文件,从而开启或屏蔽硬件逻辑。(2)生成激励。根据配置信息,修改测试激励的宏文件,从而生成与目标RTL代码相对应的激励。(3)修改 VIP。若配置参数“Instance Device PHY in SoC”为Yes时,USB生成器删除VIP模板中的设备物理层单元;(4)修改xml文件。USB生成器根据接口的配置参数,删除xml中无用的端口信息。(5)SI分析修改后的xml文件,获取互连和仿真信息实现系统集成和仿真平台的搭建。

图8 SoC集成流程

为验证U3DC的功能,仿真平台需建立主机模型与之通信。主机模型可通过配置发起特定的传输、检测U3DC的响应并对比接收数据和发送数据。USB传输类型分控制传输、批量传输、中断传输和等时传输,而USB传输方向分IN传输和OUT传输。测试中不仅需要覆盖所有这些传输,还需测试控制器的低功耗管理以及USB纠错功能[10-11]。配置参数“Instance Device PHY in SoC”为Yes时,仿真平台如图9所示,CPU通过总线与U3DC进行通信,U3DC与第三方 USB 2.0PHY,USB 3.0PHY 相连之后再与Host行为模型进行通信。系统存储分为两部分,分别存储通信数据与特定的触发数据以同步CPU和Host行为。CPU通过执行test.c编译生成的汇编指令进行U3DC的初始化配置和端点配置,若为IN传输还需准备净载数据包。CPU完成U3DC的配置后,向同步存储中写入触发数据以触发test.v调用任务进行Host配置,使其发起特定的传输。在每次传输完成后,对比收发数据是否一致。在整个传输过程中BUS Monitor监测USB总线行为,并将总线事件输出到test.log中,以便调试。

图9 U3DC功能仿真平台

6 实验结果与分析

6.1 面积评估

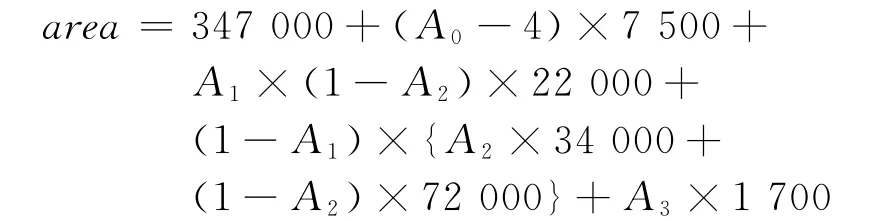

本文提出的U3DC具有较高的可配置性,可根据应用需求进行配置。为满足应用的基本需求,控制器的端点个数不会少于4。不同配置下的U3DC面积有所不同。本文采用smic55LL工艺库,使用Synopsys编译器进行综合,对不同配置下的U3DC进行面积统计,如表1所示(统计中未包含FIFO面积)。

表1 不同配置的控制器面积统计

然而,UTMI,ULPI接口的数据宽度、PIPE接口的数据宽度和总线从接口类型配置对控制器的面积影响很小,因此表格中未列出其配置。根据配置1和配置2的差异可得,功耗管理模块面积约4 000μm2;根据配置1和配置3的差异可得,ULPI封装逻辑面积约1 700μm2;根据配置1、配置4、配置5、配置6的差异可得,每增加一个端点面积约增加8 000μm2;根据配置1、配置7的差异可得,当总线主接口为AHB时,数据位宽从32位扩展到64位时,面积增加约为22 000μm2;根据配置8、配置9的差异可得,当总线主接口为AXI时,数据位宽从32位扩展到64位时,面积增加约为38 000μm2。

根据上述分析,为方便IP配置评估,推出U3DC的初步面积计算公式为:

其中,参数A0表示端点数;参数A1:0表示总线主接口为AXI,1表示为AHB;参数A2:0表示总线宽度为64位,1表示总线宽度为32位;参数A3:0表示USB2.0物理层接口为UTMI,1表示ULPI。

6.2 功耗评估

将配置2中的U3DC集成到SoC实验平台中,并使用Power Compiler进行功耗评估,其中SoC实验平台中使用杭州中天微系统有限公司的CK610处理器[12],四 川 和 芯 微 电 子 股 份 有 限 公 司 的USB2.0 PHY[13]和USB3.0PHY[13]。在评估功耗中,约束时钟bus_clk为125 MHz,mac3_clk为125 MHz,mac2_clk为30 MHz,sp_clk为12 MHz。表2为控制器在U0状态下使用门控时钟前后的功耗比较,实验结果表明使用门控时钟策略能节省约50%的动态功耗。

表2 门控时钟使用前后的U0功耗比较 MW

表3为U3DC在超高速模式下不同状态的功耗统计。从U0切换到U1/U2,减少了约50%的动态功耗;从U0切换到U3时,动态功耗减少了约66%。而当进入休眠模式时,动态功耗和静态功耗都有大幅度的下降,总功耗比U3减少了95.5%。

表3 超高速模式下不同工作状态的控制器功耗统计 MW

6.3 FPGA验证

FPGA原型验证是IC设计中一种重要的验证手段,可在FPGA应用开发中提早发现电路设计中的问题。对上述的SoC实验平台完成功能仿真后,将其在FPGA开发板上进行实现。其中,测试超高速的开发板平台如图10所示。

图10 FPGA开发板平台

开发板平台使用S2CDual Virtex-6TAI Logic Module[14]。将SoC平台中的处理器CK610和U3DC等逻辑映射到Virtex6中,通过I/O接口外接USB 3.0物理层测试样片和128MB的SDRAM。因为PIPE接口时序需达到125MHz,而I/O延时较大,所以对pipe_clk进行了相位偏移,从而完成时序约束。本文实验中,将控制器配置模拟成U盘,通过USB电缆与PC主机进行通信,调试中使用USB分析仪进行分析,并完成U盘枚举、识别和文件读写操作。

7 结束语

本文实现了可配置的低功耗USB 3.0设备控制器IP设计方案。在可配性上,通过宏定义和寄存器进行IP配置,使IP具有可重用性强、应用范围广等优点。在低功耗设计上,通过门控时钟技术减少空闲逻辑的动态功耗;利用门控电源技术,在挂起模式下断开控制器电源,最大限度地降低功耗。实验数据表明,采用这2种低功耗策略能大幅度降低控制器功耗。然而在服务周期间隙,USB没有进行数据传输,处于空闲状态,如何降低该期间的动态和静态功耗将是下一步需要研究的内容。

[1]USB Implementers Forum,Inc..USB Specification[EB/OL].[2014-12-05].http://www.usb.org/developers/docs/.

[2]张建民,李思昆,黎铁军.可配置总线接口USB控制器IP核的设计与实现[J].微电子学,2004,34(6):640-643.

[3]The SPRIRIT Consortium.SPIRIT 1.4Specification[EB/OL].[2014-12-05].http://www.accellera.org/XMLSchema/SPI RIT/1.4.

[4]索晓杰,翟正军,姜红梅.USB 3.0协议分析与框架设计[J].计算机测量与控制,2012,20(8):2233-2253.

[5]徐 进.USB3.0数据链路层的设计与验证[D].杭州:杭州电子科技大学,2011.

[6]陈宏铭,程玉华.基于AHB总线的USB 3.0设备控制器IP核设计[C]//第9届中国通信集成电路技术与应用研讨会论文集.苏州:中国通信学会,2011.

[7]Advanced RISC Machines.AMBA Specification[EB/OL].[2014-12-05].http://www.arm.com/zh/products/systemip/amba/amba-open-specifications.php.

[8]Teoh T H,Sarwar Z,Mohd Z A.A Power Efficient USB 2.0Device Controller Architecture and Its Implementa-tion [C ]//Proceedings of International Symposium on Con-sumer Electronics.Singapore:IEEE Press,2011:388-392.

[9]黄凯杰,黄 凯,马 徳,等.基于IP-XACT标准的SoC集成方法[J].浙江大学学报:工学版,2013,47(10):1770-1777.

[10]吴从中,彭 乐,王亚君,等.USB3.0设备控制器IP核OUT端点测试平台的研究与实现[J].电子测量与仪器学报,2012,26(7):646-650.

[11]尹夕振.USB 3.0设备控制器IP核IN端点的功能验证[D].合肥:合肥工业大学,2011.

[12]潘 赟.CK-CPU 嵌入式系统开发教程[M].北京:科学出版社,2011.

[13]四川和芯微电子股份有限公司.USB3.0PHY[EB/OL].[2014-12-05].http://www.ipgoal.com/shop/?type=detail&id=340&classid=19&classid2=0#Menu=Child Menu19.

[14]S2C.V6TAI Logic Module[EB/OL].[2014-12-05].http://www. s2cinc. com/product/HardWare/V6TAILogic Module.htm.