基于FPGA的增量式光栅信号采集系统设计

2014-12-23周云飞周柔刚

涂 骁,周云飞,周柔刚,梁 涛

(华中科技大学 机械科学与工程学院,湖北 武汉430074)

0 引 言

在100nm 的步进扫描光刻机中,要求硅片台和掩膜台的定位精度小于10nm,对于粗动台而言其精度也要达到μm 级别[1,2]。目前,工作台的位置和速度信息的获取主要由高精度的增量式光栅尺来测量。而工作台高精度位置速度信息的获取仅靠光栅尺本身的物理测量还远远不够,更需要建立一套高速实时有效的增量式光栅尺信号采集系统,以实现数据的准确采集和快速上传。

针对上述要求,本文设计了一种基于FPGA (现场可编程门阵列),能实现增量式光栅信号高速实时采集的系统。以RS485为接口,建立增量式光栅尺信号的高速采集通道,利用FPGA 实现光栅信号的处理逻辑和光纤数据传输的控制逻辑,并以双模光纤作为传输媒介,将数据高速上发给上位机控制系统。

本系统传输速率高、距离长、抗干扰能力强,且具有良好的拓展性。

1 系统整体结构设计

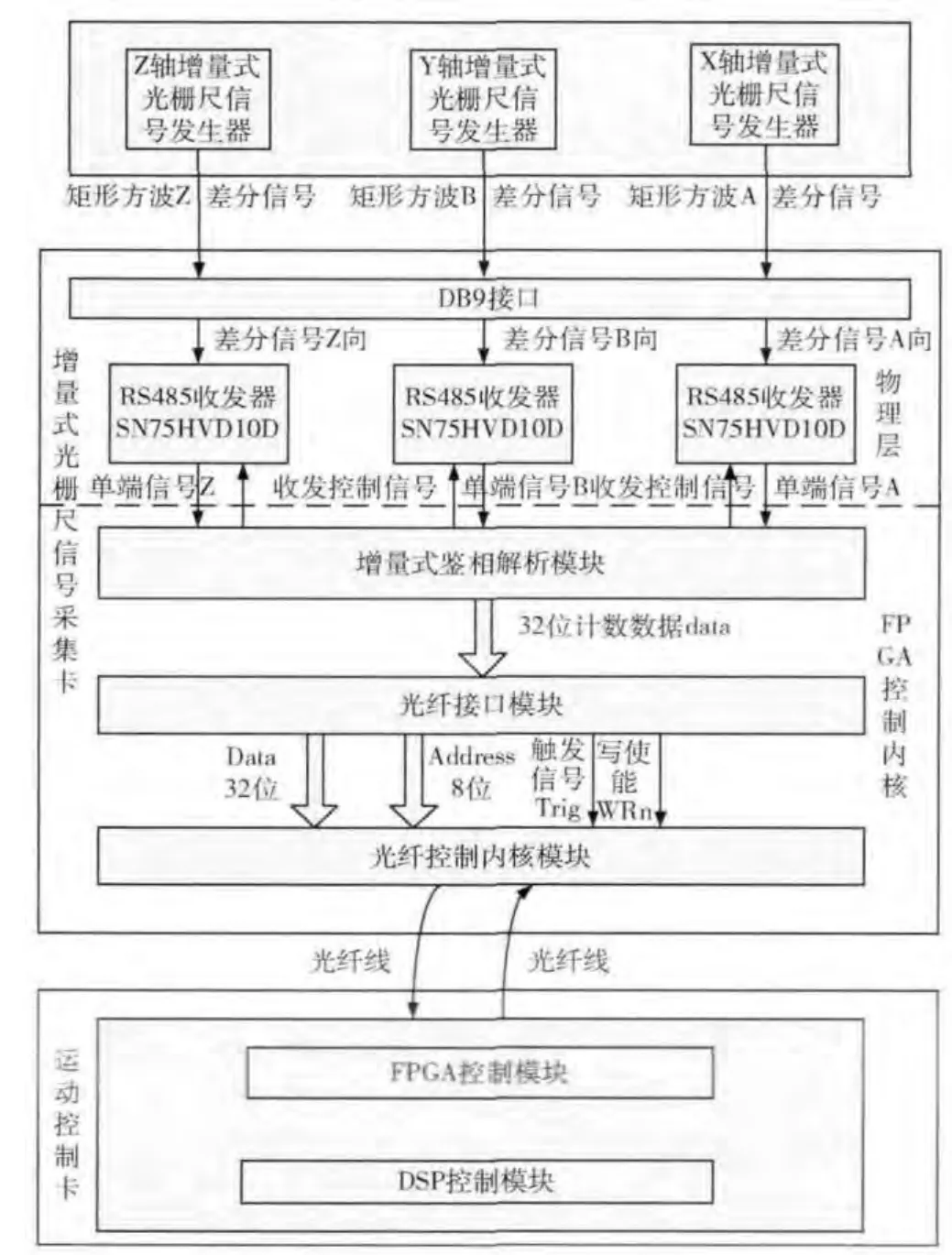

增量式光栅尺数据采集系统结构如图1所示。该结构涵盖了从光栅尺信号输入端到输出端的系统的整体构架。包括DB9接口、RS485收发器、FPGA 内部的增量式鉴相解析模块、光纤接口模块、光纤控制内核模块。其主要功能说明如下:

(1)DB 9接口:该接口共9根引线,选取该接口是为了和增量式光栅尺的输出接口配套。

(2)RS485 收发器:本系统选取的RS485 收发器为SN75HVD10D。该芯片支持差分信号输入输出,实现差分与单端信号的相互转化,具有较好的抗干扰能力。本系统是作为光栅信号的接收端,故只需通过FPGA 设置该芯片为接收模式。

(3)增量式鉴相解析模块:该模块由FPGA 实现,主要将接收的A、B 脉冲进行鉴相比较,然后将比较的结果计数上传。若A 脉冲超前B脉冲90度,则计数器加1,反之,则计数器减1[3]。计数器的值代表具有相位关系的AB脉冲的个数,表征光栅尺运动轴相对移动位置。

(4)光纤接口模块:该模块主要实现数据的采集缓冲和存储时序逻辑。

(5)光纤控制内核模块:该模块是本系统最核心模块,主要实现数据的发送与接收逻辑,光纤通信协议的控制逻辑,包括数据的成帧与解帧,8B10B 编码与解码等。负责与上位机的光纤通信控制。

图1 增量式光栅数据采集卡结构

2 增量式光栅信号采集原理

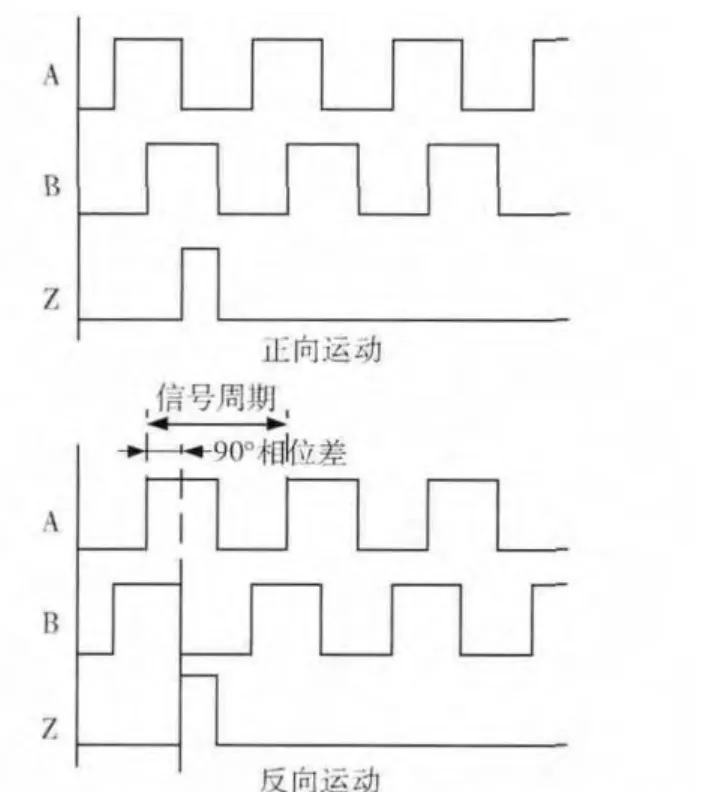

在机械结构上,增量式光栅尺由动尺和定尺2部分组成。动尺在定尺上移动的过程中产生脉冲序列:A 脉冲、B脉冲、Z脉冲[4]。3种脉冲包含了动尺的运动位置、速度和方向信息。其中,A、B脉冲包含了动尺相对于定尺的移动距离和方向信息,Z 脉冲表征了动尺在光栅尺中点和两端点的信息[5]。

增量式光栅尺信号的输出方式有TTL 输出方式和EIA422A 输出方式。其中,TTL 输出方式易产生共模干扰,且传输距离较短;而EIA422A 输出方式属于差分传输方式,则抗干扰能力强,且传输距离相对较长[6]。本系统采用EIA422A 方式传输。

对于每个时钟周期,输出A 脉冲与B脉冲的相位始终相差90°。当A 脉冲相位超前B脉冲90°时,表示动尺相对于定尺正向移动;反之,若A 脉冲相位滞后B脉冲90°,则意味着动尺相对于定尺反向移动[7],如图2所示。由于光栅尺动尺相对于定尺每移动一个栅距,光栅尺就输出一个A、B、Z脉冲。因此通过在一定时间内,计算采样的AB 脉冲数,就可以准确换算出动尺对定尺的相对位移。本系统本质上就是实现对AB脉冲数的采集以及AB相位判断。

图2 A、B、R 脉冲相位

3 增量式光栅尺信号控制逻辑的FPGA实现

3.1 增量式鉴相解析模块

该模块是FPGA 控制逻辑中的信号处理端,主要实现脉冲的相位鉴定和脉冲计数。其结构包含光栅尺信号缓冲器、滤波去抖模块、鉴相比较模块、32位可逆计数器和时延去抖模块,如图3所示。

(1)光栅尺信号缓冲器:由于传输线路阻抗不匹配或者焊接存在虚焊等,有可能使得A、B、Z 三路信号不稳定,因此在接口端需要一个缓冲器,将数据锁存延时,待稳定之后再下发给下一模块。本系统经实验验证将数据锁存2个节拍可满足要求。

图3 增量式鉴相解析模块结构

(2)滤波去抖模块:由于采用的是DB9接口,不具有信号屏蔽功能,信号传输时可能会引入噪声;同时光栅尺的动尺在运动时因意外出现的抖动也会反映在输出信号中;另外,采集卡硬件设计的缺陷等都会引入噪声,因此建立滤波去抖模块很有必要。该模块滤波去抖原理如下:本系统的采样时钟为125 M,当信号在连续3个时钟周期内检测的电平为高或者为低,则认为该信号有效;反之,若该信号在连续的3时钟周期内检测的电平出现高低跳变,则认为该信号中存在毛刺,为无效。通过上述方法可以滤除一定频率范围噪声,不能滤除全部噪声,但实验证明对于本系统已经足够。

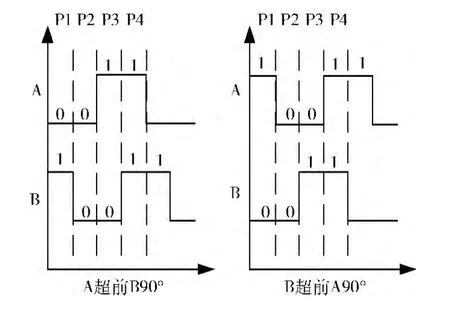

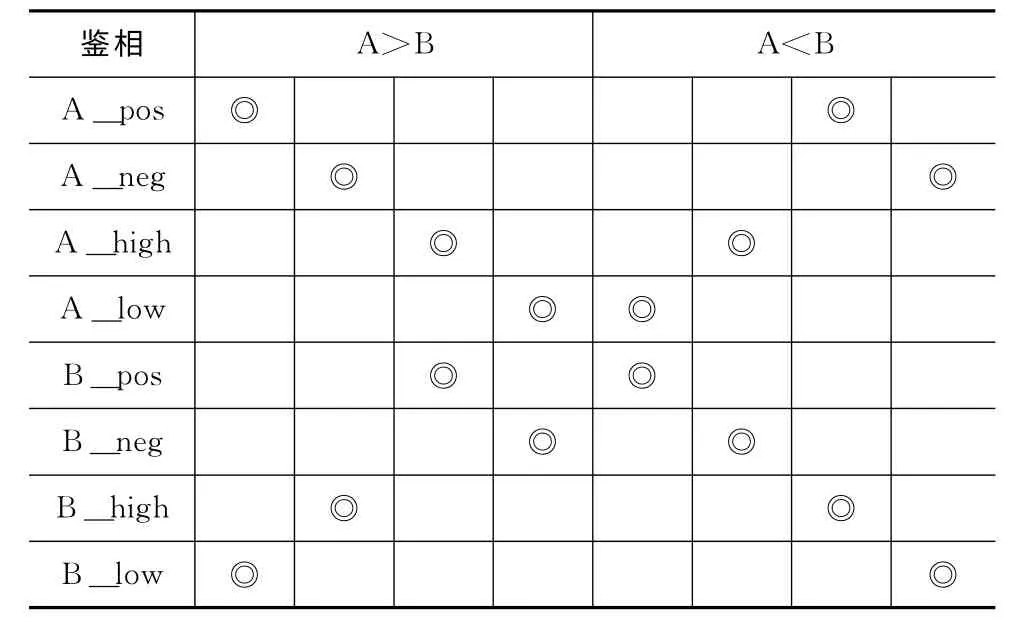

(3)鉴相比较模块:该模块主要实现A、B 脉冲的相位判定。在一个信号周期内,AB脉冲的电平变化如图4所示。当A 脉冲超前B 90°时:A、B的电平变化为00→10→11→01;当A 脉冲滞后B 90°时,A、B的电平变化为00→01→11→10,通过检测AB的电平变化,可以判定A、B脉冲的相位[8,9]。本文采用的脉冲检测法:即通过在A 或B脉冲边沿时,检测B或A 的电平状态来判断两者的相位关系,如表1所示:其中A_pos、A_neg、A_high、A_low、A>B、A<B、◎分别是A 脉冲上升沿、下降沿、高电平、低电平标志位、A 超前B900、A 脉冲滞后B 脉冲900、该状态有效 “1”;B同上。当A_pos=1,B_low=1时,可以确定A 脉冲超前B 脉冲900,其它状态按照表1依次类推,最后将A 超前B或B超前A 的各个状态分别求或,即可判定AB的相位关系。

图4 A、B脉冲相位比较

表1 A、B鉴相状态图

(4)32位可逆计数器:当计数器收到A 超前B 脉冲90°的标志信息时,则加1;反之,则减1。由于采用的是32位二进制计数器,且时钟为125 M,那么该计数器会出现多位同时翻转的情况,这样会产生干扰脉冲,出现竞争冒险,使得计数数据出现不稳定甚至错误。对于该情况,一般可以采用格雷码计数器,因为格雷码计数器不存在多位同时翻转的情况,就不会引入噪声,但是该计数器数据需要转化成二进制后才便于直观的读取,且增加了编写难度[10]。本系统利用D 触发器的D 输入端对毛刺信号不敏感的特点,在可逆计数器后面,用2级D 触发器锁存,待数据稳定后,再上传。该功能由时延去抖模块完成。实验证明此方法可行有效。

3.2 光纤接口模块

光纤接口模块主要用于接收各类传感器信号,按照一定的逻辑时序传给光纤控制内核,为数据存储提供接口。该模块包括32位数据接收端口、信号缓冲器、数据发送端口3部分,如图5所示。其中当32位数据接收端口接到来自光纤内核的触发信号时,就开始进行数据接收,传给信号缓冲器,待数据稳定之后,传到数据发送端口,该端口将数据及地址和写使能信号按照DPRAM (双口RAM)的存储时序,发送至光纤控制内核的发送DPRAM 存储,当数据存储完毕后,数据发送端口会向光纤控制内核中的发送控制器发送触发启动信号,表示发送控制器可以启动数据读取,开始工作。

图5 光纤接口模块结构

该光纤接口模块可以将多种传感器信号,按照一定的存储时序下发给控制内核中的DPRAM,具有良好的扩展性。

3.3 光纤控制内核模块

3.3.1 数据帧格式定义光纤通信链路中数据按照一定的帧格式定义,目的是为了保证数据在传输的过程中不出现失帧、丢帧错误[11]。而繁杂的数据帧定义能够提高数据的稳定性,但是增加了FPGA 逻辑资源开销。为了减小FPGA 的开销且保证数据传输的稳定性,本文简化了帧格式定义,如图6所示。

图6 数据帧格式定义

一个完整的数据帧包含开始帧SOF、帧头、帧头检验、实际数据、同步字符、数据和校验和结束帧EOF。其中,开始帧SOF表示新的一帧的开始。帧头共4个字节:第一个存放当前帧包含的数据个数,即帧长;第二个存放当前帧的起始地址,当接收数据帧时,数据域中的长字将逐字存放到目标模块中从该地址开始的一系列连续的空间中;第三字节未使用;第四字节存放发送模块对接收模块的控制信息,当控制信息中指定位被置1后,目标模块将被复位。和校验就是帧头或数据中所有字节之和,是保证数据传输正确的重要方式。同步字符SYNC用于数据帧的填充,作为接收端字对齐的标志,若接收端检测到该字符在数据边界,表明该帧中数据边界对齐,反之,则通过重新调整恢复时钟与字边界的相位关系,来调整数据边界,虽然当前的数据被缩短或延长,数据出现损坏,但同步字符之后的数据又重新对齐了字边界。

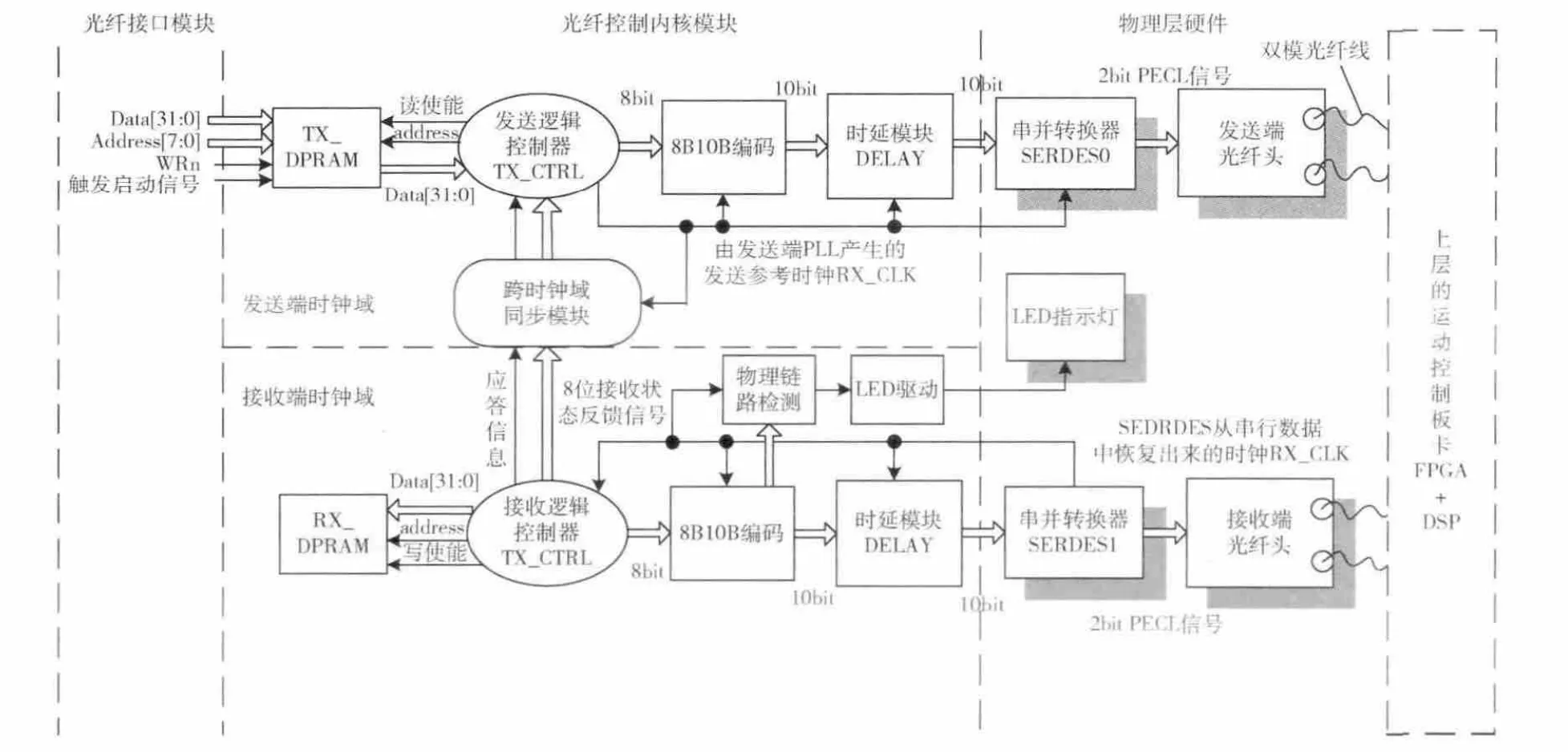

3.3.2 光纤控制内核结构

光纤控制内核模块是整个系统中的核心模块,主要实现数据的接收与发送控制逻辑,光纤通信协议解析,主要包含通信的物理层和传输层。其中物理层由光纤头、串并转换器和LED 指示灯组成,实现编码数据的串并转换、光电转换、时钟倍频、时钟提取、错误显示,为高速实时通信提供物理支持;传输层由FPGA 实现,包含时延模块、8B10B编码解码模块、物理链路检测模块、LED 驱动模块、发送接收控制模块、发送端接收端DPRAM 和跨时钟域同步模块。各个模块协调工作,完成数据的组帧与解帧,编码与解码,发送与接收。

光纤控制内核结构如图7所示。

图7 光纤控制内核结构

(1)串并转换器 (SERDES):本系统采用的SERDES为TLK1221芯片,最大支持1.3Gbps传输速率。发送端,SERDES用高速时钟调质编码数据流,将接收的10bit的并行数据以PECL 差分信号串行输出,为长距离传输提供电平支持;接收端,SERDES主要从数据流中恢复出时钟信号,并解调还原数据。

(2)8B10B 编码解码模块:8B10B 编码是一种将8bit元数据通过运算编码为10bit的算法,其特点为编码后的数据没有5个长的连 “0”或连 “1”串,因为连 “0”或连“1”串所含的数据信息量小,不利于驱动参考时钟与数据随路时钟对齐,会造成恢复时钟的抖动或漂移。8B10B 解码的过程与编码相反,主要将10bit数据恢复成8bit元数据。8B10B的编码方式已经标准化,这里不再详述[12]。

(3)物理链路检测模块:该模块实现对光纤线路通信状态的实时监测,其原理为:数据帧中会插入同步字符,当光纤正常传输时,数据帧中相应位置会有同步字符,该模块通过在一定时间内检测到同步字符,来判断光纤正常,并将正常标志位传给LED 驱动器,以驱动相应LED 显示;反之,若在一段时间未在指定地方检测到同步字符,则判定光纤物理连接错误,并报以LED 指示。

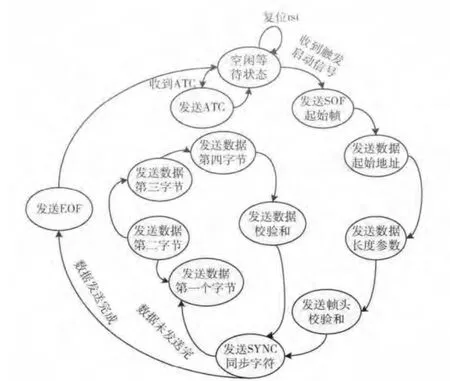

(4)发送逻辑控制器 (TX_CTRL):当收到触发启动信号后,TX_CTRL开始按照读时序,从发送DPRAM 中读取数据,然后按照定义的数据帧的格式,每8位为一组发送,当发送结束帧EOF时表示一帧已经发送完毕,返回到等待状态,等待下一次的触发。在数据帧中插入了同步字符SYNC,便于接收端的字对齐。另外,当TX_CTRL接收到来自接收控制器的反馈信息应答帧ATC 时,表示接受端数据接收完毕,则TX_CTRL 将该信息反馈至上位机。其跃迁状态如图8所示。

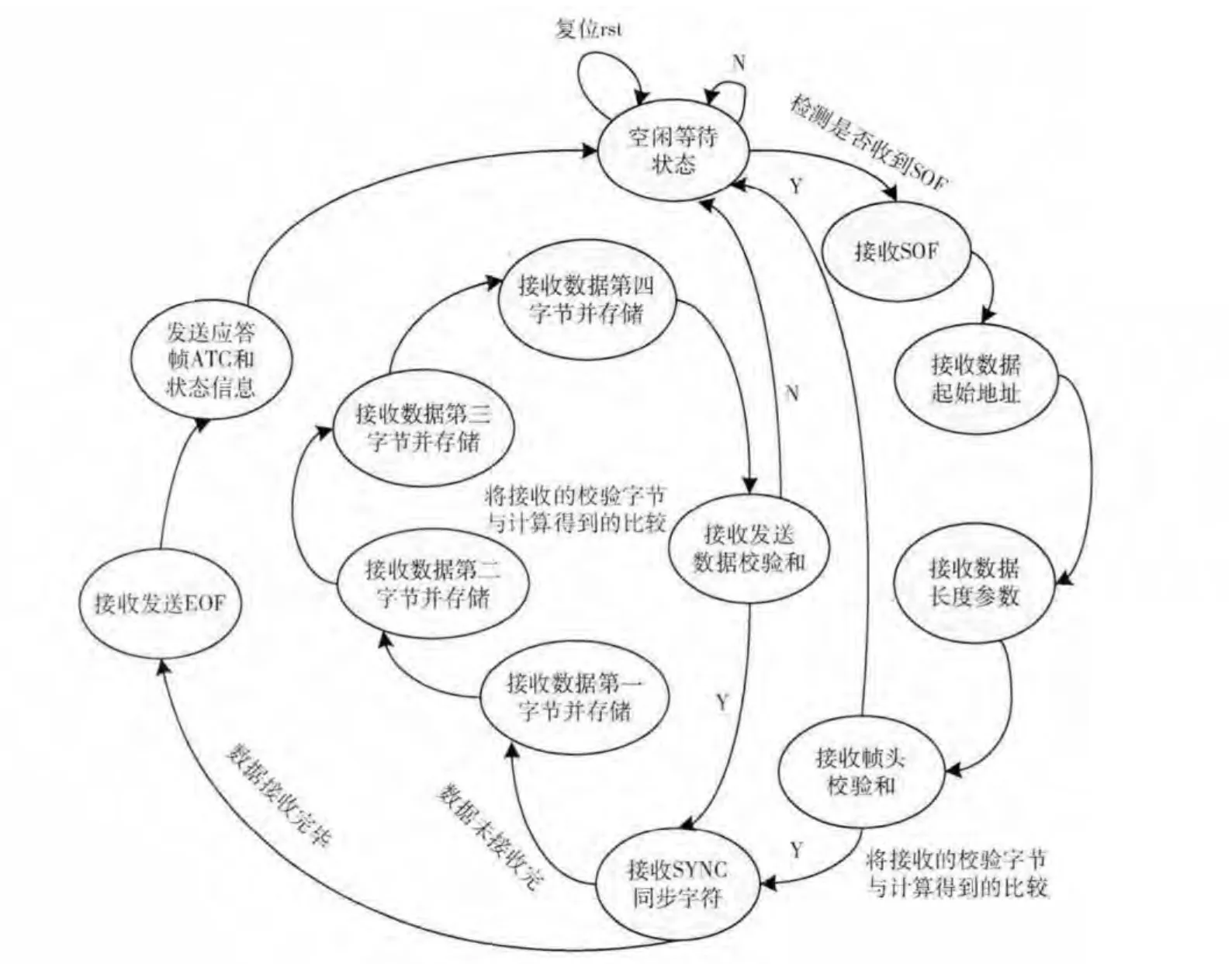

图8 发送控制器状态跃迁

(5)接收逻辑控制器RX_CTRL:接收控制器在恢复时钟的节拍下将串行的数据流经过8B/10B译码接收,将校验正确的数据保存到接收DPRAM 中,同时产生应答信号ATC,反馈给发送控制器,途中经过跨时钟域同步模块,即经过双D 触发器串联缓冲,可减少亚稳态。当检测到SOF字符表示一帧开始,然后按照数据帧的格式每8位一组接收数据,数据正确,则存储到DPRAM 中,当检测到EOF字符表示一帧结束,此时发出应答帧ATC 表示该帧数据接收完毕,其跃迁状态如图9所示。

图9 接收控制器状态跃迁

4 光栅信号采集系统实验验证

本实验旨在验证该增量式光栅信号采集系统的可行性与可靠性。实验原理如下图所示:增量式编码器连续产生相位差为90°脉冲信号A、B,以此作为信号源,光栅信号采集卡连续采集该信号,并将计数数据通过光纤线以1.25 Gbps速率上传到运动控制板卡中DSP的相应的寄存器中,然后通过CCS开发软件实时观测数据变化,如图10所示。由于信号源按照一定频率连续上传,那么计数器的数值会等差递增或者递减,在code composer studio DSP开发软件中观测的计数值相对于时间的函数则是一条递增或递减的直线,如图11所示,经过长时间测试,直线稳定,表明本采集系统可行可靠。

图10 实验原理连接

图11 实验结果

5 结束语

为了实现增量式光栅尺精确定位,设计了基于FPGA的光栅尺信号的高速采集系统,该系统具有如下特点:

(1)利用FPGA 实现增量式光栅脉冲信号的相位鉴别和4倍频脉冲计数,125 M 的采样时钟满足系统采样速度要求;

(2)定义了光纤传输数据帧格式,增强了数据传输的可靠性和容错性;

(3)设计了光纤控制内核结构,采用TLK1221芯片实现数据流的串并转换和1.25G 的高速光纤传输;同时,发送接收控制模块的设计,控制数据流流向,实现光栅数据采集卡与上位机控制卡的信号交互的逻辑控制。

该系统已在100nm 光刻机中得到应用,且具有较好的扩展性。

[1]CHENG Xin,ZHOU Yunfei.Design of parallel computing architecture for multi-axis ultra-precise synchronous motion control [J].China Mechanical Engineering,2011,22 (18):2156-2161 (in Chinese).[程鑫,周云飞.针对多轴精密同步运动控制的并行计算架构设计 [J].中国机械工程,2011,22(18):2156-2161.]

[2]CHENG Xin,ZHOU Yunfei,HU Yongbing,et al.Synchronous measurement and control mechanism based on high-speed fiber channel link [J].China Mechanical Engineering,2011,22 (19):2325-2330 (in Chinese). [程鑫,周云飞,胡永兵,等.基于高速光纤链路的同步测控机制 [J].中国机械工程,2011,22 (19):2325-2330.]

[3]WEI Jie.Design and implementation of raster data acquisition card based on USB [D].Baoding:Hebei University,2008(in Chinese).[魏杰.基于USB接口的光栅数据采集卡的设计与实现 [D].保定:河北大学,2008.]

[4]YUAN Xiangrong,TIAN Xincheng.Application of grating encoder in CNC system for indexable inserts peripheral grinding[J].Instrument Technique and Sensor,2013,43 (8):18-20(in Chinese).[袁向荣,田新诚.光栅编码器在可转位刀片周边磨削数控系统中的应用 [J].仪表技术与传感器,2013,43(8):18-20.]

[5]DU Yingcai,WANG Xijun,WANG Shujie.Auto-detection system of incremental encoder[J].Journal of Electronic Measurement and Instrument,2012,44 (11):993-996 (in Chinese).[杜颖财,王希军,王树洁.增量式编码器自动检测系统 [J].电子测量与仪器学报,2012,44 (11):993-996.]

[6]XIAN Hao,REN Aizhi.Incremental encoder data acquisition[J].Journal of north China Institute of Technology,2008,12(2):33-36 (in Chinese).[鲜浩,任爱之.增量式编码器数据采集 [J].华为工学院学报,2008,12 (2):33-36.]

[7]LIN Yisong,TANG Zhaohong,QU Ruixiang.Design of incremental grating interface module in the numerical control equipment[J].Tool Engineering,2006,40 (3):126-127 (in Chinese).[林一松,汤兆红,区锐相.数控设备中增量式光栅尺接口模块设计[J].工具技术,2006,40 (3):126-127.]

[8]YANG Linnan,LI Honggang,ZHANG Lilian.Design of high speed multichannel data gathering system based on FPGA [J].Computer Engineering,2007,33 (7):246-249 (in Chinese).[杨林楠,李红刚,张丽莲.基于FPGA 的高速多路数据采集系统设计 [J].计算机工程,2007,33 (7):246-249.]

[9]PI Daijun,ZHANG Haiyong,YE Xianyang.Design of high speed real-time data acquisition system based on FPGA [J].Modern Electronics Technique,2009 (6):12-15 (in Chinese).[皮代军,张海勇,叶显阳,等.基于FPGA 的高速实时数据采集系统设计[J].现代电子设计,2009 (6):12-15.]

[10]LI Li.A gray code counter based on FPGA [J].Science Technology and Engineering,2009 (23):25-29 (in Chinese).[李莉.基于FPGA 的多位格雷码计数器 [J].科学技术与工程,2009 (23):25-29.]

[11]WANG Yao.The multi-processor motioncontrol card based on VME bus[D].Wuhan:Huazhong University of Science and Technology,2012 (in Chinese). [王耀.基于VME 总线的多处理运动控制卡 [D].武汉:华中科技大学,2012.]

[12]ZHONG Jianfeng,HU Qingsheng.The design of High-speed serial to parallel converter based on FPGA [J].Chinese Journal of Electron Devices,2008,31 (2):657-660 (in Chinese).[仲建锋,胡庆生.基于FPGA 的多路高速串并转换器设计 [J].电子器件,2008,31 (2):657-660.]