1553B总线网络中RT终端系统的软件设计

2014-12-18张启敏孙剑波权云涛

张启敏,孙剑波,权云涛

(1.西安电子科技大学电子工程学院,陕西西安 710071;2.山东航天电子技术研究所通信事业部,山东烟台 264670)

MTL-STD-1553B是一种数字时分制指令/响应型多路传输数据总线,简称1553B总线,它最早是由美国军方专为飞机设备指定的一种信息传输总线标准。由于1553B总线具有双向输出、实时性高、可靠性高、抗干扰能力强和易于维护扩充等特点,被广泛应用于舰船、航空和航天等领域。在我国的航空航天领域,1553B总线主要应用于主控系统对子系统的状态信息获取和状态控制。目前,比较常用的是DDC公司的总线芯片,该公司生产了一系列总线芯片,如:BU-65170、BU-61580和 BU-61585是组成处理器与MIL-STD-1553B总线通信接口的重要组成部分。

1 系统概述

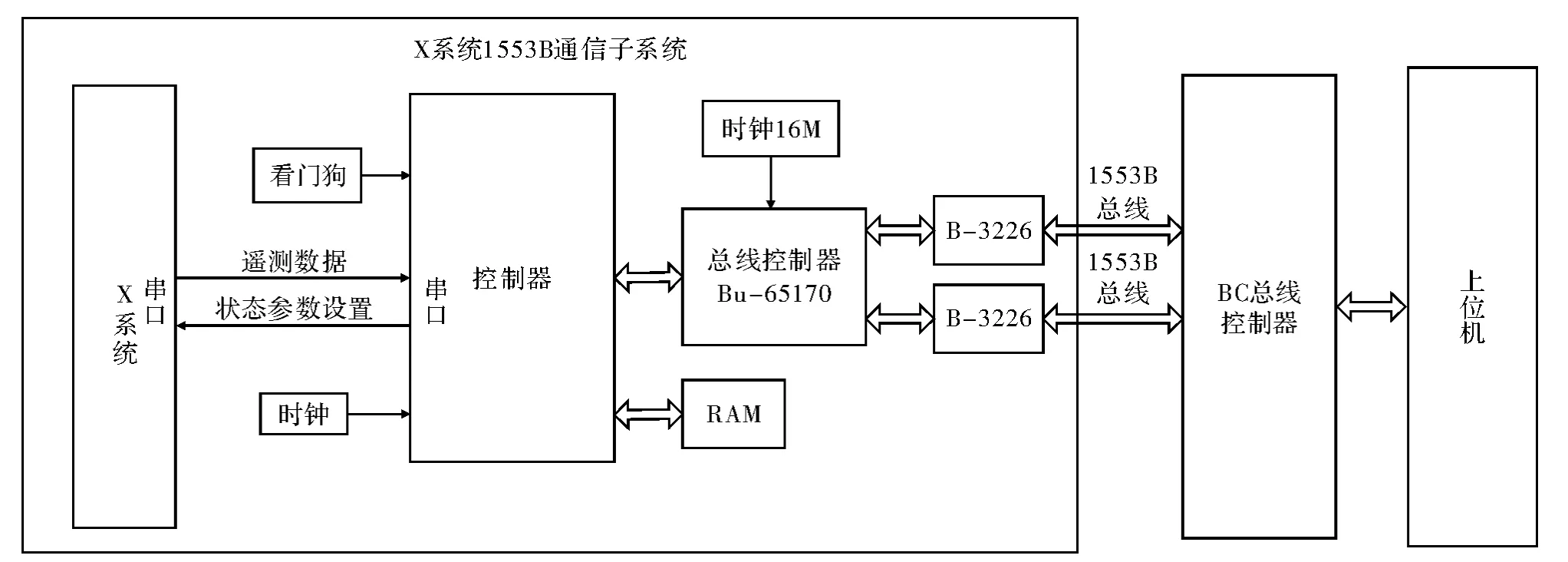

如图1为系统示意图,X系统1553B总线通信子系统是1553B总线网络中的一个RT终端系统。在总线系统中,X系统是一个需要被测控的子系统。X系统1553B总线通信子系统能够接收、解析和执行来自BC总线控制器的各项命令。同时,RT端控制器与X系统之间通过RS232串口进行通信,实现获取并存储X系统遥测数据和转发BC总线控制器命令的功能。此1553B通信系统中,BC总线控制器的指令主要有:遥测指令、遥控指令、上注指令、勤务指令和方式代码指令等,并且周期性的发送遥测指令与方式代码指令、不定周期发送上注指令、方式代码指令和勤务指令,RT终端系统对各项命令都进行反馈,上位机软件提取反馈的信息,实时监测X系统的状态和1553B总线状态。

2 RT系统软件设计与实现

2.1 软件设计与实现

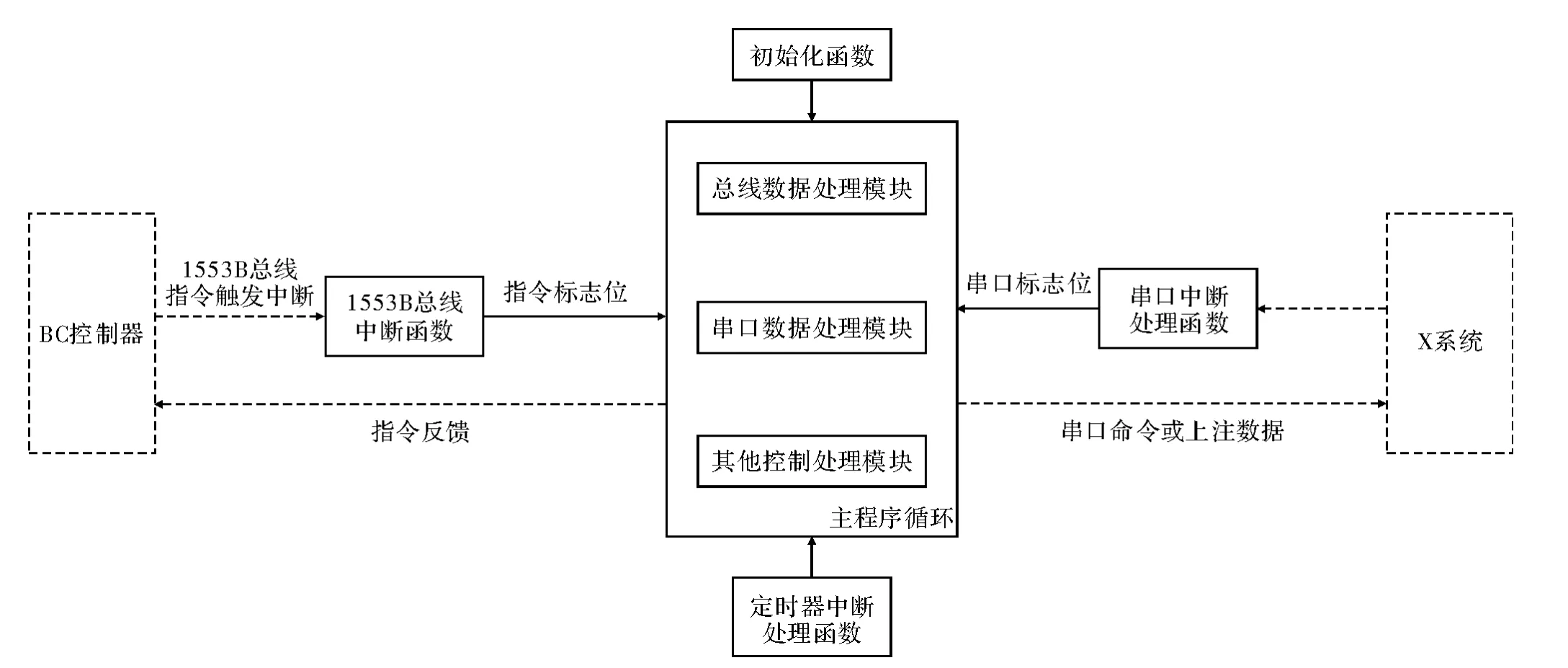

软件的模块设计示意图,如图2所示。软件进行模块设计,划分为初始化模块、总线中断模块、串口中断模块、定时器中断模块和主循环模块。

图1 系统示意图

图2 软件设计示意图

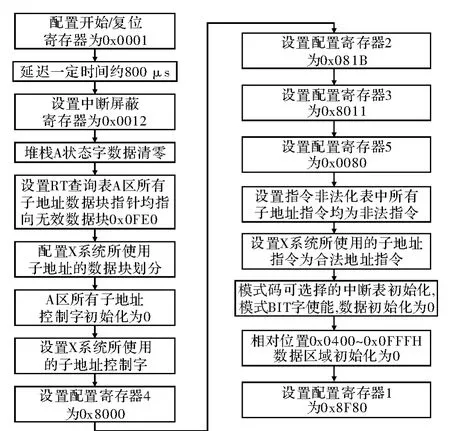

图3 总线芯片初始化步骤图

微控制器对1553B总线芯片的初始化需要遵循寄存器配置的顺序,当配置RT为增强使能模式,总线芯片的初始化步骤,如图3所示。其中,配置开始/复位寄存器为0x0001实现软件复位;配置中断屏蔽寄存器为0x0012,使能RT子地址控制字EOM中断和 RT模式码中断;配置寄存器4为0x8000,使能外部BIT字;配置寄存器2为0x081B,使能“写覆盖无效数据”、中断状态自动清除、电平中断请求、增强型RT存储器管理、分离广播数据;配置寄存器3为0x8011,使能“增强模式”、禁止非法的RX传送、增强型模式码处理;配置寄存器5为0x0080,使能“禁止广播”;配置寄存器1为0x8F80,使能增强RT模式、清除动态总线控制位、清除忙位、清除服务请求位、清除子系统标志位以及清除RT标志位。

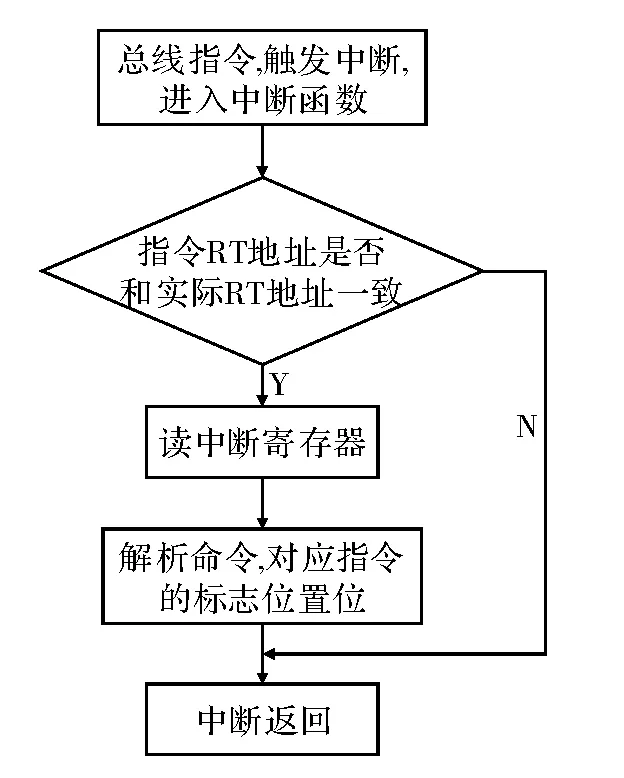

实现总线中断函数时,首先对接收到的指令数据中RT地址与实际RT地址进行对比判断。判断成功后,读取中断寄存器,解析总线指令。在总线中断函数中不进行数据处理,仅对相应指令的标志位置位,如图4所示。

图4 总线中断函数流程图

本系统采用8位微控制器为小尾端处理器体系架构,而BC总线控制器采用大尾端模式的SPARC体系结构,总线芯片BU-65170工作于8位缓存模式,RT端向1553B主总线缓冲区存储待发送数据时,应该依据大尾端方式来排放字节数据。同时,在8位操作模式的微控制器对BU-65170寄存器进行读操作时,先读高字节,再读低字节,之后再读高字节和低字节,即需要连续读操作两次,才能够读出寄存器的状态值;写操作时,仅写入一次即可。

2.2 系统软件安全可靠性方面的考虑

保障系统软件的安全与可靠,可以从提高软件的容错和纠错能力着手,逐项提出与分析了以下方法措施,包括:(1)初始化总线芯片时,程序配置开始/复位寄存器后,需要进行约800μs的延迟,保证1553B总线芯片复位操作充分完成。(2)初始化时,程序对未使用子地址的读/写数据块指针设置为0xFE0,将指针明确指向一个不使用的数据块地址。同时,未使用的子地址控制字均赋值为0。此措施防止程序对未使用子地址的误操作,提高软件对误操作的容错能力。(3)初始化时,程序需要对总线芯片的全部数据区域进行初始化,数据初始化为0,防止误操作得到未知的数据,防止未知数据对程序运行造成影响。(4)对于总线中断函数处理时,对接收到的总线指令中RT地址与实际RT地址进行对比判断,防止系统接收到其他RT终端的总线指令而造成误操作,增强该RT系统的容错能力。(5)为避免遗漏总线中断,缩短总线中断函数的执行时间,在总线中断函数处理中,程序对总线数据不进行处理,仅对相应总线指令的标志置位。(6)初始化时,对1553B总线芯片的RAM区域进行自检,检测RAM区域能否使用,自检出错,则启用备用RAM芯片,提高系统的纠错能力。(7)系统运行过程中,实施定时刷新操作,即在定时时间内未能接收到总线中断,则进行总线芯片重新初始化,提高芯片的自我纠错能力。

3 系统软件验证

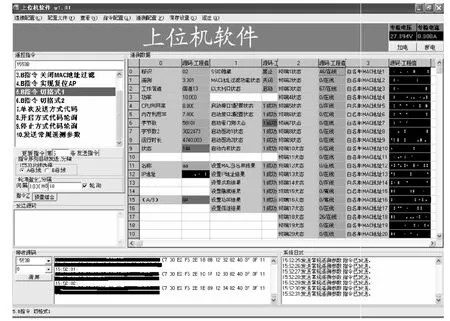

X系统1553B总线通信子系统软件是否能够正常稳定运行,通过RT终端与BC总线控制器相连实现遥测和遥控等功能进行验证。BC总线控制器向RT终端系统发送各项总线指令,能够实现获得系统遥测信息、控制系统状态和监测总线状态等一系列功能。如图5所示,BC总线控制器接收到的反馈信息数据帧经过上位机解析,将X系统的运行状态信息显示到上位机软件界面,各项状态信息显示X系统运行正常,并且遥测状态量和X系统实际工作状态一致,证明X系统1553B总线通信子系统及系统软件运行正常,其中对部分状态信息进行了隐藏。

图5 X系统运行状态

4 结束语

本文对1553B总线网络中RT终端系统软件的设计与实现进行了详细说明,重点对提高RT终端系统软件容错能力和纠错能力的措施进行了分析,这些措施在一定程度上提高了系统软件的安全性和可靠性,保障了系统安全稳定地运行。经过系统验证,X系统1553B总线通信子系统及系统软件运行稳定,并且已成功应用于某型项目中。目前,系统运行状态良好。

[1]赵月琴.基于BU-61580的嵌入式1553B终端设计[J].航空兵器,2004(4):28-31.

[2]郭坚,付连芳,王海涛.基于8051微控制器的1553B总线接口设计[J].计算机测量与控制,2006,14(7):946 -949.

[3]DDC.ACE/Mini- ACE series BC/RT/MT advanced communication engine integrated 1553 terminal BU-65170 user's guide[M].USA:DDC,2005.

[4]DDC.MIL -STD -1553A/B notice 2 RT and BC/RT/MT advanced communication engine[M].USA:DDC,1999.

[5]马忠梅,刘滨,戚军,等.微控制器C语言Windows环境编程宝典[M].北京:北京航空航天大学出版社,2003.

[6]凌志华,谭立英,陶坤宇.基于BU-65170的1553B终端设计[J].微计算机信息,2008,24(2):273 -274.

[7]旷文聪,姜运生.基于BU-61580的1553B航空通讯总线设计[J].电子技术,2008,45(12):14 -20.

[8]王好同,贾会甫,高瑞乾.基于BU-61580的MIL-STD-1553B远程终端设计[J].海军航空工程学院学报,2008,23(4):439-441.