基于SEC-DED的抗SEU星载MIMO检测算法

2014-12-10王大鸣

高 山,王大鸣

(信息工程大学,河南 郑州 450002)

目前国内外研究机构都针对卫星LTE体制展开了广泛研究,2011、2012年韩国和我国分别向 ITU组织提交了基于LTE通信体制的卫星移动通信系统标准化草案,标志着LTE通信体制将成为未来卫星移动通信的主流通信体制。MIMO作为LTE通信体制的核心技术之一,能够提高频谱利用率,增大系统容量[1],然而将MIMO检测应用于星上设计面临星上资源受限和易受空间辐照影响两项难题,需寻求低开销抗SEU的MIMO检测算法。

星载平台算法层面上的抗单粒子翻转设计主要有ABFT(Algorithmic-Based Fault Tolerance)[2]和RPR(Reduced-Precision Redundancy)[3]。ABFT设计在矩阵阶数较小时资源占用率高,且增加了处理时延。RPR设计降低了资源占用率,有良好的抗辐射性能,但会降低数据精度。硬件层面上抗SEU(Signal Event Upsets)的方法主要有擦洗、纠错编码、动态重构等,其中应用最为广泛、最为有效的是TMR技术,该设计可以检测和纠正错误,但资源占用率高。针对基于TMR架构的MIMO检测算法资源开销大、功耗大的问题,本文在海明校验码[4]的基础上,提出了一种基于SEC-DED(Single Error Correction-Double Error Detection)的抗SEU的星载MIMO检测算法。

1 MIMO检测算法分析

假设MIMO信道矩阵为H,接收信号为y,发送信号为x。则MIMO的系统模型可表示为:

其中,n为信道噪声,功率为δ2,其线性检测算法ZF和MMSE可分别表示为:

由式(2)、式(3)可以看出线性检测算法复杂度为 2M3(M为MIMO的天线数量)。分析其资源占用率高的原因,主要是矩阵的乘积和求逆运算包含大量的乘法运算,以收发天线数量等于2为例,实际使用22个乘法器,每个乘法器占用的实际资源约为(3×N+N2)个LUT(N为数据位宽)[5]。且星载平台采用的抗SEU设计会进一步增加资源占用率。因此本文以降低乘法运算资源占用率为切入点,给出一种基于SEC-DED的抗SEU乘法运算设计,通过降低算法中数乘运算的资源占用率来降低算法整体的资源占用率,并提高抗SEU性能。

2 星载MIMO检测算法设计

SEC-DED星载MIMO检测的乘法算法采用类SEC-DED海明校验码设计,其基本原理是将有效数据按某种规律分成若干组。每组安排1个校验位进行奇偶校验。在1个数据组中加入几个校验位,增大数据代码间的码距,当某一位发生变化时会引起校验结果发生变化,不同数位上的错误会得出不同的校验结果,从而实现检错和纠错。

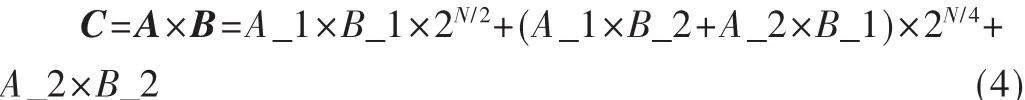

本文将长度为N的数据分隔为等长的两部分,分别记为 A、B,长度为N/2,输出数据记为 C,长度为 2N。由于乘法器资源占用与数据位宽的平方成正比,数据位宽降低一半,乘法器资源节约3/4。同时为实现抗SEU性能,即自检错纠错功能,对乘法器输入数据SEC-DED海明校验设计。将截断的数据分别记为 A_1、A_2、B_1、B_2,由于有效数据位位数为2,按海明校验码设计至少需要 2位校验码, 分别记为 V_1、V_2、W_1、W_2, 其中V_1=A_1+A_2、V_2=A_1-A_2、W_1=B_1+B_2、W_2=B_1-B_2。本设计系统模型如图1所示。

图1 系统模型

2.1 检错

为完成矩阵向量的检错和纠错,引入两个标志量K和 P,定义如下:

判断矩阵向量是否发生错误,只需要判断K和P是否为0,以及K+P是否为0,三者结合可判断出矩阵向量发生错误的数据块位置,以此检测出故障位置,详述如下:

如果K=0并且P=0,则没有错误发生;

如果K=0并且P≠0,则C_4计算过程错误;

如果K≠0并且P=0,则C_3计算过程错误;

如果 K≠0并且 P≠0,则计算 K+P,当 K+P=0时,C_2计算过程错误;当K+P≠0时,C_1计算过程错误。

2.2 纠错

由于只需要保证C_1和C_2计算正确,即只需要在C_1和C_2计算错误时及时纠正即可。在2.1节方式发现故障位置的基础上,用错误的C_1或C_2减去K或者加上P即可获得正确数值。以式(7)为例:

假设计算C_2时,受单粒子翻转影响,其值被错误地计算为5.1,此时:

目前主流的移动应用开发方式可分为Native App、Hybrid App和Web App三种。Hybrid App是Native App和Web App的中庸产物,既具有Native App良好用户体验的特点,又具有Web App跨平台的特性。Hybrid App是一种十分具有潜力的移动应用开发模式,按网页技术与原生应用技术的混合程度可以分为三类:多View混合型、单View混合型以及Web主体型[2]。

由式(8)、(9)可知,K≠0、P≠0 并且 K+P=0,判定 C_2计算错误,则正确的C_2应为 C_2′-K=5.1+0.4=5.5。

由2.1和2.2节可知,如果K或P中有且仅有一个为0,则“校验和”的计算过程中发生错误,乘法器核工作正常,输出结果不受影响,此时可以重新计算一下 “校验和”,并对错误的“校验和”计算模块重构复位;如果K、P都为0时,不需要做任何处理,可视为没有发生单粒子翻转;如果K和P同时不为零,则计算K+P:当K+P=0时,C_2计算错误;C_1正确的计算结果为C_1-K;当K+P≠0时,C_1计算错误;C_1正确的计算结果为C_1-K。

3 性能比较

3.1 资源占用比较

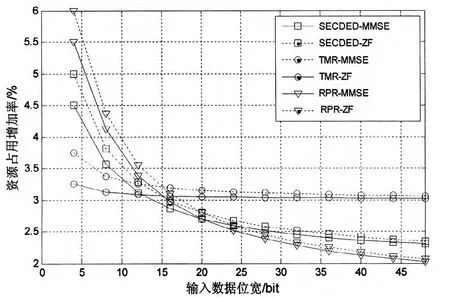

为了验证本文所提算法具有资源占用率小的优势,本文针对 MMSE、ZF两种算法,对不同数据位宽下的3种设计,相比无抗SEU性能算法的资源的占用增加率进行仿真实验,其结果如图2所示。可以看到,基于SEC-DED的MIMO检测算法在数据位宽为12~20时,资源消耗率最低。当数据位宽高于20时,RPR设计资源占用率最低,其主要原因是RPR设计比SEC-DED少使用(N/2)2面积的乘法器资源,但使用较多的移位和加减运算。

图2 MIMO检测算法理论资源占用增加率

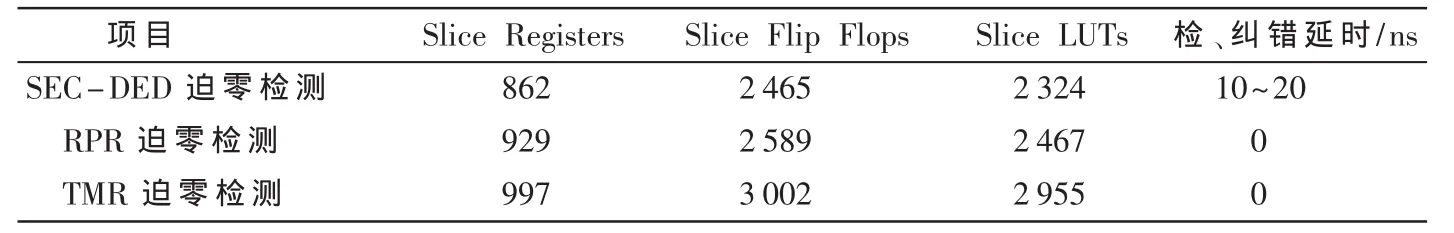

为分析所提算法的实际资源占用率,本文基于Xilinx公司的xc5vlx50t-ffg1136c芯片进行了仿真实验,将基于SEC-DED设计的迫零检测算法与TMR和RPR在资源占用率和抗SEU性能等方面作比较。仿真条件:以线性检测算法ZF为例,收发天线数Nt=Nr=2,调制方式 BPSK,数据位宽16,采用Q11定标法。仿真结果和资源占用情况如表1所示。

测试结果表明:基于SEC-DED设计的ZF检测算法相比于TMR和RPR设计有一定时延,但SEC-DED和RPR设计资源占用率优于TMR设计。其中SEC-DED设计比TMR设计的资源占用率下降约1/4,与理论值相符。SEC-DED与RPR设计相比,降低了芯片资源占用率。

表1 迫零检测资源占用和时延

3.2 误比特率

为分析所提基于SEC-DED的MIMO检测算法的误比特性能,本文模拟在星载MIMO检测算法发生单粒子翻转的条件下,对基于SEC-DED的ZF和MMSE检测算法在不同信噪比下的误比特率进行仿真,并与基于RPR和TMR设计的MIMO检测算法进行对比。仿真条件为莱斯信道,收发天线数Nt=Nr=2,信号采用BPSK调制。仿真结果如图3所示。

图3 MIMO检测算法误比特性能随SNR变化曲线

从图3可以看出,基于SEC-DED的MIMO检测算法的误比特性能与基于TMR设计的MIMO检测算法相比无明显变化。在BER相对较大时,基于RPR设计MIMO检测算法的误比特性能明显恶化。当BER较小时,三种设计的误比特性能相当。其主要原因是,降低精度相当于在MIMO检测额外引入了一定量的“噪声”,当BER较大时,降低精度对算法的影响远远大于信道噪声对系统的影响,此时降低精度引入的“噪声”起决定性作用,使得误比特率不随SNR增大而变化。当信道环境较差时,信道噪声起主要作用,降低精度引入的“噪声”对算法的影响很小,使得基于以上三种设计的MIMO检测算法误比特性能相当。

4 抗SEU性能测试

对所提算法的抗SEU性能测试,本文以ZF检测算法为例,通过Xilinx提供的后端工具FPGA Editor,随机修改电路范围内的 LUTs、Block RAM、IO标准等进行测试,进行5 000次故障注入,测试结果如表2所示。

表2 故障注入测试结果

从表2中可以看出,基于SEC-DED的迫零检测算法与TMR设计相比,降低了发生软错误的概率,软错误减少了约25%,提高了抗SEU能力。主要原因是SEC-DED设计的资源占用率下降,受辐射面积减少。基于SECDED的迫零检测算法与RPR设计相比,发生软错误的概率相当,抗SEU性能略优于RPR设计。

综合仿真和测试结果可以看到,基于SEC-DED的MIMO检测算法抗SEU性能最好。此外,与TMR设计相比,误比特性能相当,但节约了大量资源。与RPR设计相比,在数据位宽8~20时,资源占用率低于RPR设计,且误比特性能优于RPR设计。因此基于SEC-DED的MIMO检测算法综合性能最好,更适用于星载平台。

[1]李靖,李建海,刘玉广,等.LTE系统中MIMO传输模式性能分析与仿真[J].电子技术应用,2012,38(10):103-105.

[2]JACPBS A,CIESLEWSKI G,GEORGE A D.Overhead and reliability analysis of algorithm-based fault tolerance in FPGA systems[C].Field Programmable Logic and Applications(FPL),2012 22nd International Conference on.IEEE,2012.

[3]SULLIVAN M A,LOOMIS H H,ROSS A A.Employment of reduced precision redundancy for fault tolerant FPGA applications[C].Field Programmable Custom Computing Machines,2009.FCCM′09.17th IEEE Symposium on.IEEE,2009.

[4]Xilinx.LogiCORE IP Multiplier v11.2[EB/OL].http://www.xilinx.com/support/documentation/ip_documentation/mult_gen_ds255.pdf March 1,2011.

[5]何秉姣,刘科.SEC-DED海明校验码算法研究及其FPGA实现[J].中南民族大学学报(自然科学版),2012,31(3):89-92.