基于FPGA的高速数据存储系统优化设计

2014-12-10张凯华任勇峰贾兴中

张凯华,任勇峰,贾兴中

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

遥测系统数据记录装置是飞行器运作的重要组成部分,其功能是负责接收采编器采集数据并实时存储,保证数据的完整和准确,也称为存储器。在地面测试阶段,存储器主要通过测试电缆和采编器完成数据上传操作,由工作人员通过上位机软件进行分析处理;而在飞行测试阶段,存储器在飞行状态下记录数据,落地后通常会遭受冲击和拉力破坏,对数据的回收工作带来困难。存储器数据的高速存储和工作可靠性问题由此产生。

1 方案设计

根据实际工程应用,LVDS有效数据传送速率不高于59 MB/s,设计要求存储器能够实现LVDS有效数据的可靠存储及数据回读功能,存储容量不小于3 GB。

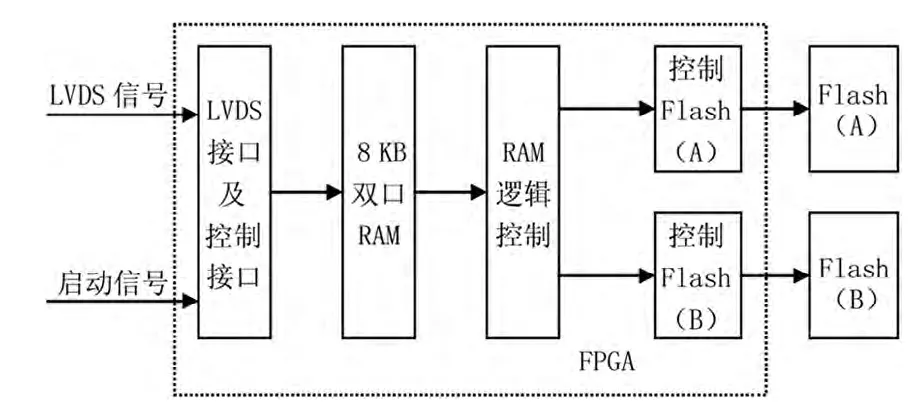

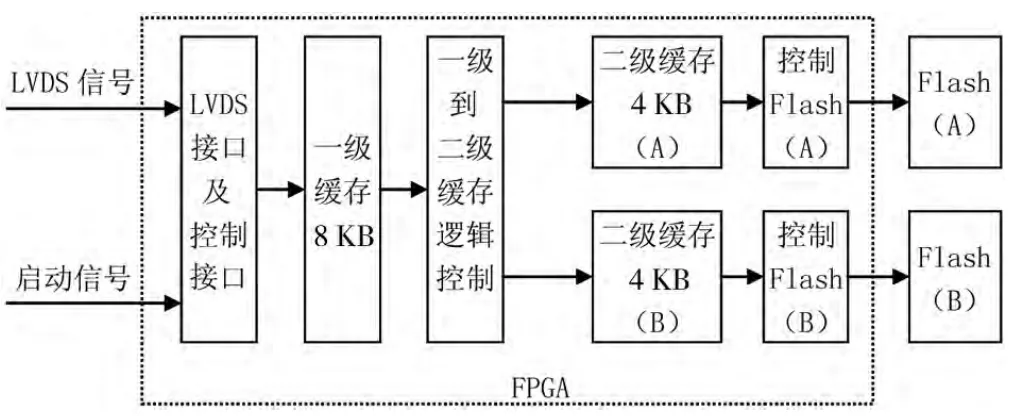

作为存储器的核心组成部分,存储模块设计由接口电路、中心逻辑控制芯片FPGA、配置芯片PROM、LVDS均衡器、LVDS解码器、存储芯片 Flash、电源模块以及60 MHz晶振等构成。LVDS数据经解码器转换为并行数据后传送给FPGA,FPGA对其进行分组,缓存处理,写入Flash芯片;接口电路则实现存储器数据的回收;由电源模块为整个电路提供电源,60 MHz晶振提供工作时钟。原理框图如图1所示。

图1 存储系统原理框图

2 关键技术设计

2.1 存储速率优化设计

根据设计要求,存储模块接收LVDS有效数据的传输速率不高于59 MB/s,要想实现数据准确、完整的存储,就要求其存储速率不低于59 MB/s。设计选用三星公司的NAND型Flash存储芯片K9WBGO8U1M作为存储介质,单片存储容量为4 GB。

K9WBGO8U1M芯片由两片K9WAGO8U1M组成,分别记为chip1和chip2,两者通过芯片 CE1和CE2引脚实现使能控制,当CE1为低电平时,chip1选通,可执行内部擦除、读写操作,反之亦然。Flash的写操作过程即实现页编程的过程,可分为加载和自动编程两个步骤,加载主要完成指令、地址的下发,自动编程则完成数据的存储[1]。由于Flash结构的特殊性,采用不同的操作方式,存储速率都会有所不同,可分为以下几种:

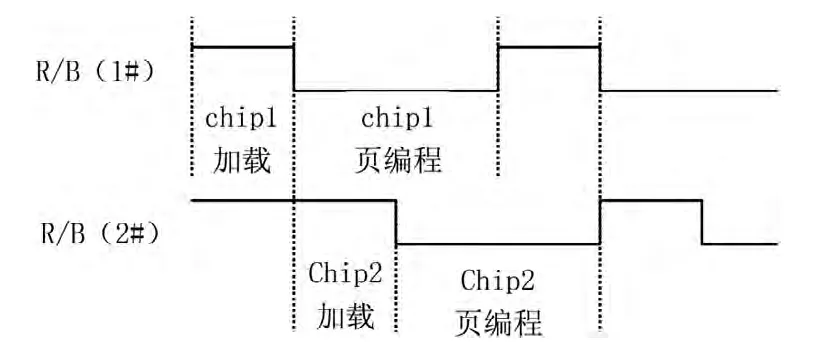

(1)单平面编程方式:该方式是指在同一时刻只有chip1或者chip2响应命令操作,进行页编程,在时间上无法同时进行,从而浪费在等待的过程中。其操作流程图如图2所示。

图2 单平面编程方式示意图

(2)交替页编程方式:该方式是在chip1完成加载并进入页编程时刻,对chip2进行加载,其好处是实现了时间上的复用,避免因为等待而造成时间浪费。其操作流程图如图3所示。

图3 交替页编程方式示意图

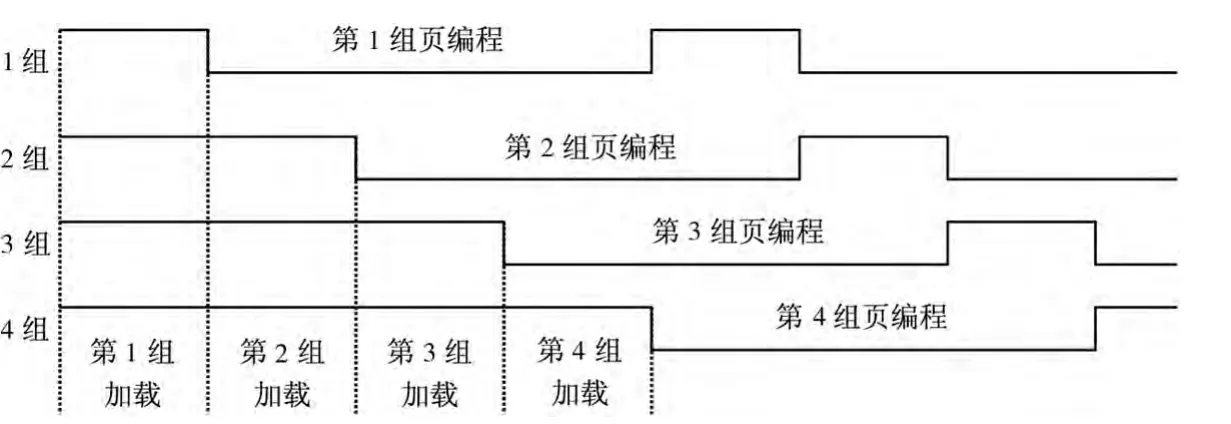

(3)交替双平面编程方式:Chip的内部存储空间可划分为 4个plane,每个plane由 2 048个块和4 KB的页寄存器组成,能够执行单独擦除和编程操作。在执行双平面编程操作时,必须选择两个plane同时进行操作。利用芯片内部不同平面可以单独进行操作的特性,令chip1中plane0和plane1为第1组,plane2和plane3为第2组,chip2中plane0和plane1为第3组,plane2和plane3为第4组,采用如图4所示的流水线操作技术[2],各组的加载和页编程能够实现连续操作,大幅度提高了单片Flash的存储速率。

图4 交替双平面编程方式示意图

当第1组加载完成后,页编程的时间约为200μs,此时对 2、3、4组加载,加载时间大约为 tjiazai={2[4 KB×t+7t]+tDBSY}×3=823.2 μs>200 μs;其中,t=1/30 MB/s,tDBSY为1μs等待时间。因此第4组完成加载时,第1组已经完成页编程操作,可以继续加载。写完4组的时间为T={2[4 KB×t+7t]+tDBSY}×4=1 097.6 μs,则单片 Flash 采用交替双平面编程方式的最大存储速率为4 096×8 B/1 097.6μs=29.85 MB/s>29.5 MB/s,达不到59 MB/s的设计要求。因此,需要对存储模块数据总线进行扩展,采用两片Flash并行存储的办法。该想法的实现对控制单元FPGA的逻辑设计提出更高的要求。

2.2 存储逻辑优化设计

针对存储模块数据总线扩展带来的逻辑控制难题,本设计利用FPGA内部丰富的存储资源以及VHDL语言的可操作性和高灵活性,在FPGA内部构造双端口RAM[3],实现数据缓存,提出以下两种方案:

方案一:利用FPGA内部双口RAM资源,构造8 KB的缓存FIFO。图5所示为存储模块的逻辑原理框图。当存储模块采集信号有效并进入记录状态时,数据流以60 MB/s的速率写入缓存。当写入数据个数大于4 096时,便以30 MB/s速率从缓存中读出4 096个数,写入Flash(A)中;同时继续判断缓存中的数是否大于4 096个,若大于,同样以30 MB/s速率读出4 096个数写入Flash(B)中。依次交替循环,利用两片Flash完成有效数据的写入过程。

图5 方案一逻辑原理框图

经过多次测试,发现存储数据回读后经常出现某位置4 096 B与前4 096 B帧计数颠倒的情况。分析是由于双端口RAM为异步操作造成地址补偿信号offset的值误判引起的[4]。双口RAM写时钟是根据LVDS解串出来的恢复时钟,而读数时钟是逻辑控制模块的120 MHz时钟,所以RAM读写时钟为异步时钟。RAM中的读操作是在地址补偿信号offset满足要求的情况下进行的,而offset的值是在120 MHz时钟下进行判断,可能此时写地址正处于变化状态,使得写地址的值不稳定,导致offset的误判,从而出现帧计数颠倒的现象。

方案二:在方案一8 KB RAM之后增加两个4 KB双口RAM,构成二级缓存[5]。实现两级缓存的逻辑原理框图如图6所示。对于单路的LVDS信号,数据以60 MB/s的速率写入一级缓存,当判断写入数据大于7 106后,以60 MB/s的速率连续读取4 096个数据至二级缓存(A),同时控制 Flash(A)模块对二级缓存(A)中的数据进行判断,当写入数据大于10个后,以30 MB/s速率连续读取 4 096个数并写入 Flash(A)中;同时,如果判断一级缓存中数据个数大于7 106,同样以60 MB/s速率连续读取 4 096个数据,写入二级缓存(B),当控制Flash(B)模块判断二级缓存(B)中数据大于10个后,同样以30 MB/s速率读取4 096个数写入Flash(B)。Flash操作交替进行,实现LVDS有效数据轮流有序地写入两片Flash。当执行Flash读操作时,为了保证数据的完整性和正确性,按照写操作时序依次交替读出两片Flash中的数据[6]。

图6 方案二逻辑原理框图

采用方案二的设计,单片Flash的写入速率达到30 MB/s,进行并行扩展后,使得LVDS数据流同时流入两片 Flash,写入速率可达 60 MB/s,实现了传输速率与存储速率的良好匹配。经过多次测试,回读数据无异常情况出现。因此,采用第二种设计方案。

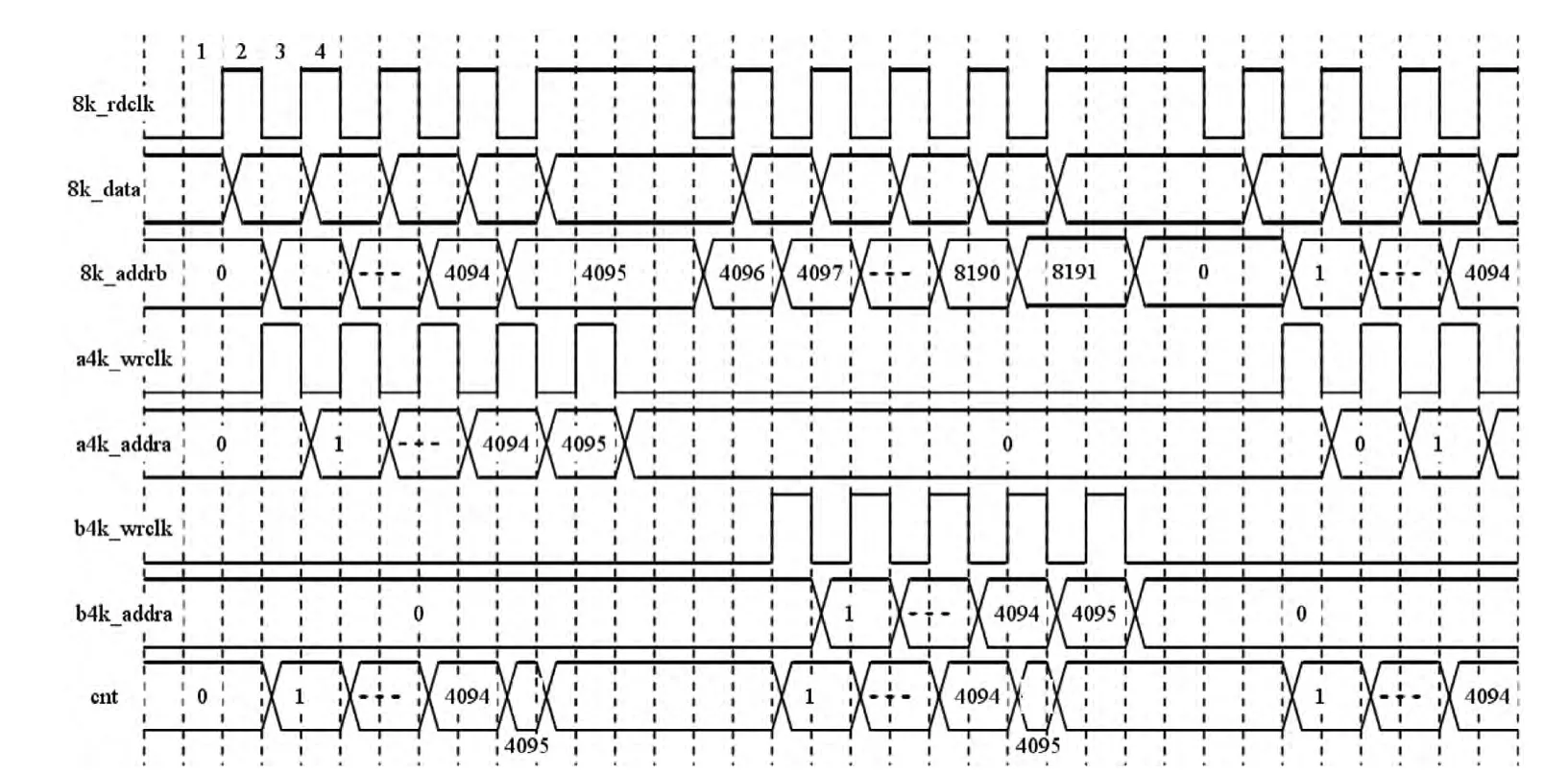

存储模块一级缓存到二级缓存切换时序如图7所示。8k_rdclk表示一级缓冲的读时钟,8k_data表示一级缓存中读出的1 B数据,8k_addrb表示一级缓冲读地址,a4k_wrclk表示二级缓存(A)的写时钟,a4k_addra表示二级缓存(A)的写地址,b4k_wrclk表示二级缓存(B)的写时钟,b4k_addra表示二级缓存(B)的写地址。

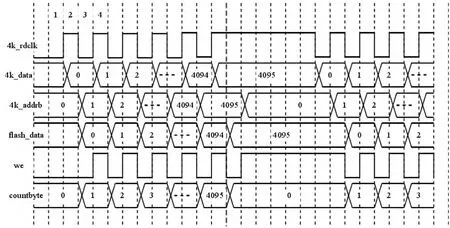

图8所示展示了读二级缓存写入Flash时序图。4k_rdclk为二级缓存4 KB的读时钟,4k_data为从4 KB缓存中读出的数据,4k_addrb为4 KB缓存的读地址,flash_data为写入Flash中的数据,we为Flash的写信号,countbyte为写入Flash的字节计数。

图7 一级缓存到二级缓存切换时序示意图

图8 二级缓存数据写入Flash时序图

2.3 存储器硬件优化设计

由于在飞行试验过程中,存储器落地时会受到地面很大的冲击作用,容易造成内部电路板损坏,因此需要在电路板与机械结构之间填充满缓冲介质[7]。尽管如此,很多情况下晶振也会不可避免地遭到破坏,直接影响到存储数据的回收,而飞行试验的存储数据对于航天分析具有至关重要的作用。因此在存储器设计时采用多备份的设计原则,即将采集数据同时灌入甲、乙两个存储器,每个存储器内部分别有两个存储体,存储体之间相互独立、互为备份,存储有相同的数据。

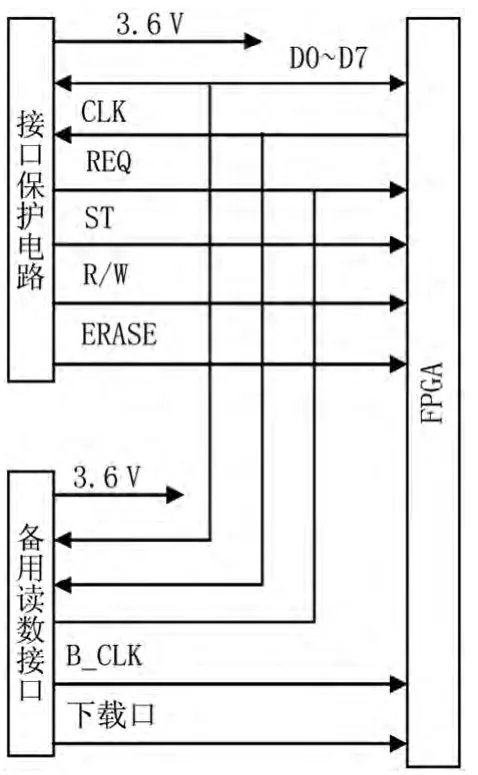

存储器在落地过程中易受到拉力破坏,使其无法再通过测试电缆进行数据回读。针对存储器落地时晶振损坏的情况,对存储模块的接口电路进行改进设计,增加了备用读数接口,两者具有相同的电气特性。在存储器落地后通过备用读数电缆连接地面测试台,由测试台提供给存储器电源和备用读数时钟进行数据回读,实现了存储数据的可靠回收。备用读数接口电路设计原理如图9所示。

3 试验验证

对存储器设计进行改进后,将存储器、采编器和地面测试台通过地面电缆连接,模拟飞行器上的数据采集、存储过程。在数据回收后,由上位机软件进行分析处理,存储数据准确无误,测试数据总量为300 GB。通过备用读数接口和地面甩辩电缆接口读出的数据相同,证明设计方案能够实现采集数据的准确、完整存储及可靠回收。

图9 备用读数接口原理设计

本次设计的存储系统采用Flash的并行存储技术和交替双平面编程的方式,在存储速率方面有很大提高,保证了数据存储的准确性和完整性。同时多备份和备用读数接口的设计也提高了存储器数据回收的可靠性,在数据高速存储和可靠回收测试领域具有良好的应用前景。

[1]盛大鹏.基于Flash的高速大容量存储器的研究[D].北京:中国科学院研究生院,2008.

[2]车艳霞,任勇峰,刘东海.一种小体积高速数据记录器的设计与实现[J].自动化与仪表,2011,26(11):9-11.

[3]白佳俊,孟祥勇,张德平,等.基于 W5300和 FPGA的实时数据采集系统设计[J].电子技术应用,2013,39(4):19-21.

[4]马游春,张涛,李锦明.FPGA集成FIFO在高过载存储测试系统中的应用[J].仪器仪表学报,2006,27(6):2350-2351.

[5]胡宏平,胡兵.基于FPGA的双口RAM在信号采集中的应用[J].微计算机信息,2007(23):223-225.

[6]甄国涌.雷达视频回波模拟设备关键技术研究[D].太原:中北大学,2009.

[7]刘飞.小型高速图像存储系统的设计[D].西安:西安电子科技大学,2009.