基于FPGA的多源信息实时传输系统

2014-12-02季玲玲张志芳

季玲玲,国 辉,张志芳,康 峥

(航天恒星科技有限公司,北京100086)

责任编辑:任健男

1 研究现状

随着空间信息技术的广泛发展,以及军事应用的特殊迫切需求,仅依靠单个传感器监测战场情况显然已无法满足新作战技术的发展要求。近年来我国装备部队传感器种类越来越多,多传感器协同采集信息已势在必行。但多传感器采集的多路数据如何同步实时传输,对战场上及时准确地获取各种有用信息,进行适时完整的战略决策是极其重要的。

大多侦察机的下行链路只有一条,多传感器采集的大量数据必须合并为一路才能传输。然而,侦察机对设备的小型化要求,决定了不可能增加额外硬件设备。

目前,多路数据传输方面的研究主要集中在民用设备中,通常是将话音或等速率同类型的低速数据进行复接[1-4],但当各支路数据速率差距较大时,这些算法无法应用。文献[5-7]将速率差距较大的图像、语音和人工指令数据进行异步复接,根据不同数据的速率比在复接帧内固定开辟空间,但数据源个数或数据速率比一旦发生变化,需重新设定帧结构,通用性不强,无法广泛适用于传感器类型多变的军用设备。

本文针对军用设备的小型化、传感器类型的多样化和传输实时性的要求,提出了一种基于FPGA的多源信息实时传输系统。

2 系统方案设计

2.1 数据接收缓存

本系统的传输数据端是串行输出,故输入数据无论是串行还是并行接口,均需要转换成串行数据。采用FPGA内部数据缓冲器FIFO来实现数据的接收缓存。用系统时钟采样数据时钟的下降沿作为FIFO的写使能,以系统时钟作为FIFO的读时钟,将数据存入FIFO内。由于FIFO并串转换的限制,对于超过8 bit的并行数据接口类型,需要设置2级FIFO,前一级将数据转换到8 bit及其以下的并行数据,后一级FIFO缓存数据。对于不超过8 bit的并行数据和串行数据,用一级FIFO缓存数据即可。

本系统在输入数据的中间读取数据,能防止因数据时钟抖动或传输延迟导致的数据读取不稳定的情况。同时将输入数据和时钟均同步到系统时钟,解决了同一个FPGA工程内出现多个异步时钟的问题。

每路数据对应1个缓存FIFO,每个缓存FIFO设定1个传输门限值。当FIFO内存储数据量低于传输门限时,FIFO将被挂起;挂起机制可防止FIFO读空导致增加未知冗余数据,可通用于连续发送数据和断续发送数据的情况,也适用于停止发送数据的情况。当FIFO内存储数据超过传输门限时,待当前帧传输完后,下一帧即开始读取FIFO内数据进行传输。为节省FIFO资源,FIFO门限值设为一帧可传输的有效数据量。

2.2 数据智能编队

当同时有多个缓存FIFO都超过传输门限时,需要对各FIFO内数据进行编队传输。编队原则采用兼顾数据速率和时间累积的原则:以FIFO内存储数据量动态决定各FIFO传输优先级,每次传输完一帧后,根据各FIFO内存储数据量更新传输编队。如图1所示,第一路数据传输速率最高,FIFO1首先到达门限,数据优先传输;传输完一帧后,若FIFO1数据量仍是最高,则继续传输FIFO1内数据;随着时间累积,相对低速数据总有超过高速数据的时候,此时传输相对低速数据。对于暂时不用的数据路,相应FIFO始终挂起(如图1中FIFO4),不会影响其他路数据的传输。

图1 智能编队示意图

编队机制是本系统的智能化,不仅可以自动判决各路数据的优先级,还可防止高速率数据长时间占用传输通道导致低速数据溢出的问题。编队机制也支持指令决定优先级的功能,且指令优先级高于自动识别功能。

2.3 实时传输流程

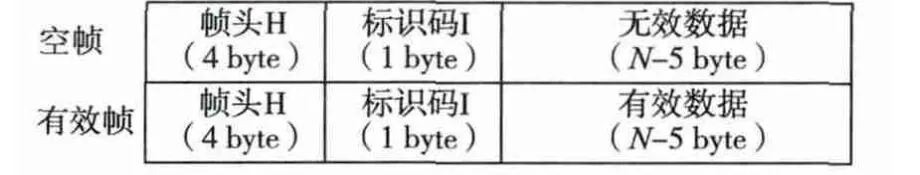

为了便于后续模块的处理,传输帧长固定为N byte,帧头为H(4 byte),标识码I(1 byte)用于区分不同路数据,以便接收端还原各路数据,其余(N-5)byte均为有效传输数据。为了防止无有效数据可传输导致传输数据流中断,以填充空帧来保持数据流的连续性。故传输帧分为有效帧和空帧,如图2所示。空帧出现频率由多路数据速率总和与传输数据速率差距决定,当多路数据速率总和远小于传输数据速率时,空帧才会大量出现;当多路数据速率总和逼近传输数据速率时,空帧将消失,故信道利用率可高达(N-5)/N。

图2 传输帧示意图

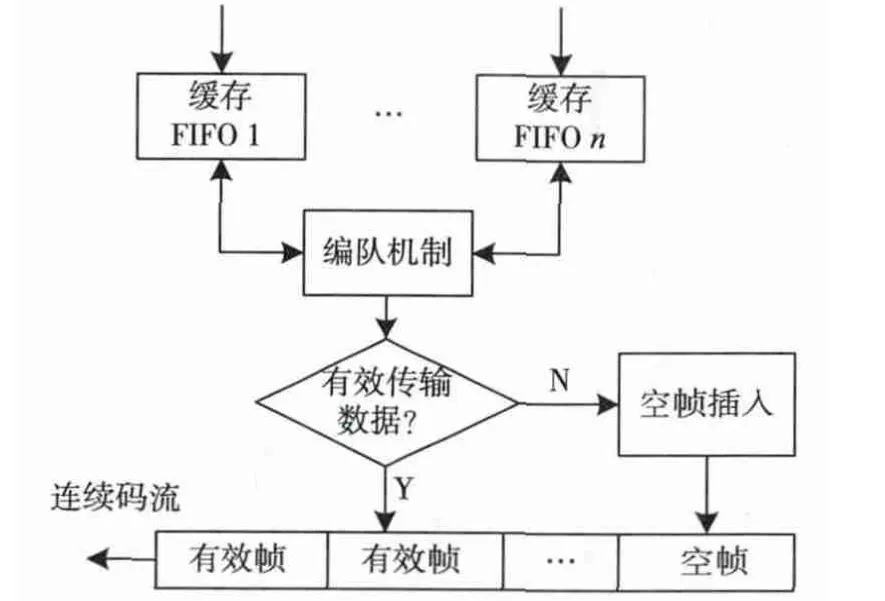

发送端:将各路数据缓存在相应FIFO内,编队模块根据各FIFO上报的存储数据量选出即将传输的FIFO,并生成标识码I,待当前帧传输完毕,下一帧开始传输时,开启选中的FIFO,读取数据进行传输;若无可传输数据,则通知空帧插入模块传输空帧。数据融合传输流程如图3所示。

接收端:通过帧同步模块定位帧头H,提取标识码I,剔除空帧,解析还原各路数据,并存入相应FIFO内。为防止FIFO读空的情况,为每个FIFO设定一个门限值,当低于门限值时,FIFO将被挂起。

图3 数据融合传输流程图

3 系统硬件实现平台

本系统基于Xilinx公司的XC4VLX60-10FF668I芯片开发。本系统资源开销少,除占用FPGA内部的FIFO资源外,其余资源极少占用,仅需嵌入原有的FPGA程序内,无需额外硬件开销。

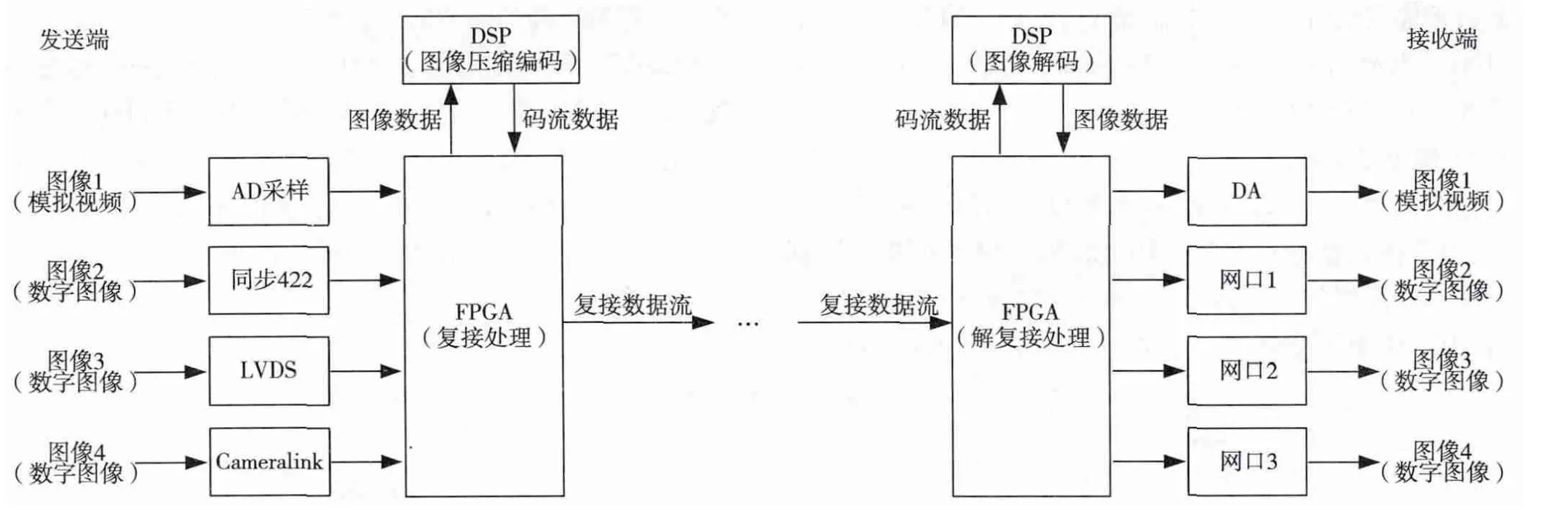

发送端接口类型有视频接口、同步422、LVDS、Cameralink,可支持DVD、摄像头、可见光、红外、CCD数码相机、低速SAR等多种传感器的输入数据源。接收端输出接口有模拟视频口和网口。模拟视频数据可通过监视器还原视频图像;网口可将不同路图像数据输出给目标设备。此外本系统还配有DSP,用于对视频图像进行压缩编码。硬件平台框图如图4所示。

多种传感器数据通过不同接口进入发送端:

图4 系统硬件平台框图

1)第1路图像数据为标准模拟视频信号,需经过AD离散化采用后形成并行数据输入到FPGA内,FPGA根据视频标准格式将AD采样后的数据通过McBSP(Multichannel Buffered Serial Port)接口输出给DSP,DSP将其进行压缩编码形成码流数据后再通过McBSP接口返回给FPGA;McBSP接口为64 bit并行数据,针对本系统应用在数据接收缓存模块需采用2级FIFO;

2)第2路图像数据为串行数字信号,通过同步422接口输入到FPGA进行数据接收缓存;

3)第3路图像数据为串行数字信号,通过LVDS接口输入到FPGA进行数据接收缓存;

4)第4路图像数据为Cameralink的高清图像,28 bit并行数字信号,通过Cameralink接口输入到FPGA,与第1路的标清视频图像相同,需要经DSP压缩后方可传输。

4路数据源经过数据接口缓存模块处理后,智能编队模块根据各FIFO上报的存储数据量确定各路数据传输的优先级,形成复接数据流。

接收端FPGA根据帧标识码I解析还原各路数据,并存入相应FIFO内:

1)FPGA将第1路码流数据通过McBSP接口输出给DSP进行解码还原标准视频图像后,再通过McBSP接口返回给FPGA,FPGA输出给DA进行数模转化恢复模拟视频信号,通过监视器显示第1路图像;

2)第2至第4路图像通过不同网口输出给目标设备进行后期应用处理。

本系统算法内参数设置如下:复接帧帧同步码H为0x1ACFFC1D,帧长N为1 084 byte。发送端缓存FIFO门限值为1 079 byte(N-5),接收端缓存FIFO门限值为1 024 byte,故信道最高传输利用率为(N-5)/N=99%。

4 试验结果

为验证本系统的可行性,搭建上述硬件平台。

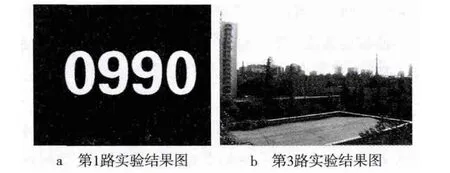

第1路外接标清 DVD,PAL制,25 f/s(帧/秒)图像,图像像素尺寸为720×576,8 bit灰度图像。经DSP压缩后生成2 Mbit/s码流,传输到接收端后,经DSP解压缩后将还原的视频图像输出给监视器显示,如图5a所示。

图5 系统实验结果图

第2路外接实验室测试设备输出的1 Mbit/s纯数字信号,为便于验证本系统传输数据的正确性,将该路数字信号设成帧内容均相同,仅帧计数器有变化的帧格式。帧头为0xEE0036,紧跟帧头后有一字节表示帧计数器,帧长480 byte(包括帧头),经本系统传输后,由网口1输出到工控机,接收到的数据信号与发送的数字信号相同。

第3路外接实验室测试设备输出的500 kbit/s纯数字信号,验证方法与第2路相同,仅接口类型和速率不同,该路数据接收正常。

第4路外接Cameralink接口的高清摄像头,base模式,30 f/s,图像像素尺寸为1 024 ×768,24 bit三分量彩色图像。经DSP压缩后生成4 Mbit/s码流,传输到接收端后,经DSP解压缩后将还原的高清图像通过网口3输出给工控机,如图5b所示。

实验结果表明,本系统可同时支持多源信息实时传输。

5 小结

本文针对军用设备的小型化、多传感器和传输实时性的要求,提出了一种基于FPGA的多源信息实时传输系统。该系统解决了现有算法的四大弊端:1)通用性。对于同步接口信息,可实现透传,无需知道帧格式和数据速率,可广泛通用于各类传感器。2)信道利用率。为各路数据编队动态传输,信道利用率可高达99%。3)智能性。可自动识别各路数据优先级,也可根据指令决定优先级。4)扩展性。本系统不局限数据源个数,可根据实际情况扩展。

目前本系统已成功应用于多项国家“863”预研项目和无人机及飞艇等型号项目中。实际应用证明,本系统运行稳定可靠,适应性强。

[1] ABDULLAH M K,MAHBDIRAJIG A,ELHAG M F.A new duty cycle based digital multiplexing technique[C]//Proc.IEEE International Conference on Telecommunications.[S.l.]:IEEE Press,2007:526-530.

[2] WANG H S,QIN X Y,ZENG LG,etal.Decoding and recovery of clock synchronization in digital multiplexing system[J].IEEE Trans.Communications,2003,51(5):825-831.

[3] PARK CH,YOO SM,CHOOAND H,et al.Multi-user data multiplexing for digital multimedia broadcasting[J].Computer Communications,2006,29(18):3970-3975.

[4] GERARD K,RAUWERDA C.Towards software defined radios using coarse-grained reconfigurable hardware[J].IEEE Trans.Very Large Scale Integration Systems,2008,16(1):3-13.

[5]刘力维.一种新型的数字图像/话音传输系统的实现方案[J].电视技术,2001,25(11):27-28.

[6]刘昌锦,刘永峰.基于FPGA的异步数字复接系统[J].计算机测量与控制,2007,15(12):1829-1831.

[7]杨保平,陈永光,陈军,等.基于FPGA的战术数据链中继传输复接技术[J].系统工程与电子技术,2010,32(12):2628-2631.