基于ARM和FPGA的红外系统数据交换驱动设计

2014-12-02王小平

王小平,吴 伟

(1.重庆城市管理职业学院,重庆401331;2.重庆邮电大学信号与信息处理重庆市重点实验室,重庆400065)

责任编辑:薛 京

红外辐射测温技术作为一种非接触温度测量方法,广泛应用于军事和民用领域。红外成像仪通过该技术将温度的差异转换成实时的视频显示在监视器上[1]。它能全天24 h工作,即使在最黑的夜晚、浓雾、下雪和烟雾条件下也能进行观看,它能快速探测所存在的威胁并快速做出反应以保护人员、财产和基础设施的安全。同时,本文关于数据采集的方法具有一般性,在电视信号的数字化、视频监控、交互式网络电视数据采集等方面都具有广泛的应用。

1 系统设计整体架构

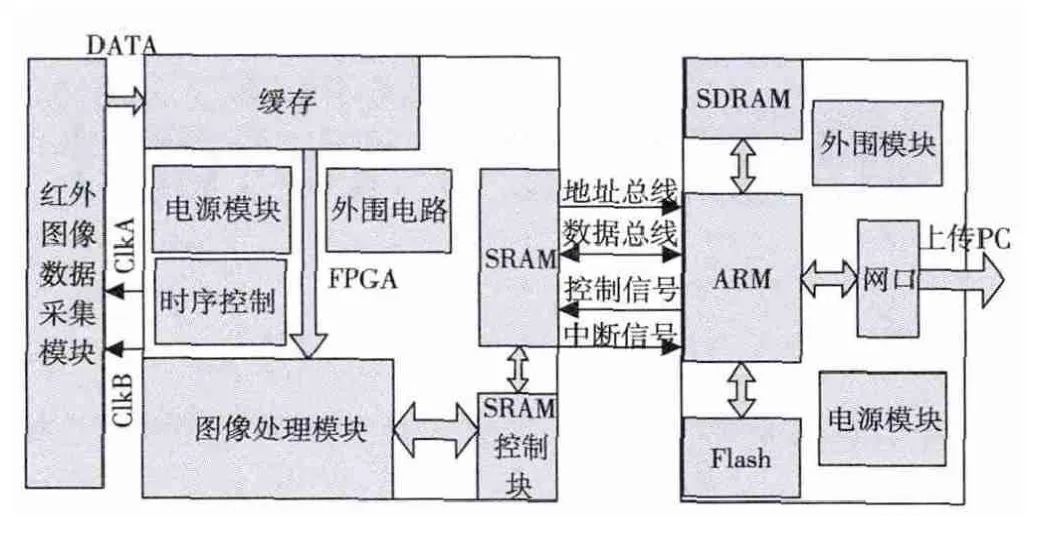

本文主要介绍一种基于ARM(Advanced RISC Machines)和FPGA(Field Programmable Gata Array)的红外监控系统。ARM模块实现对各个单元模块的初始化、控制和管理,FPGA模块为前端图像采集模块提供驱动时序,对图像数据进行处理,为ARM系统进行数据交互。本系统FPGA芯片选用ACTEL公司推出的ProASIC3系列芯片,它具有百万系统门,采用1.2 V直流电压供电,0.5 nm COMS工艺[2];ARM处理芯片选用SAMSUNG公司推出的16/32位RISC微处理器S3C2440A,功耗低、外围接口丰富,具有32根地址线,支持4 Gbyte存储空间。设计时充分利用ARM易操控性和FPGA处理数据的并行性。

系统中FPGA模块首先为前端图像数据采集模块提供时序控制,将输出的模拟图像信号通过模数转化变为数字信号,为弥补探测器硬件的缺陷,FPGA对图像数据进行盲元补偿、非均匀性校正、滤波等算法处理,通过乒乓的操作方式,对数据进行内存映射,将数据通过4路FIFO缓存到SRAM内,当采集一帧数据后向ARM模块发出中断信号。ARM模块通过驱动程序响应FPGA发出的中断信号,触发片选信号,将ARM的地址总线映射到该SRAM芯片内,触发DMA中断,通过DMA方式将数据映射到内存空间,最后通过网口将图像数据上传到PC。系统整体设计框图如图1所示[3]。

2 数据接口硬件设计

图1 高速红外监控系统设计框图

对于高速图像采集系统,两个模块的数据交互接口非常重要,极有可能成为高速图像传输性能的瓶颈。根据系统对处理数据的分析,考虑到系统向上和向下的兼容性,SRAM选型时均考虑处理数据的最大值情况,前端非制冷焦平面微热辐射计型探测器选用系统兼容最大可能的384×288像素,处理后的图像数据16位宽度,得到未经过压缩的单帧图像数据量为2.16 Mbyte。考虑到图像处理运算过程中需要大约10帧的图像缓存空间。

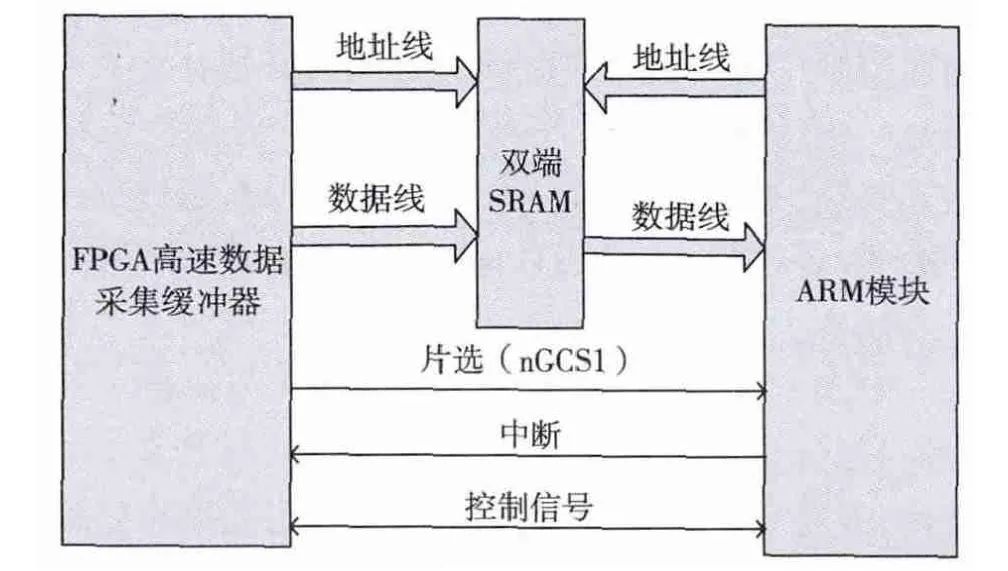

鉴于以上对系统中传输数据的分析,本系统选用ISSI公司的IS61LV51216,高性能CMOS制造工艺,存储容量为512×16 kbit,内部8 Mbyte容量,存取时间最低可达8 ns,全静态操作不需要时钟或刷新,输入输出兼容TTL标准,高字节数据和低字节数据可分别控制,最高运行频率为133 MHz,常见的封装为44脚TSOP,兼容LVTTL接口。具有简单的读写和片选控制引脚,在与FPGA和ARM连接时,只需将SRAM的控制端、数据端及地址端直接与FPGA和ARM分配的相应端口连接,并在FPGA和ARM中设计SRAM接口控制模块,便可实现SRAM的读写操作[4]。ARM与 FPGA接口电路设计框图如图2所示。

图2 ARM与FPGA接口电路设计框图

FPGA模块首先将前端处理后的高速数据分为4路低速数据写到构建的4个FIFO中,采用乒乓操作的方式将经过算法处理的32 bit数据存到4个FIFO中[5]。经过对SRAM的时钟控制,将4个FIFO的数据分别存储到4个地址区域,将8 Mbyte的SRAM分为4个地址空间,由于SRAM的写时钟信号和FIFO的时钟信号为同频,所以FIFO时钟与输出之间必然会产生时间延时,本文采用将FIFO的时钟相位做相应的偏移,然后作为SRAM的写时钟信号方法,有效地避免了竞争冒险。

存入的数据采用小端存储方式,数据存储的控制模块采用中断控制方式对数据流进行相应控制,当FIFO中的数据达到系统设计的一帧阈值时,控制模块将FIFO中的数据存储到SRAM中,当SRAM中的数据达到一帧数据时,控制模块向ARM端口发出中断信号,ARM通过片选总线获取数据。

3 驱动程序设计

系统以ARM模块为核心对各个模块进行控制,其操作系统选用具有开源、免费、安全、稳定、高性能等优点的Linux系统,应开发商要求本系统选用Linux-2.6.30稳定版本。

在整个系统中,驱动程序主要工作为:消息队列函数等待响应中断信号,软件触发DMA中断,数据进行内部映射,DMA方式获取红外图像信号。驱动程序主要处理过程为:

1)初始化前端SRAM模块,注册设备号,申请外部中断和DMA中断,申请两个阻塞等待队列;

2)判断FPGA模块发出的中断信号,唤醒等待队列1,并进行中断响应;

3)通过片选nGCS1,将地址线、数据线获取片外SRAM数据;

4)唤醒等待队列2,响应DMA中断,通过DMA方式对数据进行内存映射;

5)将SRAM的存储空间映射到用户进程空间。

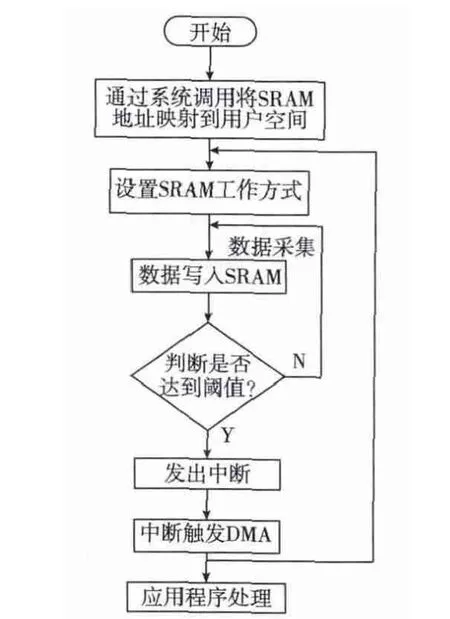

驱动设计的主要流程如图3所示,驱动程序主要分为下面几个部分进行介绍。

图3 ARM驱动设计流程图

3.1 模块初始化

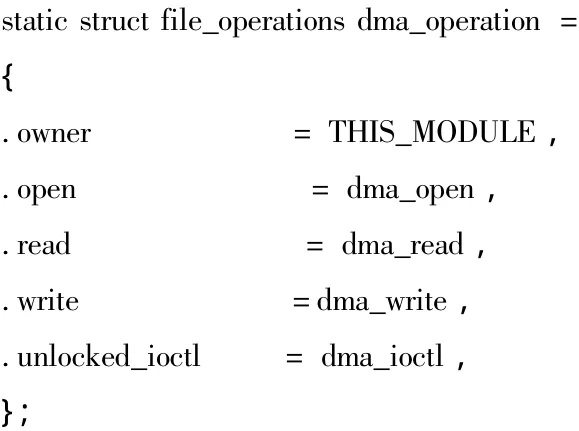

每个字符设备驱动中都需要一个file_operations结构,便于内核与驱动程序的操作对应,file_operations结构是定义在<Linux/fs.h>中的函数指针数组,结构体中的每一个域对应着驱动内核模块用来处理某个被请求事件的函数首地址,在驱动编写时均用dma作为函数名[6]。

本次设计中SRAM驱动模块初始化定义如下:

在该结构体中,每个函数的参数都有1个指向特定file结构的指针,第2个参数在驱动程序中都有对应的硬件操作程序,每个参数都有特定的功能。

对驱动程序的初始化是在dma_init()函数中完成的,其中包括设备号的申请、外部中断的初始化、对外部地址映射空间的初始化等。

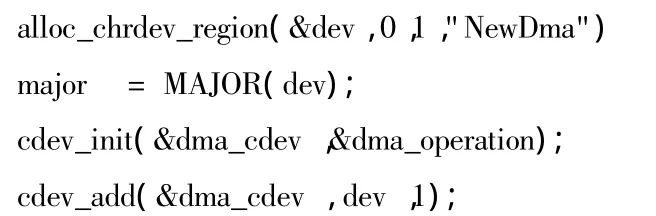

3.2 驱动设备号申请函数

本文设计的驱动函数采用动态分配设备号,调用函数 alloc_chrdev_region(dev_t*dev,unsigned int-firstminor,unsigned int-count,char*name),其中 dev 为手动给定的设备号,count为所请求的连续设备号的个数,而name为与该设备号范围关联的设备名称,它将出现在/proc/devices和sysfs中。采用动态申请可以避免手动指定设备号带来的缺点,即:

3.3 中断申请初始化

由于Linux内核要与外部硬件设备进行通信管理,但处理器的处理速度与外围设备速度不处于一个等级,不能采用浪费处理器资源的轮询方式进行处理,因此驱动程序中通过注册中断号并且激活一个中断处理函数来对数据进行处理。中断注册函数如下所示:

request_irq(unsigned int irq,irq_handler_t handler,unsigned long flags,const char* name,void* dev)

其中第1个参数irq表示分配的中断号,第2个参数handler是指向中断处理函数的指针,中断一旦来临转到处理中断处理函数,第3个参数flags指定了快速中断或中断共享等中断处理属性,第4个是设备驱动程序的名称,第5个是中断名称。与之对应的中断注销函数为free_irq(unsigned int irq,void*dev_id),一般在退出和出现特殊情况时调用。

本系统选用的是外部中断4(IRQ_EINT4)与DMA中断,选用软件触发的DMA3通道(IRQ_DMA3)。具体程序代码如下:

s3c2410_gpio_cfgpin(S3C2410_GPF4,S3C2410_GPF4_EINT4);//定义I/O口为中断

set_irq_type(IRQ_EINT4,IRQF_TRIGGER_RISING);//设置中断4触发方式

ret=request_irq(IRQ_EINT4,irq_int4_handler,IRQF_SHARED,"irq_int4",1);//中断 4

request_irq(IRQ_DMA3,dma_finish_handler,0,"dma_irq",NULL);//DMA3中断

3.4 等待队列

等待队列属于阻塞式的访问模式,阻塞方式是驱动在对设备进行操作时,如果始终没有获取中断信号,进程将会被挂起直到中断信号来临满足条件后再进行操作;非阻塞式是不对设备进行操作时,不断地查询或者放弃控制设备,这样将大大降低系统性能。本驱动选用阻塞式等待队列,当应用程序对设备进行读操作时,会调用一个程序,将系统的控制权交给内核并进入等待状态,当系统执行程序完毕后向应用程序返回响应,得到响应后系统将退出阻塞状态继续后面的工作。

下面简要介绍等待队列的基本操作。

1)定义等待队列头并初始化

DECLARE_WAIT_QUEUE_HEAD(dma_waitq);

DECLARE_WAIT_QUEUE_HEAD(int4_comeq);

系统主要是在等待两个中断时进行阻塞,分别取名为 dma_waitq,int4_comeq。

2)等待事件函数

wait_event_interruptible(int4_comeq,int4_come==1);

wait_event_interruptible(dma_waitq,dma_finish==1);

首先wait_event_interruptible将当前进程的状态设置为TASK_INTERRUPTIBLE(可中断的睡眠状态),然后调用schedule()(进程调度)函数,schedule()会将位于TASK_INTERRUPTIBLE状态的当前进程从运行的等待队列中删除,当前进程不再参与调度,最后调用wake_up_interruptible()函数将当前进程重新放入到运行的等待队列中。

3)响应函数

当变量int4_come1和dma_finish1的值不等于1,进程将自动再次被设置为TASK_INTERRUPTIBLE状态,然后执行schedule()函数,进程将从正在运行的队列中删除,这时就需要再次通过wake_up_interruptible()函数将当前进程重新放入到运行的等待队列中。两个等待时间响应节点函数设置在对设备的读操作(read()函数)中,只有当变量int4_come1和dma_finish1的值等于1时才退出阻塞,进行下面的动作。设置满足变量条件的函数即int4_come1=1;dma_finish1=1和wake_up_interruptible()在中断响应函数中实现。中断响应函数代码如下:

3.5 存储器控制初始化

S3C2440A存储器控制器为访问外部存储器提供控制信号,控制器包括以下特性:支持软件大/小端控制,共1 Gbyte的存储空间分为8个Bank,每个Bank有128 Mbyte的空间,其中 Bank6~Bank7存储器为 ROM,SRAM,SDRAM提供控制,Bank0~Bank5为ROM,SRAM提供控制。具有7个固定的Bank地址,1个可变的存储器Bank地址,所有的存储器访问周期都可以编程控制,并且支持SDRAM自刷新和掉电模式。S3C2440A内部存储空间地址分配如图4所示。

系统选用的SRAM芯片为IS61LV51216,芯片总线宽度为16位。该外部存储器SRAM映射到Bank1上,物理地址0x08000000上,需要对控制寄存器进行相应的设置,首先是总线宽度和等待控制寄存器BWSCON,该寄存器的物理地址为0x48000000,只需对Bank1的控制位进行相应设置。SRAM不使用UB/LB,禁止WAIT状态,数据总线宽度根据芯片所知为16位,BWSCON中Bank1的控制信息详见S3C2440A芯片手册。

图4 S3C2440A内部存储空间地址分配

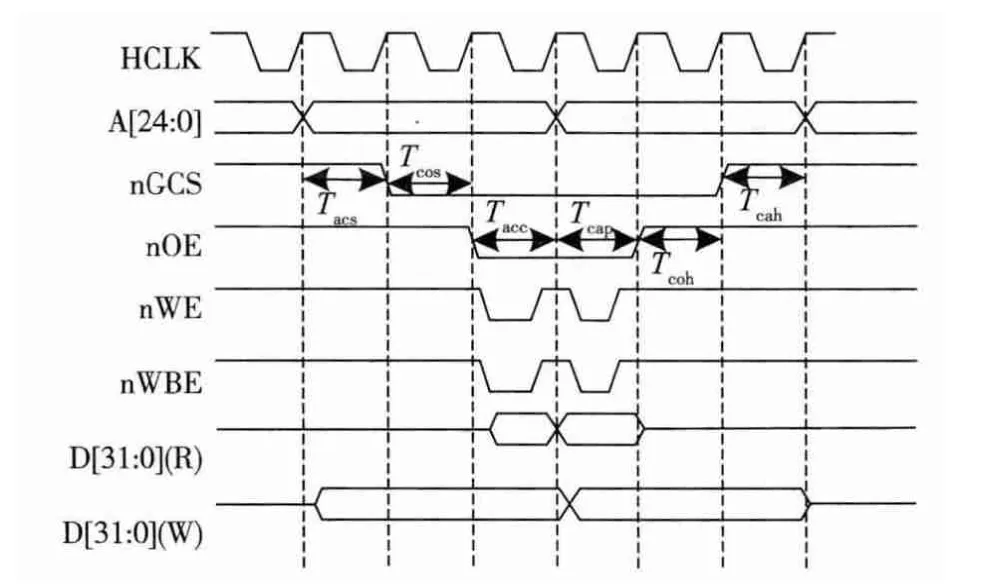

由于采用的是 Bank1,对 Bank1的控制寄存器(BANKCON1)进行相应设置。根据S3C2440A芯片手册,该寄存器物理地址为0x48000008,对寄存器每一位进行相应设置,根据图5对SRAM控制时序对寄存器进行相应配置。

图5 SRAM控制时序图

图5中,Tacs为nGCS n前的地址建立时间选择0个时钟;Tcos为nOE前的片选建立时间选择0个时钟;Tacc为访问周期选择14个时钟;Tcoh为nOE后的片选保持时间选择0个时钟;Tcah为片选信号nGCS1后的地址保持时间选择0个时钟;Tacp为Page模式下的访问周期选择0时钟;PMC为Page模式配置选择正常模式一个数据。这些参数都在BANKCON1寄存器中进行配置。具体代码如下:

#define BWSCON 0x48000000

#define BANKCON1 0X48000008

rBWSCON=ioremap_nocache(BWSCON,4);

r BANKCON1=ioremap_nocache(BANKCON1,4);

3.2 量表信度 Cronbach′s α系数 它用于评价问卷的内部一致性,其取值范围为0~1,取值越大,问卷的内部一致性越好。一般而言,系数为0.7以上表明问卷的信度较好[12]。本研究显示,中文版N-QOL两个维度及总量表的Cronbach′s α系数分别为0.763、0.734、0.782,表明本量表具有较高的内部一致性信度。2个维度与总量表的相关性分析结果提示,量表各维度与总量表的相关性均较好。

*rBWSCON =(*rBWSCON&~(0xf<<4))|(2<<4);

*rBANKCON1=*BANKCON1& ~(0x7f< <4)|(7< <8);

3.6 DMA寄存器初始化

S3C2440A支持处于系统总线和外设总线的4个DMA通道,DMA控制器的每个通道都可以无限制地执行系统总线和外设总线之间设备的数据移动,每个DMA通道都可以执行下面4种情况[7]:

1)源地址和目标地址都在系统总线上;

2)源地址在系统总线上,目标地址在外设总线上;

3)源地址在外设总线上,目标地址在系统总线上;

4)源地址和目标地址都在外设总线上。

DMA可以在没有CPU的干扰之下进行数据传输,大大提高处理器的效率,DMA的运行还可以由软件进行控制,也可以由来自内部或者外部的引脚请求进行。本系统选用DMA3通道,采用软件触发的方式进行,驱动程序需要对DMA中的相关寄存器进行配置。

源地址控制寄存器DISRCC3,物理地址为0x4B0000C4,源地址在系统总线(AHB)上,每次进行单次和突发模式传输后数据大小选择增加。

目的地址寄存器DIDST3,物理地址为0x4B0000C8,分配目的地址时要注意,由于采用DMA方式,内存中获取的目的虚拟地址数据与cache中数据不一致将会出现内存错误,所以在进行地址申请时要禁止C(Cacheable)域,C域代表是否使用高速缓冲存储器。也就是cache。所以在进行目的地址申请时采用dma_alloc_writecombine()。

目的地址控制寄存器 DIDSTC3,物理地址为0x4B0000CC,因为SRAM也外设在系统总线上,所以与源地址控制寄存器配置相同。

DMA控制寄存器DCON3,物理地址为0x4B0000D0,该寄存器有32位,配置非常重要,针对外接SRAM的特性,软件触发的方式。最后对DMA触发屏蔽寄存器(DMASKTRIG3)进行配置,主要设置为软件触发方式。如要详细了解配置原因详见芯片手册。

#define DMA3_REGS_BASE 0x4b0000c0

struct dma_regs{

volatile unsigned long disrc;

volatile unsigned long disrcc;

volatile unsigned long didst;

volatile unsigned long didstc;

volatile unsigned long dcon;

volatile unsigned long dstat;

volatile unsigned long dcsrc;

volatile unsigned long dcdst;

volatile unsigned long dmasktrig;

};

dma_regs=ioremap_nocache(DMA3_REGS_BASE,sizeof(struct dma_regs));

dest=dma_alloc_writecombine(NULL,BUSIZE,&dest_phy,GFP_KERNEL);

dma_finish=0;

dma_regs->disrc=FPGA_DATA_BASE;

dma_regs->disrcc=0;

dma_regs->didst=dest_phy;

dma_regs->didstc=0;

//AHB|interrupt|burst|holemode|reload

dma_regs->dcon=(1<<30)|(1<<29)|(1<<28)|(1<<27)|(1<<22)|(BUSIZE/4);

dma_regs- >dmasktrig=(1<<1)|(1);

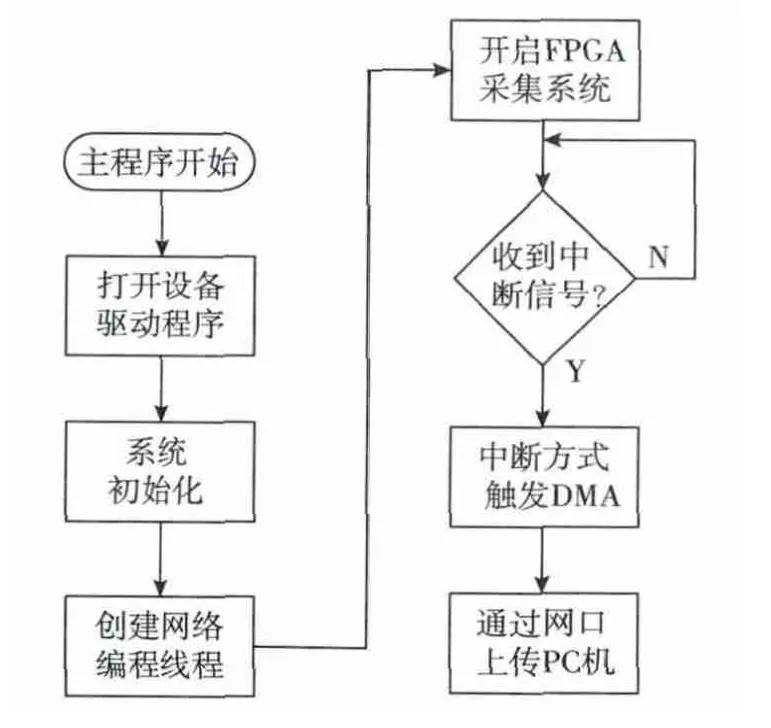

4 应用程序设计

系统对实时性要求较高,以突出高性能为主,因此应用程序规模较小,在设计时采用面向过程的开发方式。本系统的主要开发流程如图6所示。

图6 应用程序流程

本系统的主要应用程序较简单,主要是将图像数据上传到PC机,本系统选用UDP的方式进行数据传输。

上传数据包括两个部分,一个是图像数据,另一个是传感器信息。由于传输数据中包括了实时媒体流数据,因此该网络传输协议采用了RTP/RTCP实时传输协议和实时传输控制协议。传输数据包括标签数据和视频压缩数据,进行分时传输,但由于标签数据重要性高,因此具有更高的优先级,即保证一个传输周期内标签数据可靠传输完成后,再进行视频数据流的传输。

RTP/RTCP下层使用的网络层协议为UDP,因为RTP/RTC协议已经完成了差错控制和拥塞控制等传输控制,不需要使用复杂的TCP协议来实现,而是选择简单的UDP 协议[7]。

数据按照RTP格式封装完成后,使用UDP协议通信,UDP不要求保持一个连接,没有因接收方认可收到数据包而带来的开销,需要的网络带宽比TCP更小。UDP通信的程序设计流程图如图7所示。

图7 网口数据传输协议

5 实验结果分析

对采集的原始图像,在FPGA做相应的盲元补偿、滤波、非均匀校正等算法处理。通过实验室中黑体映射进行温度标定,建立温度与灰度的映射表,ARM系统中采用DMA方式对图像进行传输存取,每帧图像分辨率为384×288,每点的图像数据位16 bit,在进行图像显示时只需选取高8位轮廓进行显示就能达到要求,经测试传输速度为15 f/s(帧/秒),网口模块需要在系统中达到20 Mbit/s的带宽,经过测试本系统网口模块能达到传输要求。最后PC机对上传的灰度数据经过编码显示。系统实物图和PC机接收到烙铁红外图像如图8所示。测试表明本文设计的各组模块均能达到红外监控系统的要求。

6 总结

本文设计出基于ARM和FPGA红外系统数据交换驱动程序,详细介绍驱动设计的流程,在传统数据的内存映射传输方式上,提出软件触发DMA方式实现对图像数据的搬移,极大提高了系统传输效率。

图8 系统实物图和PC机接受到烙铁红外图像

[1]周庆福,杨永军,吕国义.红外辐射测温仪及校准方法探讨[J].计测技术,2008,28(1):33-35.

[2]王剑飞.基于FPGA和DSP的多路信号采集系统的设计[J].电视技术,2013,37(23):57-60.

[3]宋玲,裴志强,刘宝娟.Actel FPGA芯片APA150研究与应用[J].微处理机,2008(3):22-23.

[4]许川佩,孙义军,吴玉龙.基于ARM和FPGANoC资源网络接口驱动设计与实现[J].微型机与应用,2013,32(13):83-86.

[5]吴华,谢礼莹,徐泽宇.基于 ARM9的红外热像仪设计与实现[J].计算机工程,2010,36(16):234-236.

[6]杨柱,刘健.先入先出数据缓存的方法及全满空间访问先入先出存储器,中国:CN200510083155.7[P].2006-02-08.

[7]屈晓平,刘涛.嵌入式Linux操作系统设备驱动程序程序设计与实现[J].计算技术与自动化,2008(10):45-46.

[8]姚锡忠.基于S3C2440的FlexRay总线设计[J].淮海工学院学报:自然科学版,2010,19(3):25-27.