基于多核处理器的加密卡异步并行驱动设计*

2014-10-31秦培斌肖志辉杨大川李希源

秦培斌,肖志辉,杨大川,杨 洋,李希源

(1.西南交通大学 信息科学与技术学院,四川 成都 610031;2.迈普通信技术股份有限公司,四川 成都 610041)

0 引言

随着当今网络的飞速发展,网络承载业务量的激增和业务种类的多元化变迁,人们对网络设备提出了更高的要求。以路由器设备为例,不仅要求更加高速的数据处理转发能力,同时要提供可靠的网络安全协议,保障网络数据的安全。在3G、4G无线传输,互联网金融,电子政务以及传统的银行等对数据安全要求较高的应用场景中,网络安全就显得更为重要。可以说,在很大程度上网络的安全性依赖于网络传输设备的安全性。因此,在路由器、交换机等网络传输设备中实现数据加密,对保障我国网络安全具有重要意义。

现有的加密方式主要有软件加密和硬件加密两种[1]。软件加密的优势在于其设计难度和成本较低,但加密速度依赖于CPU的性能,且会消耗大量系统资源,安全性和可靠性较硬件加密差[2]。硬件加密采用专用的加密卡实现,具有较高的安全性和可靠性,越来越成为加密技术的发展方向。因此,如何提高硬件驱动的效率,以获得对加密卡性能最大程度的利用,关系到整个通信设备的性能。

1 加密卡的硬件结构

该加密卡主要由 FPGA、DDR、随机数芯片、Flash和通信接口等模块组成。FPGA是整个加密卡的核心部分,其完成SM1加密算法,内含6个独立的SM1加解密通道。Flash中存储有FPGA的程序镜像,实现FPGA程序的上电加载。加密密钥及加密向量由随机数芯片产生以确保数据的随机性。DDR模块用来存取主机端发来的加解密报文和随机数报文。SPI接口和10G以太接口通过2MM连接器完成路由器主机端与加密卡FPGA的管理数据和业务数据的交互。这种将管理数据和业务数据分离的实现方式,使加密卡控制集中、结构简单,在保证数据安全的同时使加密卡具有更高的灵活性和效率。图1为加密卡硬件结构框图。从图1中可以看出整个加密卡的核心处理机制就是由主机端的驱动程序和加密卡上的FPGA实现私有协议之间的通信,完成对加解密数据的传递。

图1 加密卡硬件结构框Fig.1 Encryption card hardware structure

2 加密卡驱动设计

目前的数据加密技术根据密钥类型可分为私钥加密和公钥加密[3],而SM1加密算法是一种私钥(对称)加密算法。本加密系统采用IPSec协议层<——>SM1加密算法驱动层<——>SM1硬件加密芯片这种软硬件架构。根据IPSec层的调用需求,为了获得更强的SM1算法处理能力,SM1加密算法驱动层采用异步流水线方式实现。IPSec协议层可以将报文批量传入驱动层,然后进行缓存和排序,驱动层通过万兆以太通道交送硬件加密芯片进行加密处理,待报文加密完成并回送至驱动层过后,驱动层通过回调函数将报文送回IPSec协议层。

2.1 加密卡驱动结构

加密卡驱动程序设计是基于VxWorks操作系统编写的,主要分为初始化模块、私有调试模块、数据收发模块和工装测试模块,各模块间的调用关系及数据流如图2所示。初始化模块主要完成对FPGA等硬件资源的初始化、软件缓存队列的申请以及发送接收任务的创建和注册。私有调试模块和工装测试模块主要完成对加密卡加解密报文的正确性测试和性能测试。数据收发模块是整个加密卡驱动的核心,需要维护驱动缓存队列,完成对数据的收发,同时要考虑多核下操作虚拟BD环的任务互斥问题。

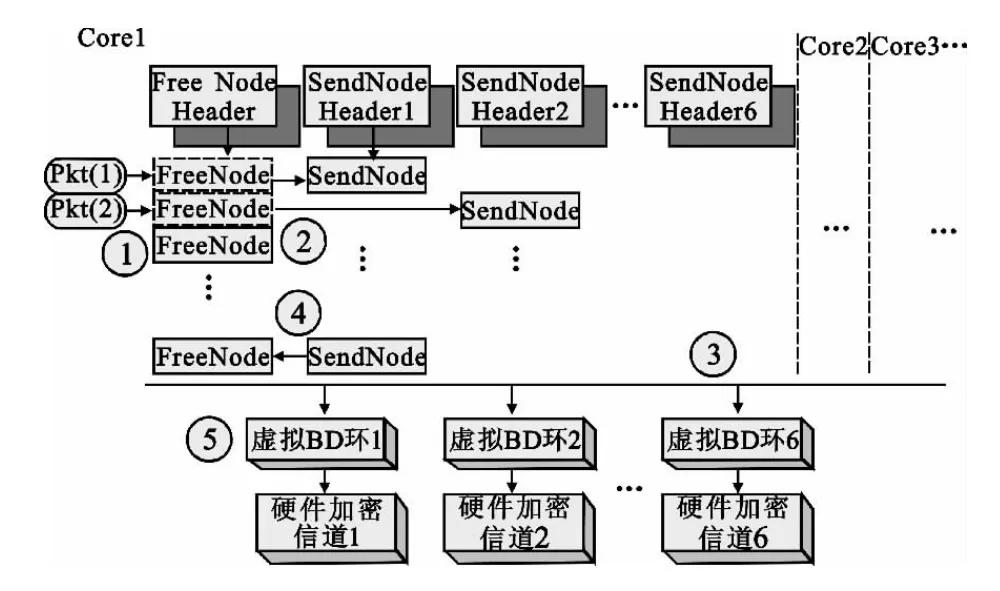

常用的加密模式分为ECB模式和CBC模式[4],本加密系统采用CBC模式。加密卡共有6个独立的CBC加解密通道,每个加解密通道的DDR缓存大小为3 MB,因此,每个加解密通道对应的虚拟BD环长度设为2048,即每个加解密通道同时收到的加解密报文最多为2048个。处理器中含有7个数据转发核,每个转发核绑定1个发送任务(Tx Job),用于发送加解密报文到以太通道。同时,由于加密卡中含有6个独立的加解密通道,因此设计6个发送队列(SendNode),分别对应6个虚拟BD环和加解密通道,发送队列头定义为SendNode Header。除此之外,每个转发核绑定1个预先分配好的FreeNode队列,供本转发核上的6个SendNode队列从中取出缓存空间,缓存排序报文并入Send-Node队列,FreeNode队列头为FreeNode Header,其队列最大长度为4096。

2.2 异步加解密工作流程

加密卡的数据处理流程都是送数据到加密卡,然后等待返回处理结果的过程[5]。同步和异步方式都可以实现对数据的加解密,然而同步方式处理速度较慢,无法满足高性能设备的效率要求。根据需求,选择异步方式实现驱动程序。

待加解密数据通过路由器主机端的IPSec层调用驱动程序发送接口,将待加解密的数据发送到驱动层,驱动层接收到IPSec发来的数据后按照图3的异步加解密流程进行缓存处理,并将待加解密数据报文记录至虚拟BD环,通过10G以太通道发送至加密卡进行加解密。从图3中可以看出,整个异步处理流程可分为5个步骤,下面依据图中标号进行详细论述。

图3 异步加解密流程Fig.3 Asynchronous encryption flow chart

1)为IPSec层传入的需要加解密的报文申请Node缓存节点缓存该报文,对应的Node节点从FreeNode Header队列中出队,然后完成报文的处理和封装并将信息缓存至Node节点。

2)将Node缓存节点挂接至对应的SendNode Header队列,对应挂接至哪一个队列根据上层IPSec传入的加解密通道号决定,该通道号在配置隧道时已经预设好了。

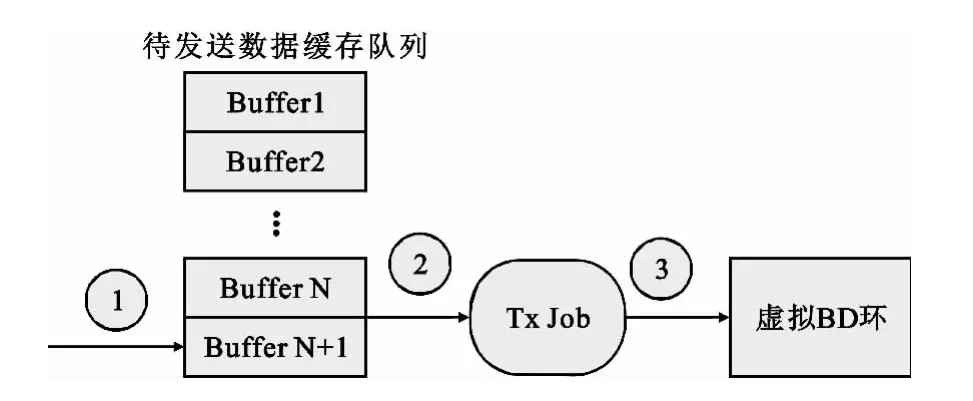

3)7个发送核core1—core7通过Tx Job同时对各自的6个发送队列SendNode Header进行出队,从而可以更加高效的利用硬件加解密通道。同时为考虑每个发送核中6发送个队列的负载均衡,避免从1个固定的队列一次性全部出队过后再进行下一队列的操作,每个队列发送8个报文后即转向下一队列进行发送操作。最后,将出队的Node信息同步至虚拟BD环,此时需要考虑不同Core对虚拟BD环的同时操作,需要互斥锁进行保护,如图4所示。

图4 发送任务过程Fig.4 Transmit job process diagram

4)此时Node缓存节点的使命已经完成,被释放回原有的FreeNode Header队列中等待后续报文的处理。

5)将报文信息记录至虚拟BD环上,调用对应的以太通道发送函数将报文通过10G以太通道发送至加密卡FPGA进行加解密。

至此,待加解密数据已由路由器主机端发送至加密卡,接下来将由硬件加密卡完成对数据的加解密处理。当数据由加密卡加解密完成后,加密卡通过10 G以太通道将加密后的报文发送回路由器主机端。驱动层的数据接收任务通过不断轮询,当发现有加解密完成的数据收回时,调用相应的接收处理函数解锁对应虚拟BD环,完成报文解析并将数据部分送回IPSec层,由IPSec层完成后续处理,从而完成整个报文的一个处理流程。

3 性能测试

目前国内加密卡实现的加密速度一般不超过2 Gb/s[6]。为测试驱动程序的稳定性和性能,在VxWorks操作系统下设计完成驱动程序后,进行了单包加解密测试,裸跑速率测试,IPSec流量测试。单包加解密测试中,由驱动程序自己构造加解密报文,发送给加密卡进行加解密,然后将单包加解密结果与理论结果比较,验证了加密驱动工作正确。为测试加密驱动的板卡级速率,驱动程序为每个转发核构造了2000个长度为1400 B的报文,共14000个报文(7个转发核)发送到加密卡进行加解密,待加密报文全部加密完成返回驱动层时,计算所有报文加解密所用时间(精确到微秒),由此可计算出驱动层数据收发速率。计算公式为:PPS=2000×7/加密所用时间,bps=2000×7×1400×8/加密所用时间。最后,由IPSec层调用驱动收发数据进行流量测试,将整个加密系统进行了长时间的完整测试,未出现异常。测试结果如表1所示。

表1 加解密测试结果Table 1 Encryption test result

4 结语

本文基于多核处理器设计了一种加密卡异步并行驱动,并对其软硬件架构及缓存和数据收发流程做了详细介绍。通过性能测试可以看出,驱动程序运行稳定且具较高的数据收发速率,达到了预期目的[7]。本加密卡所设计的异步驱动程序,基于的处理器有7个转发核,加密卡中存在6个加解密通道,若在实际设计中转发核数目和加密通道数目发生变化,只需将相应的缓存队列数目改变即可,数据收发流程依然相同。可见本驱动程序具有良好的可扩展性和兼容性,在信息安全领域具有良好的应用前景。

[1]郭兰.加密卡的研制与加密算法的FPGA实现[D].成都:电子科技大学,2004.GUO Lan.Encryption Card Research and Implement of Encryption Algorithm in FPGA[D].Chengdu:University of Electronic Science and Technology of China,2004.

[2]彭阳,孟李林,李年,等.基于FPGA的高速加密卡设计与实现[J].电子科技,2013,26(06):42-45.PENG Yang,MENG Li-lin,LI Nian,et al.High Speed Encryption Card Design and Implement Based on FPGA[J].Electronics Technology:2013,26(6):42-45.

[3]朱作付,徐超,葛红美.基于DES和RSA算法的数据加密传输系统设计[J].通信技术,2010,43(04):90-92.ZHU Zuo-fu,XU Chao,GE Hong-mei.Design of DES and RSA-Based Data Encryption Transmission System Design[J].Communication Technology:2010,43(04):90-92.

[4]帕尔·佩尔茨儿.深入浅出密码学—常用加密技术原理与应用[M].马小婷译.北京:清华大学出版社,2012:118-122.MA Xiao-ting(translator).Understanding Cryptograph-a Text Book for Students and Practitioners[M].Beijing:Tsinghua University Press,2012.

[5]陈亚东,林为民,张涛,等.基于x86的高速加密卡异步并行驱动设计[J].电力系统自动化,2010,34(10):93-96.CHEN Ya-dong,LIN Wei-min,ZHANG Tao,et al.High Speed Asynchronous Parallel Driver Design Based on x86[J].Automation of Electric Power Systems:2010,34(10):93-96.

[6]孔洁.基于DSP的加密网卡的设计与实现[D].北京:北京工业大学,2005.KONG Jie.Encryption Network Card Design and Implementation Based on DSP[D].Beijing:Beijing University of Technology,2005.

[7]姜明华,丁益祥.Linux下加密卡驱动程序的设计与实现[J].武汉科技学院学报,2004,17(05):51-55.JIANG Ming-hua,DING Yi-xiang.Encryption Card Driver Design and Implement Based on Linux[J].Wuhan Textile University Jouranl:2004,17(5):51-55.