基于VPX平台的数字波束形成实现

2014-09-08章文星

吴 卫,章文星

(中国船舶重工集团公司第七二四研究所,南京211153)

基于VPX平台的数字波束形成实现

吴 卫,章文星

(中国船舶重工集团公司第七二四研究所,南京211153)

数字波束形成一直是雷达和通信工程中的关键技术。本文对数字波束形成原理作了简单的介绍,并在基于VPX开发平台上进行了数字波束形成的硬件实现。

数字波束形成;VPX;FPGA

0 引 言

随着作为雷达观测对象的各种飞行器性能的不断提高、雷达工作环境的不断恶化以及雷达应完成任务的增多,对雷达的发展提出了新的要求。老体制雷达已经无法适应时代的发展规律,必须要发展新体制雷达,而波束形成技术在这种情况下被提出来。传统的波束形成无论是在高频还是在中频实现都是硬件的模拟方法。这种方法的设备量大,硬件复杂,波束指向不易改动。数字波束形成(Digtal Beam Forming,DBF)是在原来模拟波束形成原理的基础上引入数字信号处理方法后建立起来的一门雷达新技术。这种技术充分利用了阵列天线所检测到的空间信息,可以方便地获得超分辨和低副瓣的性能,实现波束扫描、自校准和自适应波束形成等。DBF技术的成功应用必将对现代雷达技术的发展产生重大影响。本文充分利用FPGA资源丰富、处理灵活的优势,在基于VPX开发平台上进行了DBF的硬件设计实现。

1 DBF的基本原理

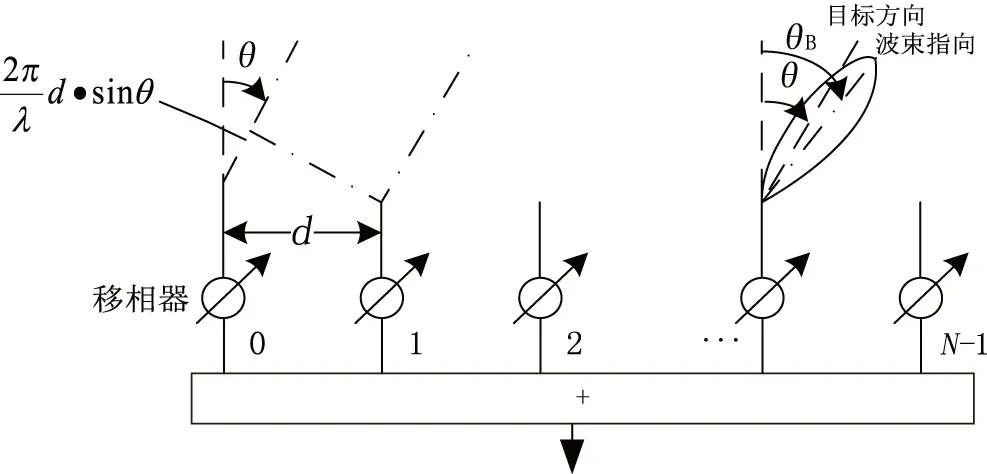

数字波束形成就是用数字处理方法, 对于某一方向入射信号, 补偿由于天线单元在空间位置不同带来的电磁波传播路程差而导致的通道间相位差, 实现信号同相叠加, 从而实现该方向的最大能量接收。传统的模拟波束形成过程是在中频载波或射频载波上对各阵元信号进行移相和模拟合成,而数字波束形成则采用数字电路实现这个模拟过程。图1为简化的线阵示意图。

图1 N单元阵列图

这里对数字波束形成的实现过程作一简单的理论推导。图1 所示的线阵单元之间的“空间相位差△φ”与“阵内相位差△φB”分别为

(1)

(2)

在用数字方法形成接收波束时,△φB按预定的波束指向θB由计算机或数字信号处理机提供。对于第i单元,在某时刻的接收信号为

Ii=ai0cos[△φ0+i△φ]

(3)

Qi=ai0sin[△φ0+i△φ]

(4)

式中,△φ0为回波信号与本振信号的相位差,ai0为各单元的幅度信息。

如果要形成多个波束,每个波束指向不同,设第K个波束指向为θBK,则应提供的阵内相位补偿值应为△φBK:

(5)

进行相位补偿后,I,Q路信号输出为

Ii′=ai0cos[△φ0+i△φ-i△φBK]

(6)

Qi′=ai0sin[△φ0+i△φ-i△φBK]

(7)

由式(3)、(4)、(6)和(7)可得下式:

Ii′=Iicos(i△φBK)+Qisin(i△φBK)

(8)

Qi′=-Iisin(i△φBK)+Qicos(i△φBK)

(9)

将式(8)和(9)写成矩阵形式为:

(10)

因此,由上文的推导可以看出,作一次矩阵变换、4次实数乘法与2次加法即可完成一个相位补偿。

在线阵单元波束扫描范围内,线阵天线方向函数F(θ)可表示为

(11)

2 硬件实现

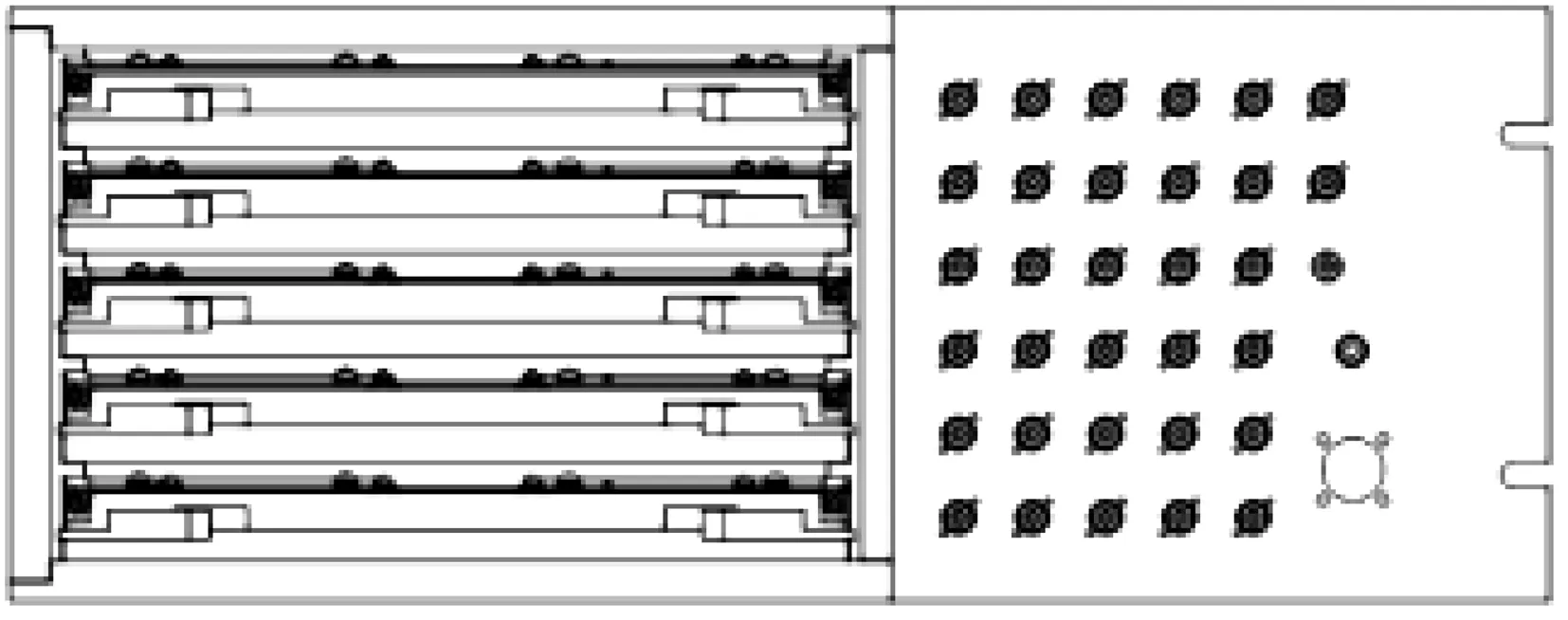

数字波束形成的硬件部分主要由基于FPGA芯片的VPX平台实现。硬件平台前视图如图2所示。

图2 硬件平台前视图

5块VPX板卡水平放置,由上到下依次是PowerPC处理板、光纤接口板、FPGA信号处理板0、FPGA信号处理板1和FPGA信号处理板2。

FPGA信号处理板是基于XILINX公司VIRTEX5系列FPGA信号处理芯片的高性能高速信号处理板,在VPX硬件平台中总共有3块。该板采用6片XC5VSX95T FPGA芯片,可以接受光纤板输出接口的数据,可以对信号进行板内缓存、大规模的预处理算法的实现、实时数据的发送等功能。

光纤接口板是基于AVAGO公司QSFP光电转换模块的接口板卡。该板采用9个QSFP光电转换模块,实现电信号与光信号的转换。本系统中用8个QSFP模块实现单向数据接收,1个QSFP模块实现单向数据发送。

各个FPGA信号处理板同光纤接口板之间的互连关系如图3所示。光纤接口板上载有1片XC5VLX50T以及9个AVAGO公司QSFP光电转换模块,其中一个QSFP模块直接连接到XC5VLX50T上,其余8个QSFP模块通过光纤接口板的P2和P3槽连到FPGA信号处理板0及FPGA信号处理板1上。3块FPGA信号处理板上各载有6片XC5VSX95T FPGA芯片,分别标记为FPGA0到FPGA5,其中FPGA0和FPGA1接收来自光纤处理板上8个QSFP模块通过GTP协议送入的数据,FPGA2和FPGA3主要实现的是3块FPGA处理板之间的数据通过GTP协议进行传输,FPGA4和FPGA5暂未用到。

图3 光纤接口板和FPGA信号处理板之间的连接关系

图3中P0~P7表示光纤处理板上的8个光模块,F0~F3表示FPGA处理板上的4片FPGA。

3 软件设计

软件设计整个流程为:首先在光纤接口板中模拟16路前端TR组件送来的I/Q信号,并设置该16通道间信号相位差为45°,以假设目标从45°方向向线阵照射。FPGA处理板0和1的FPGA0和FPGA1同时接收由光纤板送入的相位差为45°的16bit的16路IQ信号也就是每片FPGA接收4路IQ信号,之后将各路数据进行同步,并进行第一级片内的DBF合成。将FPGA0的第一级DBF合成结果通过LVDS传送到FPGA1上,并和FPGA1上的第一级DBF合成结果进行同步,之后进行第二级板内的DBF合成,并将第二级DBF合成结果都通过LVDS送到FPGA3上,将FPGA处理板1的FPGA3收到的第二级DBF合成结果通过GTP送往FPGA处理板0的FPGA3上,在FPGA处理板0的FPGA3中将通过GTP收到的FPGA处理板1的第二级DBF合成结果和通过LVDS收到的FPGA处理板0的第二级DBF合成结果进行同步,之后进行第三级板间的DBF合成,得到最终的数字波束合成结果。

图4为整个VPX硬件平台实现板间数据流收发、同步、DBF合成等流程的框图。

图4 软件设计流程的框图

下面以FPGA处理板0上的FPGA0为例介绍软件设计流程。

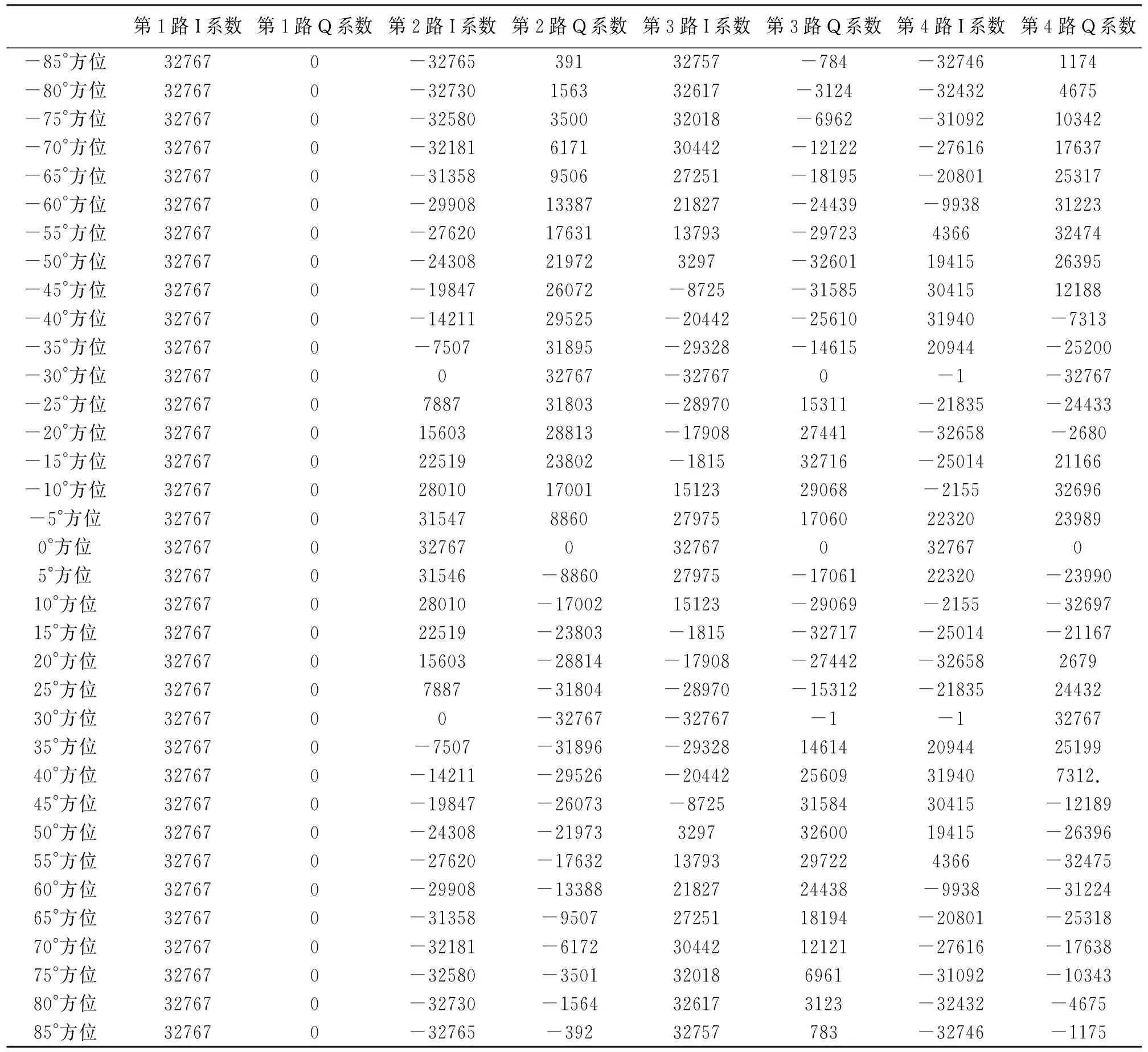

FPGA处理板0上的FPGA0前端送入为四路入射角相差45°的模拟IQ信号,信号的脉宽和频率均为0.4 μs和5 MHz,采样率为125 MHz,天线单元间距为半波长即d/λ=1/2, 入射角θ为45°。将各参数带入式(1),分别计算出-85°~85°共35个波位对应的DBF系数(幅度采用矩形窗进行加权)。由于FPGA一般不支持浮点运算,所以计算结束后还要将各组系数乘以215,并取整,从而完成16位量化。所得的系数如表1所示。

FPGA处理板0上的FPGA0前端接收到的四路信号分别为I1+jQ1、I2+jQ2、I3+jQ3和I4+jQ4。

由式(10)所示,分别将这四路信号和某一方位的波束对应的四路系数进行复数乘法运算,则求得DBF在该方位的第一级DBF合成结果。

(I1+jQ1)×(I第一路系数+jQ第一路系数)

(12)

(I2+jQ2)×(I第二路系数+jQ第二路系数)

(13)

(I3+jQ3)×(I第三路系数+jQ第三路系数)

(14)

(I4+jQ4)×(I第四路系数+jQ第四路系数)

(15)

同样方法可以先计算出FPGA处理板0上的FPGA1、FPGA处理板1上的FPGA0及FPGA处理板1上的FPGA1的其他3组35个DBF系数,再使用同样方法求得各FPGA片上的第一级DBF合成结果。

第二级DBF合成是将FPGA0的第一级DBF合成结果通过LVDS送入FPGA1中,并同FPGA1中的第一级合成结果相加而得。

表1 FPGA处理板0上的FPGA0中对应的35个DBF系数

第三级DBF合成是将FPGA处理板1的第二级DBF合成结果通过GTP结果送入FPGA处理板0中,并同FPGA处理板0中的第二级DBF合成结果相加而得。

4 试验结果

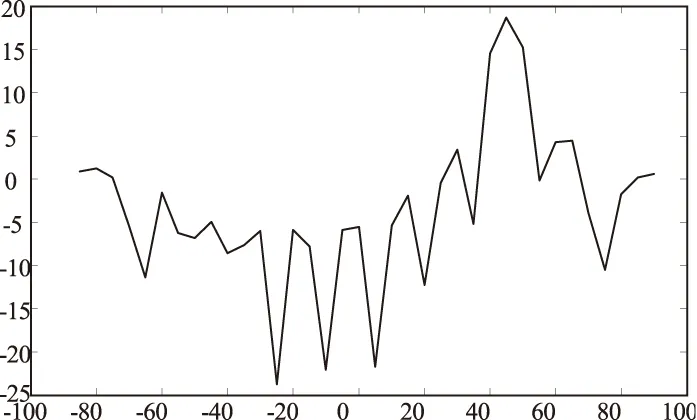

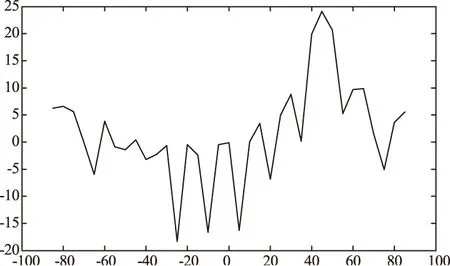

将收到的16路信号分别和-85°-80° -75° -70° -65° -60°-55° -50° -45° -40° -35° -30° -25° -20° -15° -10° -5° 0° 5° 10° 15° 20° 25° 30° 35° 40° 45° 50° 55° 60° 65° 70° 75° 80° 85°共35个方位波束对应的DBF系数进行DBF合成,再在合成结果的基础上求出相对功率。这样每个DBF系数就对应一个相对功率值。将这35个值做图如图5所示。再根据线阵方向图函数式(11),在MATLAB中进行仿真,仿真结果如图6所示。可见,所得到的DBF方向图和理论的DBF方向图基本一致,从而验证了DBF结果的正确性。

图5 试验所得的DBF方向图

图6 理论的DBF方向图

5 结束语

本文首先介绍了DBF合成的理论算法,并在基于VPX硬件平台上实现了DBF合成,并且验证了DBF合成结果的正确性。随着信号处理器和FPGA 的高速发展,数字波束形成技术在现代雷达与通信等领域中将得到广泛的应用。

[1] 张光义.相控阵雷达原理[M].北京:国防工业出版社,2009.

[2] 曹钢.基于FPGA的数字波束形成研究[D].西安:西安电子科技大学,2007.

[3] 朱荣新,方姚生.雷达数字波束形成器的研究与实现[J].现代雷达,2003(2).

Implementation of digital beam forming based on VPX platform

WU Wei, ZHANG Wen-xing

(No. 724 Research Institute of CSIC, Nanjing 211153)

Digital Beam Forming (DBF) is the key technology in radar and communication engineering. The basic principle of the DBF is briefly introduced, and its hardware implementation is accomplished based on the VPX platform.

DBF; VPX; FPGA

2014-04-03;

2014-05-24

吴卫(1977-),男,工程师,硕士,研究方向:雷达信号处理;章文星(1969-),男,高级工程师,研究方向:雷达结构设计。

TN957.51

A

1009-0401(2014)03-0011-04