基于SOPC的UART IP核设计与驱动开发及系统移植

2014-09-03崔旭晶李天雷

崔旭晶,李天雷

(1.沈阳理工大学 信息科学与工程学院,辽宁 沈阳 110015;2.中航工业沈阳发动机设计研究所 辽宁 沈阳 110015)

基于SOPC的UART IP核设计与驱动开发及系统移植

崔旭晶1,李天雷2

(1.沈阳理工大学 信息科学与工程学院,辽宁 沈阳 110015;2.中航工业沈阳发动机设计研究所 辽宁 沈阳 110015)

设计基于SOPC嵌入式系统的UART IP核,依据UART协议,采用Verilog HDL进行各模块设计,使用ModelSim、Quartus II作仿真验证及综合,结果表明该UART IP核功能正确,稳定可靠。根据Avalon总线接口协议实现UART在系统总线上的挂载,建立SOPC嵌入式硬件系统,进行UART IP核驱动开发。利用超级终端实现嵌入式系统与上位机之间的通信,并成功移植uClinux操作系统,实现对嵌入式系统的高级控制。

SOPC;UART;Avalon总线;IP核;uClinux.

计算机通信主要通过串口、并口和网络,UART是计算机串行数据通信的重要部分,而对嵌入式系统的访问主要通过UART通信,UART IP核在FPGA开发中应用广泛,可移植到专用ASIC设计中。SOPC嵌入式技术是一项软硬件协同的设计技术,它融合了MCU、ASIC、DSP等器件的优点,具有可编程的灵活性和丰富的IP核支持,为控制系统设计提供了一种更为灵活高效的解决方案[1]。uClinux操作系统是针对没有MMU(内存管理器)的CPU,它被使用在具有超前网络功能的嵌入式领域,如ARM7/9、MIPS、SH、ColdFire and BlackFin等,uClinux操作系统很好地完成了把内核、C库、应用开发融合在一起的任务,并且占用很少的资源。

1 UART IP核设计

根据UART协议,UART IP核包含4个模块,分别为寄存器模块、波特率模块、发送模块、接收模块[2]。

1.1 寄存器模块设计

由UART协议可知,数据在传输之前必须保证两端设置一致才能使数据正确地传输。寄存器模块主要完成对设计的配置,包括:波特率选择、数据位选择、停止位选择、中断使能、各种情况下的状态位。寄存器模块内部设有4个寄存器:status、rxdata、txdata、control。

1)status寄存器

状态寄存器由指示UART内部状态的多个独立状态位组成,每个状态位与控制寄存器中的中断允许位一一对应。软件可以随时读取状态寄存器而不会改变其内容。

2)rxdata寄存器

rxdata寄存器用来保存rxd输入端接收到的数据。当一个新的字符通过rxd输入端接收完毕时,它被传送到rxdata寄存器,且状态寄存器的rflag位被置1;当rxdata寄存器中数据被读取时,rflag位被清0。在新数据到来之前rxdata寄存器中数据要被读取,无论数据是否被读取新的数据都会覆盖旧的数据。

3)txdata寄存器

主设备将要发送的字符写到txdata寄存器,发送模块没有准备好之前,不应该写字符到txdata寄存器。状态寄存器中tflag位表示txdata寄存器状态,当有一个数据要被发送时tflag位被置1;当数据被装载到移位寄存器时tflag位清0。在新数据被写入之前旧数据要被发送出去,否则新数据将会覆盖旧数据。

4)control寄存器

control寄存器由多个控制位构成,每一位又可分别控制UART核的相应内部操作,软件可随时读取其中的值。control寄存器可以对设计中数据位的位数、停止位的位数、波特率选择进行配置。control寄存器中的每一位允许status寄存器中相应位irq,当某一个状态位和它的中断允许位均为1时,UART核产生一个中断irq。

1.2 波特率模块设计

UART传输数据是通过数据两端设备来配置相同波特率以确定数据传输速率。波特率模块的功能是根据不同波特率而产生相应的传输时钟频率,设计中使用115200、9600两个波特率,则时钟分频数=系统时钟频率/波特率。系统时钟为50 MHz,当波特率为115200时对系统时钟433分频,当波特率为9600时对系统时钟5219分频。分频主要通过计数器来完成。

发送模块时钟频率和接受模块时钟频率不一样,接收时钟要在发送时钟的基础上进行16分频。

1.3 发送模块设计

发送模块的功能是将数据正确地发送出去。就是把从Avalon总线写入rxdata寄存器的数据,根据UART协议要求的数据格式发送出去,其中包括:串并转换、数据寄存器转换、数据移位、开始位和停止位添加。

发送模块将接收到的数据进行并串转换后传送到移位寄存器,移位寄存器向外移数据时在字首加入起始位,在字尾加入停止位。数据传输过程通过状态机实现,数据传输分4个状态,即idle空闲状态、start起始状态、shift转移状态、stop停止状态,每个状态实现不同功能,在信号激励后进行状态转移,4个状态全部转换一遍完成一次数据发送。

1.4 接收模块设计

接收模块的功能是检测接收数据。将接收数据去掉起始位,停止位,把数据位串并转换后传送到rxdata寄存器,等待系统读取数据。

对于UART核来说接收模块比发送模块复杂,接收模块要对接收数据进行采样来检测其数据的正确性。具体采样过程是将接收数据采16个样值,当其中大于8位数为1时说明采样数据为1;当其中大于8位数为0时说明采样数据为0。数据传输过程依然采用状态机实现,分为3个状态,即idle空闲状态、shift移位状态、stop停止状态。接收模块比发送模块少了一个start起始状态,是因为接收模块中并没有发送起始位[3]。

1.5 UART IP核仿真验证

1.5.1 ModelSim仿真

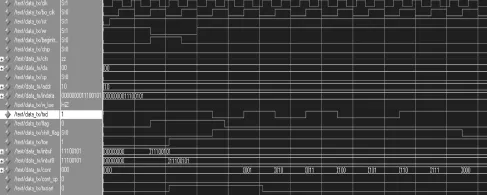

1)波特率模块

波特率模块仿真主要看内部计数器是否计数,在相应的计数值是否产生时钟。波特率模块仿真波形图如图1所示。

图1 波特率模块仿真波形图Fig.1 Baud module simulation waveforms

在cont_rxd_high为13时clk_out_txd变 为1,在cont_ txd_high为216时clk_out_txd变为1,波特率模块验证正确。

2)发送模块

发送模块仿真主要查看输入数据是否能够正确输出。发送模块仿真波形图如图2所示。

图2 发送模块仿真波形图Fig.2 Send module simulation waveforms

准备发送的数据为11100101,当txstart为1时数据开始发送,先发送起位0,数据位再一位一位地移送出去,发送模块验证正确。

3)接受模块

接受模块仿真是查看数据是否正确地接收。接受模块仿真波形图如图3所示。

接受到的起始位为0,数据位10100110被一位一位地传送到移位寄存器中,接受模块验证正确。

图3 接受模块仿真波形图Fig.3 Accepted module simulation waveforms

1.5.2 Quartus II综合和布局布线

使用Quartus II软件将SOPC生成的HDL代码进行综合和布局布线,最终生成的文件下载到FPGA开发板上。综合后出现器件列表,其中包含器件型号,使用寄存器数量,使用逻辑单元数量,使用管脚数量,使用PLL数量等。

2 硬件系统搭建

2.1 最小系统搭建

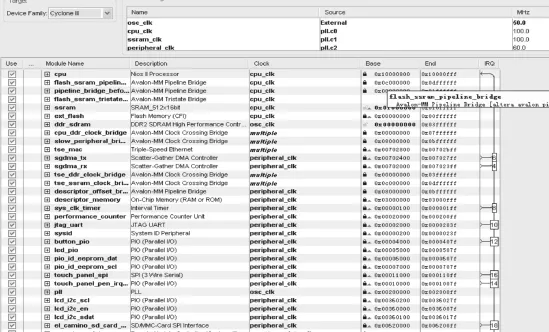

该系统用于对UART IP核测试,系统比较简单只需几个组件。使用SOPC Builder硬件平台工具,配置最小系统组件包括:Nios II/s、On-Chip Merory、JTAG_UART、UART。其中:Nios II/s处理器使用标准型级别就可满足功能需求,不需要选中MMU(内存管理器)。On-Chip Merory有两个片上存储器RAM和ROM,RAM存储数据,由于设计将会使用Printf函数,RAM必须选择64KB以上;ROM存取程序,由于程序不大选择8KB即可。UART用于测试自定义UART IP核。首先将UART IP核加到SOPC组件中,同时系统会生成tcl文件,该文件描述了自定义IP的所有系统,可以修改此文件对自定义IP的所有信息进行修改。JTAG_UART用于对程序下载调试[4]。最小系统的SOPC组件列表如图4所示。

图4 最小系统的SOPC组件列表Fig.4 SOPC component list of the minimum system

2.2 嵌入式系统搭建

该系统用于完成uClinux系统移植,系统比较复杂需要大量组件。主要组件有:Nios II/f、Pipeline Bridge、Tristate Bridge、SRAM、Flash、DDR SDRAM、Clock Crossing Bridge、DMA、PIO、Triple-Speed Ethernet、PS2、PLL、Pixel Conventer、Video Sync Gengrator等[6]。其中:Nios II/f处理器是CPU的最高配置,由于系统比较复杂,需要快速型级别才能满足系统需求。DDR SDRAM控制器,由于SDRAM的读取速度比Flash快很多,通常用来运行软件程序。Clock Crossing Bridge时钟桥,用于不同时钟频率下的数据传输,内部主要由异步FIFO组成。PLL锁相环,当系统需要多个时钟驱动时,仅靠一个外部晶振不可能满足要求,必须加入PLL提供不同时钟,这里60MHZ用于低速外部接口控制器,100MHZ给CPU供时,133MHZ给SDRAM供时。Pixel Conventer用于RGB数据传输。Video Sync Gengrator用于控制LCD[6]。嵌入式系统的SOPC组件列表如图5所示。

在实际搭建嵌入式系统时,许多器件配置不仅要考虑外围芯片的时序要求,还要考虑内部系统总线的时序要求。每个组件都必须有自己的时钟、基地址,为每个组件正确地分配地址是比较复杂的。由于CPU的寻址空间为4GB,通常把0x00000000到0x1FFFFFFF作为寄存器地址空间。可以把同一个时钟频率的组件划为一个地址空间区。组件的实际地址等于基地址加地址偏移量。

3 UART 驱动开发

UART驱动开发是利用超级终端实现SOPC嵌入式开发板(Altera公司的EP3C40 FPGA开发套件V6工作平台)与上位机之间的正常通信,即PC机向开发板发送数据,同时开发板把接收的数据再发送给PC机,在超级终端上回显。

Nios II IDE集成开发环境用于完成基于Nios II系统的软件开发和调试,Nios II IDE提供了HAL系统库里的两个重要文件,一个为system.h系统描述文件,提供Nios II系统硬件的软件描述;另一个为io.h文件,io接口操作文件提供了3种对io口操作的函数,即对8、16、32位数据操作函数,由于UART IP核采用32位静态地址对齐方式,故软件 使用对32位数据操作函数IORD、IOWR,这两个函数的功能是将数据写/读到基地址+偏移量*数据总线位数/8。

UART的测试软件流程为:首先对control寄存器初始化(写入0x0000),然后系统不断查询status寄存器的rflag位,当rflag位为1时说明rxdata寄存器接收了一个新数据;当tflag位为0时说明txdata寄存器为空可以写入数据,将接收到的数据写到txdata寄存器中,发送给PC机,最终在超级终端上能够显示发送和接受的数据。

图5 嵌入式系统的SOPC组件列表Fig.5 SOPC component list of the embedded system

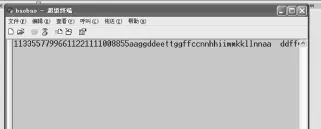

在使用超级终端测试之前必须对超级终端进行设置,在超级终端属性栏的“ASCII码设置”里,把“ASCII码接收”、“ASCII码发送”全部选中,只有这样才能在超级终端上查看发送的数据。经测试,每发送一个数据都能在超级终端正确回显,如图6所示。

图6 在超级终端上的数据回显Fig.6 Data on the HyperTerminal echo

4 uClinux系统移植

4.1 建立有关文件系统

向SOPC嵌入式系统开发板移植uClinux操作系统主要是为了更自主地开发,实现系统更高级功能。uClinux操作系统是针对没有内存管理器的微处理器的操作系统。这里移植的nios2-linux-20100621,需要从Altera官方网站下载系统源代码,由于该系统使用git进行管理,在移植系统之前必须具备EPEL安装包,其为远程软件仓库管理软件。nios2-linux-20100621软件包里面几乎没有什么软件包,必须安装git、make、gcc等相关软件。要在PC机上编译Nios II程序,需要安装交叉编译器nios2gcc-20080203.tar.bz2。

4.2 移植系统

系统移植需要两个很重要的文件nios.h和config.c。开发包通过nios.h文件来管理SOPC组件与uClinux内核驱动设备的地址映射;config.c文件包含了大部分设备驱动支持,各个设备要通过读取该文件来获得设备驱动支持。

在移植前必须将两个文件里的内容对比一下,检查两个文件的宏定义是否相同。进入uClinux-dist目录输入make menuconfig配置内核,如果第一次配置内核必须选择默认选项,再生成镜像文件,保存退出后系统会显现有错误,因为没有指定PTF文件(PTF文件是SOPC生成的系统文件,里面定义了所有关于SOPC组件的信息),把系统生成的PTF文件复制到/opt目录下,定义为nios.ptf。在uClinux-dist目录下执行配置硬件信息文件命令make vendor_hwselect SYSPTF=/opt/nios.ptf之后,系统提示选择CPU以及运行程序的存储器,选择后就可以配置内核了。

Nios2-linux-20100621通过git来管理,输入git-branch-l查看分支列表,转到test-nios2 branch目录下。执行make menuconfig后,进入系统自定义配置列表,可以根据自己需要配置内核,比如开发板类型选择。控制台选择UART,保存退出系统会进入应用程序配置,可以在这里配置文件系统GUI、Busybox等,保存退出后,输入make命令来制作系统映像文件,映像文件生成在image文件里的zImage,到此uClinux移植完毕[7]。

启动nios2 command shell,将生成的zImage烧写到开发板的SDRAM中,同时打开超级终端,超级终端显示的系统加载如图7所示。

在超级终端中输入ls命令,到此系统移植成功,超级终端显示的系统文件如图8所示。

5 结束语

使用Altera公司的Cyclone III为FPGA开发芯片,经过基于Avalon总线的UART IP核设计及其驱动过程,在SOPC嵌入式硬件系统[8]中加以实体性验证,表明自定义设计的UART IP核各项功能均达到预期要求,实现了UART的通信功能和uClinux操作系统移植。这种设计方法大大缩短了嵌入式系统的软硬件开发时间,增加了系统的灵活性、扩展性和实用性,有效地提高了系统的开发效率,是当今科技含量较高的设计思路及实现方法,具有广阔的应用领域和前景。

图7 超级终端显示系统加载Fig.7 HyperTerminal display system load

图8 超级终端显示系统文件Fig.8 HyperTerminal display system files

[1] 周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006:16-21.

[2] 李秋菊,杨银堂,高海霞.基于Verilog HDL的UART IP的设计[J].半导体技术,2007,32(6):520-523.

LI Qiu-ju,YANG Yin-tang,GAO Hai-xia.Design of UART Based on Verilog HDL[J].Semiconductor Technology,2007,32(6):520-523.

[3] 邓伟,徐扬婧.基于SOPC技术的异步串行通信IP核的设计与实现[J].电子设计工程,2012,20(3):185-188.

DENG Wei,XU Yang-jing.A UART IP Implementation Based on SoPC[J].Electronic Design Engineering,2012,20(3):185-188.

[4] 王刚,张潋.基于FPGA的SOPC嵌入式系统设计与典型实例[M].北京:电子工业出版社,2009:250-282.

[5] Altera Corporation.SOPCBuilderUserGuideVersion1.0[EB/OL].[2010-12-01].http//:www.altera.com.cn/literature/ug/ug_sopc_ builder.pdf.

[6] Altera Corporation.Embedded Peripherals IP User Guide[EB/OI].[2010-12-01].http//:www.altera.com.cn/literature/ug/ug_ embedded_ip.pdf.

[7] 巨政权,原亮,满梦华,等.SOPC系统建立及uClinux移植实现[J].微计算机信息,2009,25(11):43-45.

JU Zheng-quan,YUAN Liang,MAN Meng-hua,et al.Establishment of SOPC System with Implementation of uClinux[J].Microcomputer Information,2009,25(11):43-45.

[8] 薛慧敏,武传华,路后兵.基于SoPC的分布式干扰系统嵌入式网关设计[J].现代电子技术,2011(6):121-123,127.

XUE Hui-min,WU Chuan-hua,LU Hou-bing.Design of distributed jamming system embedded gateway based on SoPC [J].Modern Electronics Technique,2011(6):121-123,127.

UART IP core design and driver development and system transplanted based on SOPC

CUI Xu-jing,LI Tian-lei

(1.School of Information Science and Engineering,Shenyang Ligong University,Shenyang 110015,China;2.AVIC Shenyang Engine Design and Research Institute,Shenyang 110015,China )

UART IP core Design of embedded systems based on SOPC,according to UART protocol,using Verilog HDL conducted each module design,using ModelSim,Quartus II for simulation and synthesis results show that the UART IP core functions properly,stable and reliable.According to the Avalon bus interface protocol UART mounted on the system bus,achieved the establishment of SOPC embedded hardware system for UART IP core driver development.Use HyperTerminal for communication between the host computer and embedded systems,and successfully transplanted uClinux operating system,advanced control for embedded systems.

SOPC;UART;Avalon bus;IP core;uClinux.

TN332

A

1674-6236(2014)11-0121-05

2014-02-19 稿件编号:201402098

辽宁省教育厅高校科研计划项目(L2010482)

崔旭晶(1964—),女,天津人,硕士,副教授。研究方向:嵌入式技术、集成电路设计。