电脑芯片的新技术

2014-08-13

很快,芯片业将面临穷途末路,因为物理定律将阻碍新一代芯片的开发,而目前无处不在的台式电脑、笔记本电脑、平板电脑和智能手机的发展都依赖于新的芯片。现在,电脑行业的发展仍然遵循摩尔定律:50年前英特尔的共同创始人曾预测,每24个月芯片上的晶体管数量将增加1倍。时至今日,世界上最大的芯片制造商英特尔仍然遵循摩尔定律,每两年一次地努力缩小晶体管的尺寸,以便在芯片上集成更多的晶体管。例如英特尔最新的Haswell处理器是由约14亿个晶体管组成,而10多年前的一个奔腾4处理器的晶体管不到1亿个。而除了英特尔之外,三星、台积电和格罗方德等其他主要的芯片生产商,也同样尽自己所能地遵循这一周期。

特定区域内的晶体管数量越多,它们产生的热量就越多,其结果将是出现暗硅(dark silicon,指芯片中停止工作的晶体管),如果按照目前的芯片技术继续发展下去,那么进入2018年,芯片上的晶体管将超过一半无法工作。实际上,根据美国研究人员的一项研究发现,现如今处理器早已无法实现更高的时钟频率,如果勉强为之,芯片产生的热量将会是一个难以解决的问题。为此,制造商开始增加核心的数量,或者使用更多的晶体管提供更大的高速缓存。而未来几年,制造商将面临更大的挑战,无法再依赖于新的生产工艺和继续缩小晶体管的尺寸,他们必须另辟蹊径,以确保芯片能够集成更多的晶体管,继续保持芯片业的发展,否则电脑行业的生命也将终结,而下面是一些可行的方案。

升级晶体管

对于芯片制造商来说,生产出越小的晶体管优势越大:可以提供更快的处理器、更经济的移动设备和比其他竞争对手更大容量的固态硬盘。晶体管实际上是电脑设备的计算和存储单元,一个晶体管电路可以代表1个位。目前,芯片制造商正在使用的晶体管尺寸已经到达了一个连微生物学家也无法企及的维度:流感病毒的直径为80nm~120nm,而最新的晶体管仅有60nm~90nm的宽度。

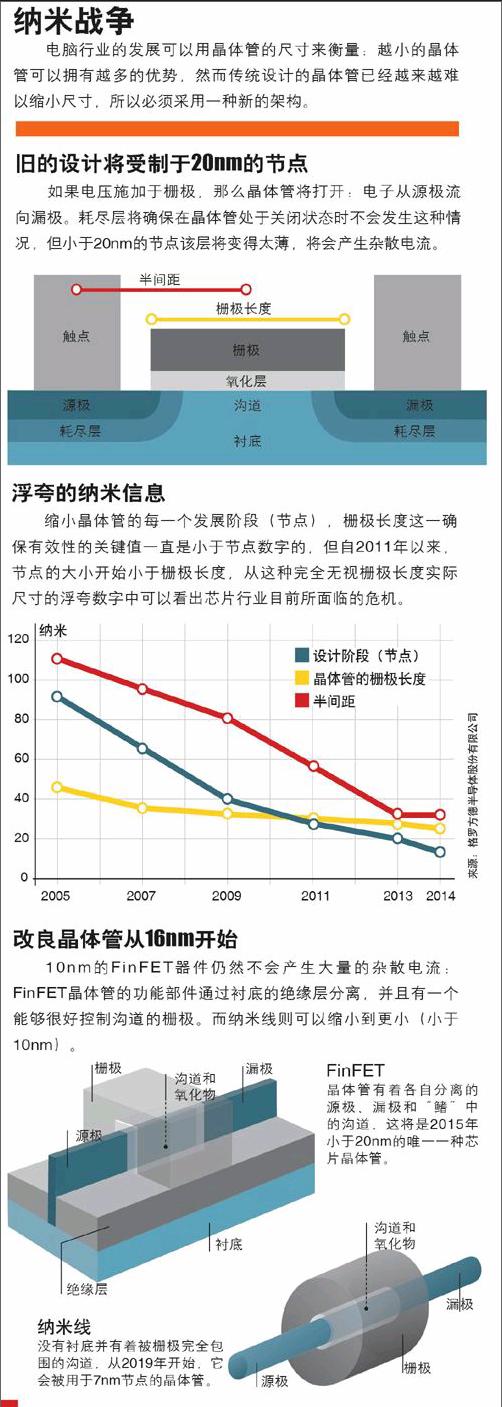

晶体管主要由半导体硅构成,并在其中掺入杂质原子。各种掺杂工艺改变了晶体管的导电性:像原子磷,它的外层比硅原子有更多的电子,可以更容易地成为自由电子,可以用在n型掺杂的源极和漏极。而衬底掺入硼原子是p型掺杂,它将产生可以接受电子的“空穴”。电压被施加于源极和漏极之间的栅极时,电流将流经源极和漏极之间的沟道,晶体管将处于开启状态。如果缩小晶体管的尺寸,尤其是压缩栅极长度,那么晶体管可以更有效地工作,但是p型掺杂和n型掺杂材料之间未掺杂的耗尽层将变得越来越薄,薄到可以被渗透。其结果是,电子没有任何阻碍地从源极和漏极流入衬底,在同一时间,该层电子被迫从源极流动到漏极,所产生的杂散电流将贡献接近40%的功耗。

获得认可的新型晶体管

因此,所有大的芯片制造商的传统晶体管发展都止步于20nm的设计工艺(节点),该节点的大小决定了前面所说的栅极长度已经到了上述问题越来越严重的临界点,因而,如果不改变现有晶体管的设计,那么将无法再缩小晶体管,所有缩小晶体管的设计都只能够存在于纸面上而无法付诸于现实。为此,英特尔开始采用FinFET概念的3栅极晶体管,并且其他的芯片厂商也纷纷效仿,将在2014和2015年采用类似的晶体管。FinFET概念的鳍式场效应晶体管,沟道、源极和漏极在衬底上各自分离,沟道掺杂很少,如果有的话,也只掺杂有很少的外来原子,而衬底没有被掺杂,这将明显地减少杂散电流,并允许节点低至10nm。

不过,FinFET元件的节点大小带有一定的欺骗性,其晶体管的效能有别于节点大小相同的传统晶体管。例如3栅极晶体管栅极长度约为30nm,但在考虑功耗和性能的情况下,其效能大约为22nm。芯片分析师马尔科姆·佩恩估计,大约在2015年节点效能可以达到17nm~20nm之间。而如果希望真正达到10nm以下,需要使用其他材料和再次更改晶体管的架构,例如将FinFET的理念发挥到极致的纳米线,它的功能组件只有源极、沟道、漏极和栅极,沟道被从四面八方包围其中。不过,纳米线目前仍处于研究阶段,研究中的几个原型都没有准备好。

替代硅金属

FinFET器件解决了缩小芯片将产生的诸多问题,并且晶体管的工作电压更低、更节能和切换速度更快,然而缩小的晶体管功能部件(源极、漏极、栅极和沟道)非常薄,“鳍”(栅极)突出,这将产生一个新的问题,那就是芯片制造商必须面对10nm的生产工艺。

2009年以来,“拉伸硅”已用于晶体管的功能组件。所谓“拉伸硅”正是字面上的意思:通过引入锗原子,增加单个原子之间的距离。一个普通的硅层将被放置锗层上,形成硅-锗层(SiGe),两个层的结合形成了规则的结晶晶格。由于SiGe层中原子之间都维持一定的距离,所以晶格的扩大增加了材料的电导率,电子移动通过所连接晶体管的速度比普通硅大约快70%左右。

但在较小的FinFET元件上,“鳍”变得非常薄,它只包含很少的原子层,如果采用拉伸硅技术将变得更加复杂,在10nm的节点之后更无法进一步拉伸,如果硅不能再被用作半导体,缩小晶体管的尺寸没有任何意义。补救的办法是使用可以替代硅的新材料,例如锗,周期表中它位于硅的正下方,完全可以取代硅作为半导体。锗是p型掺杂成分的理想基础物,并且拉伸性质的锗导电系数比硅高4倍多。而n型掺杂铟、镓和砷的混合物(砷化铟镓,InGaAs)是最佳的选择,它的导电系数是硅的6倍多。开发商在比利时鲁汶的校际微电子研究中心(Interuniversity Microelectronics Centre,简称IMEC,世界上最大的独立微电子研究机构校际微电子中心)已经制造出第一个采用InGaAs沟道的原型,它与采用硅沟道的FinFET晶体管相比能耗只有一半。市场分析师预计,这种新材料将在2017年开始量产使用。

单原子层的计算

2020年后,5nm节点将需要更小的组件,同时必须要具备良好的导电性。二维纳米层,也就是每层仅具有一个原子的单层材料是适当的选择,例如石墨烯,这种碳原子组成6边形网格的材料目前正进行深入研究中。而锗、硅、锡等相关的材料也在研究之中,2012年柏林工业大学已经制造出硅烯(Silicene),不过,单分子膜并不能完全取代硅,而是作为硅的补充,因为它们的导电率难以驾驭。

如果以纯石墨烯制作晶体管,那么晶体管将几乎在任何时候都处于打开状态,这将消耗大量的电能。但是单层材料的导电率可以解决缩小晶体管产生的另一个问题,目前快速切换状态的晶体管需要铜线以更快的速度输送电荷,随着晶体管的每一次缩小,这一问题急剧恶化,而单层材料可以扭转这种局面,日本先进工业科学和技术国立研究所的研究人员已经成功地用石墨烯取代铜线,从而实现更高的导电率。

在第三维度

几乎所有的大型制造商都在计划制造三维芯片,这些芯片中的计算和存储单元可以在没有太多延迟的情况下相互作用。例如在处理器上叠加一层内存层和一层闪存层。最大的合同芯片制造商台积电即将推出16nm的三维集成芯片,这种芯片将用于高端的智能手机,例如iPhone 7,因为2016年苹果将会成为台积电的客户。制造商通过“硅通孔”(Through Silicon Via,简称TSV)技术实现三维集成,TSV通过在晶片上钻入10μm的孔填充有电导体,导体在彼此的顶部连接多个晶片组为一个三维芯片。

相对于单体三维芯片,TSV只能作为一种临时解决方案,单体三维芯片是一个单一的半导体芯片,各层由大约100nm厚的电线连接。单体三维芯片只有最下层在一个常规的晶片上制备,然后附加其他层的同时创建每个层的导线。单体三维芯片可以在低于400℃的温度下工作,这种各层紧密联系起来的三维芯片比TSV的三维芯片更小、更节能高效、数据传输的速度更快。

三维方法的固态硬盘和磁性载体

目前,固态盘所使用的闪存单元,类似于逻辑晶体管,但有一个额外的元件:浮栅。浮栅位于沟道和栅极之间,用于存储电子。最新的闪存单元小于20nm宽,缩小闪存单元与缩小处理器晶体管一样,具备优势的同时也将带来问题:闪存单元彼此接近时,存储的电荷将相互干扰。如果缩小闪存单元的尺寸,使它们只有10nm左右,那么固态硬盘控制器将无法正确地确定存储的值。因而,三星、东芝、闪迪和海力士等闪存制造商并不忙于缩小闪存单元的尺寸,而是不断地改变闪存单元的体系结构,其中的一种结构是在内存体堆叠多个闪存单元,闪存单元的结构被简化,在三星立体形式堆叠式的V-NAND闪存上,可以实现多达35 000次的写入或删除过程,而不是以往的3 000次。到2017年,三星准备提升V-NAND固态硬盘的存储密度约10倍,那么目前128GB的芯片就会变成1TB芯片。

三维方法也适用于磁性数据载体,由于磁性材料的粒子小于某个尺寸时将无法保持其磁性,所以现有的磁性数据载体也已经达到了它的极限。但新的金属合金可以是解决这个问题的一种方案,研究人员在佛罗里达国际大学已经建立了一个原型:1个叠加3个磁化层的硬盘,硬盘的每个层是相互隔离的,并具有不同的磁特性,写入头需要不同的磁场强度来磁化它们,而读出头可以读出所有3个层的磁场强度,它可以代表8个不同的值。