基于FPGA的频率测量仪设计

2014-08-07李鑫彪王笑怡

李鑫彪,王笑怡

(中国电子科技集团公司第四十七研究所,沈阳110032)

基于FPGA的频率测量仪设计

李鑫彪,王笑怡

(中国电子科技集团公司第四十七研究所,沈阳110032)

随着可编程器件的快速发展,FPGA已经广泛应用在各个领域。由于其性能的稳定性和设计的灵活性,因此本设计也采用了FPGA为主控单元,实现了用于测量信号频率的频率测量仪。在保证精度的基础上,用Verilog硬件描述语言制定了三个模块,以实现系统的整体功能,并对系统实现的整体功能进行了仿真验证。

现场可编程门阵列;频率测量仪;高精度;高速度

1 引 言

频率是各种信号源的一个重要物理量,是电子、通信等领域的一个重要研究对象,其大小和稳定性往往可以决定一个器件或者整个系统的性能。因此,用一种简单有效且精度较高的方法来测量一个信号的频率是检测一个信号频率能否达到要求的一项重要工作,对单独某个器件或者整个系统性能的稳定性起到了有力的保障作用。

选用FPGA作为频率测量仪的主控单元,是因为FPGA具有丰富的逻辑单元和IO口,系统可以方便地进行功能扩展,且其设计灵活方便,可以采用C/C++或Verilog HDL/VHDL进行程序或元器件的编写和修改。此外,采用FPGA设计可以使整个系统采用纯硬件结构,大大提高了系统的时实性。

2 设计原理

频率计的测量原理:给定一个闸门时间和一个已知频率的标准信号,在给定的闸门时间T内,分别测量标准脉冲信号的个数Nx和要被测量信号的脉冲数Nb,则:被测信号的频率为,其中fx为标准脉冲信号频率。在忽略标准脉冲信号频率fx的误差情况下,可能产生的误差为:δ=|f′b-fb|/fbe×100%,其中fbe为被测信号频率的真实值,δ=|ΔNx|/Nx≤1/Nx=1/T×fx。由上式可见,测量的精度与闸门时间和标准信号的频率成反比,闸门时间越长,标准信号的频率越高,则误差就越小。

标准信号的频率为100MHz时,闸门时间和系统测量精度之间的关系如下:

表1 闸门时间与精度的对应关系

可见,标频在100MHz,闸门时间为0.01s时,测量精度就可达到10-6。而标准信号的频率在FPGA中通过锁相环技术很容易达到100MHz,因此整个系统的测量精度很容易就可以达到很高。

3 FPGA模块及其整体设计

设计总体分为三个部分,分别为计数部分part1,寄存器部分buffer和数据选择部分chose,总体结构如图1所示。设计为双频率测量仪,可以同时测量两路信号频率,如果需要可以通过增加计数部分part1来增加测量信号的个数。

图1 系统的整体结构

3.2 计数部分part1

pin_bp为标准频率输入端,pin_door为闸门信号控制端,pin_cp为被测频率信号输入端,pin_out1[23..0]为在闸门时间内标准频率信号个数输出端,pin_out2[15..0]为在闸门时间内被测频率信号个数输出端。为保证频率测量仪的精度,取标准频率信号个数输出端为24位,被测频率信号个数输出端为16位,如果需要可以通过Verilog HDL/VHDL硬件描述语言方便的改变计数器位数,因此系统具有很高的灵活性,适用范围比较大(见图2)。

图2 计数模块

3.2 寄存器部分buffer

为保证数据读取与处理的正确性,采用Verilog HDL语言编写了一个寄存器,用于数据的正确读取与处理,其中reset为复位键,当其为低电平时,输出都为“0”(见图3)。

3.3 数据选择部分chose

为节省系统的IO口资源,使系统可以扩展更多功能,文章设计了一个数据选择器用于选择数据输出。在sel=0,rd=0的前提下,通过改变不同的add值选择不同的输出值。当sel、rd其中有一个不为“0”时,输出out为高阻“z”(见图4)。

图3 寄存器模块

图4 数据选择模块

4 仿真

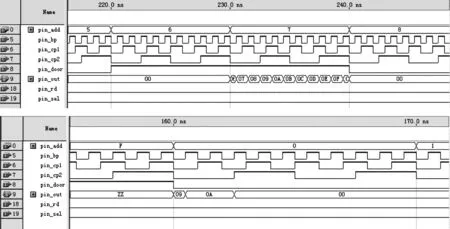

为保证测量精度,减小±1误差,闸门信号pin_ door如图5所示。但实际闸门信号设计为两步,第一步,当测频信号为高电平时,为中间闸门信号pin_ clk0的开始点,如图5中的中间闸门所示;第二步,当标准信号为高电平时,为最终闸门信号pin_clk1的开始点,最终闸门信号如图5中的最终闸门所示,其系统仿真如图6所示。

图5 预置闸门与最终闸门的关系

图6 预置闸门和实际闸门的验证

图6为验证实验图,标频信号pin_bp的频率比较低,pin_clk0和pin_clk1的时间差较长。在实际应用中,为保证测量精度,标频信号的频率往往较大,所以实际中的pin_clk0和pin_clk1的时间差很小。由图6可知仿真结果和我们预期的结果一样,所以证明了设计闸门时间控制的正确性。

图7为整个系统仿真的部分图,由仿真结果可以证明系统整体设计的正确性。

图7 系统整体功能的仿真

5 结束语

设计采用了Altera公司Cyclon II系列的FPGA芯片作为系统主控单元,通过Verilog HDL编写了三个模块组成整个硬件系统,其具有很高的灵活性,可以通过简单地修改程序,来修改三个模块,以实现不同场合的不同需要。其具有很高的精度,在保证系统标准频率不变的基础上,通过增加闸门时间来提高体统精度以保证不同场合对精度的不同要求。FPGA具有丰富的逻辑单元和IO口,因此,可以在本实验的基础上增加系统的功能和外接设备,从而可以更好的进行下一步的开发研究。

[1]王慧.基于FPGA的高速高精度频率测量系统的实现[J].传感世界,2006(1):27-29.

[2]张永安.基于CPLD的多功能等精度的数字频率计的设计[D].大连:大连理工大学,2004.

[3]周立功.SOPC嵌入式系统实验教程[M].北京:北京航空航天大学出版社,2006.

Design of Frequency Measurement Instrument Based on FPGA

LIXin-biao,WANG Xiao-yi

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

With the rapid development of the programmable devices,FPGA has been widely used in various fields.As its stability of the performance and flexibility of the design,FPGA is also used as the main control unit in the system to design the frequencymeasurement instrument formeasuring the signal frequency.In order to guarantee the accuracy,Verilog hardware description language is used to develop threemodules to achieve the overall function of the system,and the simulation is conducted to the functionsmentioned above.

FPGA;Frequencymeasurement instrument;High precision;High speed

10.3969/j.issn.1002-2279.2014.05.002

TN492

:A

:1002-2279(2014)05-0005-03

李鑫彪(1989-),男,黑龙江省七台河市人,硕士研究生,主研方向:嵌入式系统的设计及其应用。

2013-8-8