采用数字校准技术的单片12位D/A转换器

2014-08-07刘国权代雪峰

刘国权,代雪峰,唐 宁

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004)

采用数字校准技术的单片12位D/A转换器

刘国权1,代雪峰2,唐 宁1

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004)

阐述了一种分段式R-2R阶梯结构的D/A转换器电路。它利用数字码控制熔丝电阻网络,有效改善了工艺、温度以及电压等外界因素引起的R-2R阶梯结构匹配特性。依据CSMC的0.5μm,25V,BCD工艺模型进行设计,仿真结果表明12位D/A转换器的INL值为0.21LSB、DNL值为0.35LSB。

D/A转换器;数字校准;分段式R-2R阶梯

1 引 言

近些年,高速、高分辨率D/A转换器在现代先进电子设备与系统中起到了十分重要的作用。由于R-2R阶梯结构的低成本、面积利用率高的特点,被广泛应用于D/A转换器中。受限于传统电压工艺、温度以及电压等外界因素影响,R-2R阶梯结构的D/A转换器分辨率仅能做到10位,对于12位及以上采用该结构的D/A转换器产品,可以选择基于薄膜电阻的激光微调技术工艺[1]来实现;或者选择基于R-2R阶梯网络辅助子电阻网络进行补偿[2]。由于它们生产成本高、修调测试复杂等缺点,均不是最合适的方法。

提出了一种基于分段R-2R阶梯结构的单片D/A转换器,利用片上数字校准技术实现12位分辨率。首先,阐述了D/A转换器的系统结构与主要单元设计。然后给出了芯片的仿真结果。最后,作出了对这种新型DAC电路的总结。

2 D/A转换器电路设计

如图1所示,对D/A转换器中核心单元R-2R阶梯网络进行分段处理,高5位从阶梯网络中分离出来,其中高4位采用2进制加权并联方式,通过第7位与剩余的低7位R-2R阶梯网络实现权重匹配。低7位的匹配精度靠工艺水平保证,高5位电阻结构辅助熔丝电阻组成的子D/A网络,利用片上数字修调技术补偿匹配特性。

(1)R-2R阶梯网络开关设计

从图1可知,用于连接Vref或GND的开关阻值应该相等,对于此处电路设计采用图2的结构,M12、M13管作为连接Vref的开关,M14作为连接GND的开关,电阻R表示阶梯网络中电阻的阻值。利用差分差值放大器[3](DDA)组成的负反馈系统中,若开环增益足够大,那么:

图1 D/A转换器系统架构

由于流过M12、M13与M14的电流相等,那么M12、M13与M14的导通电阻相等。解决了开关连接Vref或GND的阻值匹配问题。

图2 R-2R阶梯网络中开关单元电路图

(2)熔丝电阻网络设计

如图3所示,修调电路的设计是基于熔丝电阻网络对高5位电阻匹配的补偿。电阻R的两端连接修调焊接点。依据数字修调码D<0:5>,近300mA的电流烧断熔丝,实现修调电阻的配置。

第12-10位的熔丝电阻网络如图3(a)所示。然而随着电阻R以2进制加权比例增长,修调电阻的值将过大,因此第8、9位的熔丝电阻采用分段网络结构,如图3(b)所示。

图3 电阻网络

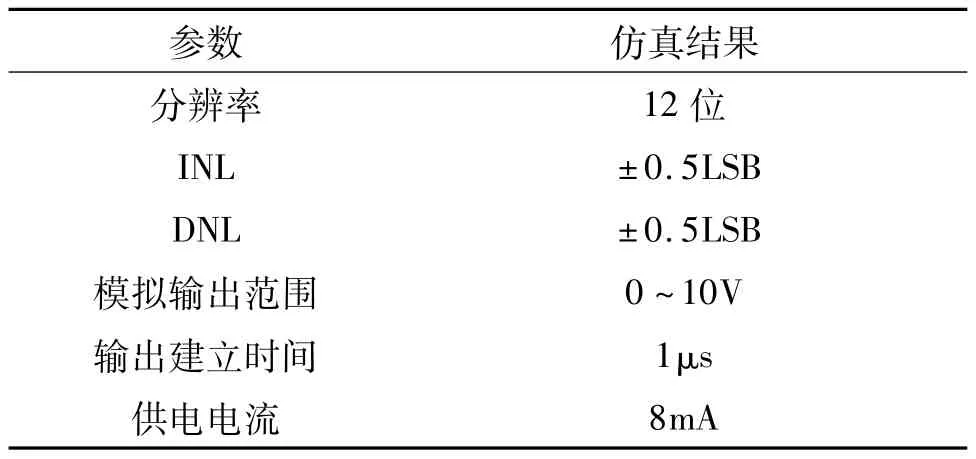

3 仿真结果

电路基于CSMC的0.5μm,25V,BCD工艺模型进行仿真验证,在电阻匹配容差为1%的条件下,进行200次蒙特卡洛分析。在最差情况下,应用校准算法进行了修调,如图4显示。修调后的INL值为0.21LSB,DNL值为0.35LSB。仿真结果证明在比较差的电阻匹配容差下,该电路修调技术可以补偿高分辨率D/A转换器性能的退化。

图4 校准后电路仿真结果

表1 主要性能指标仿真结果

4 结束语

提出了一种分段式R-2R结构D/A转换器,利用熔丝电阻修调网络对高5位2进制加权配置的电阻进行修调补偿,有效抑制了工艺、温度以及电压等外界因素对高分辨率D/A转换器中电阻匹配精度造成的影响。仿真结果显示完全满足12位分辨率的性能要求。

[1]J.Naylor.A complete high-speed,voltage output 16bit monolithic DAC[J].IEEE.J.Solid-State Circuits,1983,18(6):729-735.

[2]D S karadimas.A digitally calibrated R-2R ladder architecture for high performance DAC[J].ISCAS,2006:4778-4782.

[3]H Alzaher.A CMOS fully balanced differential difference amplifier and its applications[J].IEEE.Trans.Circuits Syst.Ⅱ,2001,48(6):614-620.

A Monolithic 12-bit D/A Convertor Digitally Calibrated

LIU Guo-quan1,DAIXue-feng2,TANG Ning1

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Physics Department,Collage of Sciences,Northeast University,110004,Shenyang,China;)

The paper presents a segmented R-2R ladder digital to analog convertor.Based on the design of fuse resistor network,it can digitally calibrate thematch tolerance performance of R-2R ladder structure,which caused by the factors of process,temperature and voltage.The paper simulates it with 0.5μm,25V,BCD processmodel in CSMC.The results show that the value of INL is0.24LSB and DNL is 0.35LSB.

Digital to analog convertor;Digitally calibration;Segmented R-2R ladder

10.3969/j.issn.1002-2279.2014.04.006

TN492

:A

:1002-2279(2014)04-0019-02

刘国权(1964-),男,辽宁临海人,高级工程师,主研方向:混合信号集成电路和功率集成电路的设计研究。

2013-12-03