嵌入式CPU总线接口单元设计

2014-08-07刘钟宇

刘钟宇

(中国电子科技集团公司第四十七研究所,沈阳110032)

嵌入式CPU总线接口单元设计

刘钟宇

(中国电子科技集团公司第四十七研究所,沈阳110032)

随着嵌入式技术的不断发展,对嵌入式CPU的要求越来越高,而总线接口单元是嵌入式CPU不可或缺的重要组成部分,它为嵌入式CPU和外设及存储器之间提供了接口控制,是决定系统性能的重要因素。深入了解总线接口单元的基本结构和设计方法对嵌入式的开发大有好处。

总线接口单元;处理器;片上系统;主机;从机

1 AHB总线的应用

AHB是基于集中多总线机制的,这使得AHB总线可以在比较高的时钟频率下运行。一个以AMBA AHB为系统总线架构的SoC,一般来说包含了高性能的系统总线与低功耗的外设总线。AHB系统总线负责连接嵌入式处理器与DMA控制器,片上存储器和其他接口外设。而外设总线则用来连接系统的周边组件,其协议相对AHB来讲较为简单,与AHB之间则通过桥相连。

2 AHB总线系统建设

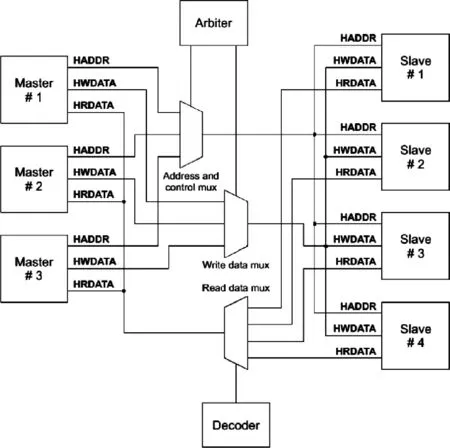

AHB系统由主机,从机,AHB总线接口逻辑三部分组成。整个AHB总线上的传输都是由主机所发出,由从机负责响应。

AHB之所以会需要仲裁器,是因为它支持多个主机,因此需要仲裁器来仲裁。而译码器则负责地址译码,从多个从机中选择要响应传输的从机。两个选择器负责总线路由,将总线上的信号在主机和从机中传送。图1介绍了AHB大概的总线互联网络。

图1 AHB总线互联网络

3 嵌入式微处理器中AHB总线接口单元的设计

3.1 AHB总线接口单元时序分析

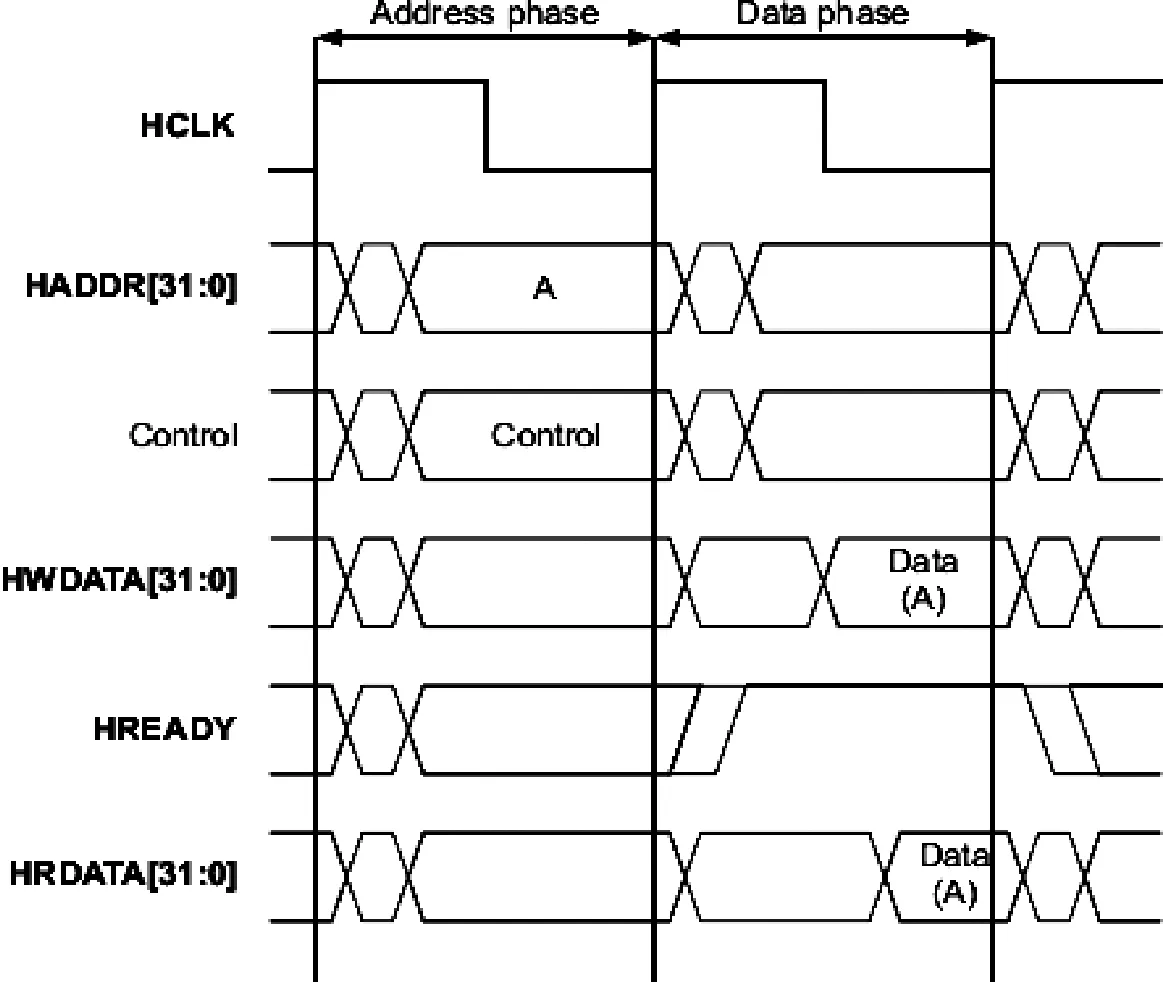

经过对AHB总线协议的详细研究,嵌入式微处理器中的总线接口单元时序如图2所示。

图2 BIU接口时序图

首先讨论不使用cache(高速缓冲存储器)的总线访问操作模式。有两种情况不会使用cache而直接通过总线操作:一是外部存储器的请求在一个不可cache的区域;二是cache没有使能。连续取指会做成不连续的读操作。下面讨论使用cache的总线访问操作模式。如果外部存储器请求到可cache区域且失效,处理器会完成一个行取值填充的传输。

下面是从机传输响应操作模式。主机发起传输后,从机的响应决定传输如何继续。从机传输响应类型如表1所示。

表1 从机响应类型

3.2 AHB总线接口单元的模块划分和设计

BIU主要划分为8个模块,包括地址信号生成模块、控制信号生成模块、数据信号生成模块、使能信号生成模块、地址控制信号仲裁模块、写数据信号仲裁模块、Split/retry逻辑模块、对内接口信号生成模块。其结构框图如图3所示。

地址信号生成模块:地址在时钟上升沿产生,包括三类地址,SRADDR1是第一个split(传输断开)响应的保持地址,SRADDR2是第二个split响应的保持地址,NextAddr是地址仲裁产生的核或cache地址。结构如图4所示。

控制信号生成模块:控制信号生成模块中按结构分成两类控制信号,一类包括HWRITE、HSIZE及HPROT信号,它们有着与地址信号生成逻辑相似的结构。包括HTRANS、HBURST、HBUSREQ信号,它们由状态机时序结构实现。

图3 BIU硬件结构框图

图4 BIU地址寄存器

(1)传输类型信号状态机

这个状态机用于生成传输类型信号HTRANS,包括:IDLE(空闲)、NSEQ(单个传输)和SEQ(连续传输)。

(2)传输个数信号状态机

这个状态机用于生成传输个数信号HBURST,包括:未定义长度(INCR)、单个(SINGLE)、4个(INCR4)和8个(INCR8)。

(3)请求信号状态机

这个状态机用于生成BIU的请求信号HBUSREQ。REQ、LAST和SINGLE状态都生成HBUSREQ信号,IDLE状态不生成HBUSREQ信号。

数据信号生成模块:BIU有两类数据,一类是读入数据,一类是写出数据。读入数据从外部存储器读入,通过BIU分别输出到DEXT、IEXT两个模块,信号是DBIURD、IBIURD。写出数据从内部写入,通过BIU输出到外部存储器,信号是HWDATA。结构如图5所示。

使能信号生成模块:使能信号状态机是标志当前总线工作状态的,总线传输时的状态是ACTIVE,空闲时的状态是IDLE。

图5 写出数据寄存器

地址控制信号仲裁模块:BIU对地址和控制信号通过仲裁模块进行选择输入。仲裁原则是先数据后指令,先核后cache。结构如图6所示。

图6 地址及控制信号仲裁器示意图

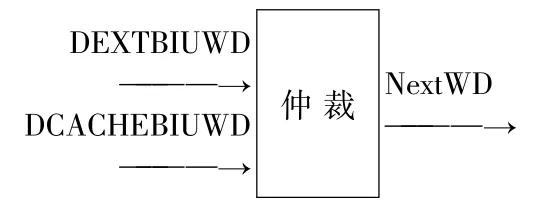

写数据仲裁模块:BIU的写数据由核与cache提供,通过写信号仲裁器选择输出NextWD。如图7所示。

图7 写数据信号仲裁器示意图

SPLIT/RETRY(传输断开和重试)逻辑模块:这部分逻辑用于产生SPLIT/RETRY状态后地址和控制信号状态。当传输可以继续后,上一次传输未成功的地址和控制信号要进行重发。

反馈信号生成模块:BIU的输出信号有一部分需要反馈给内部模块,包括DEXT、IEXT、DCACHE、 ICACHE等模块。该模块向其他内部模块产生应答、准备、出错等反馈信号。

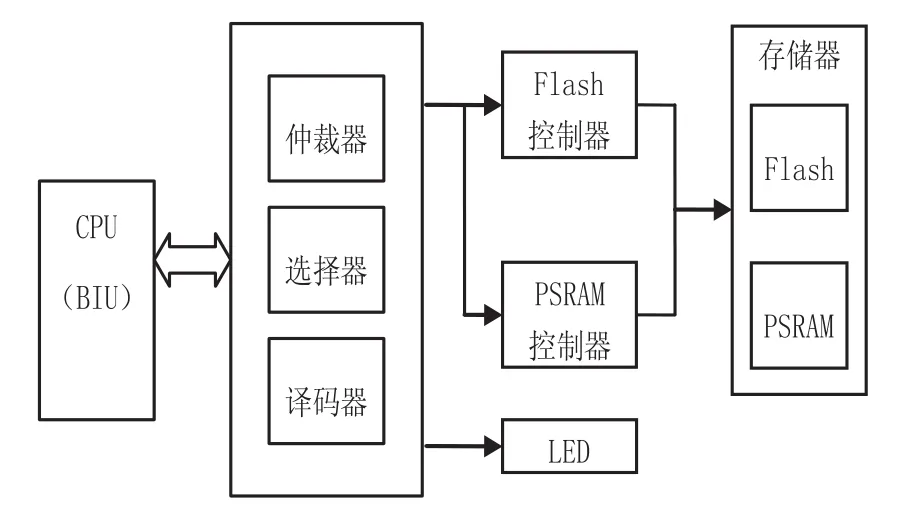

3.3 验证平台建立

对于功能验证,采用的验证平台为能够组成最小系统的嵌入式平台。连接CPU、仲裁器、译码器、选择器、LED、Flash存储器、Flash控制器、PSRAM存储器和PSRAM控制器等部件。验证过程是在复位之后进入工作状态,将Flash中的程序搬运到PSRAM中,然后执行PSRAM中的程序。图8为验证平台结构图。

图8 验证平台结构框图

4 总结

主要介绍了基本的AHB协议,由于AHB的复杂性,因此也探讨了一些AHB重要的规范和特性,并重点介绍了在嵌入式微处理器中AHB总线接口单元的设计。希望可以为嵌入式处理器的设计工程师带来一定的帮助。

[1]Steve Furber著.ARM SoC体系结构[M].田泽,于敦山,盛世敏,译.北京:北京航空航天大学出版社,2002.

[2]杜春雷.ARM体系结构与编程[M].北京:清华大学出版社,2003.

Design on BIU of Built-in CPU

LIU Zhong-yu

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

According to the development of built-in technology,the requirement for the built-in CPU is getting higher and higher.The BIU,as the important port,provides the interface between CPU and peripheral equipmentwhich controls the capability of the system.It is useful for development of BIU to deeply study its structure and design.

BIU;CPU;SoC;Master;Slave

10.3969/j.issn.1002-2279.2014.04.004

TN4

:B

:1002-2279(2014)04-0012-03

刘钟宇(1981-),男,辽宁沈阳人,学士学位,工程师,主研方向:集成电路设计及验证。

2014-01-17