频率可调的环形振荡器设计

2014-08-07赵盼盼

赵盼盼,韩 良

(哈尔滨工业大学(威海)微电子中心,威海264209)

频率可调的环形振荡器设计

赵盼盼,韩 良

(哈尔滨工业大学(威海)微电子中心,威海264209)

设计和仿真了一种环形振荡器,采用五级延迟单元输入输出相连接的方式产生振荡频率,延迟单元采用的是差分结构,可以有效避免噪声。同时对于延迟单元的尾电流源通过给予两种不同的基准电流,使得振荡器可以产生两种不同的振荡频率。在Smic 0.18μm工艺下进行仿真,得到振荡频率分别为400KHz和250KHz,同时使得这两种不同频率的低电平时间相等,使其可以很好的运用于PFM模式的升压DC-DC转换器中,性能满足设定要求。

环形振荡器;差分延迟单元;频率可调

1 引 言

电压模式PFM升压DC-DC转换器中,需要振荡器电路来实现其电路脉冲频率调制的功能。振荡器一般可以分为LC振荡器、晶体振荡器和环形振荡器,这三种结构各有优缺点[1]。其中LC振荡器一般可以产生较高的振荡频率,但是其结构比较复杂,需要大的电感和电容,因此占用的面积较大,而且不能由标准CMOS工艺实现。晶体振荡器精确度最高且不受温度和电源电压的影响,但是其成本太高,一般运用于对频率精确度要求很高的电路。环形振荡器结构比较简单,一般采用多个延迟单元输入输出相连,且可以用标准CMOS工艺实现,其芯片面积小,多用在中低频电路中,因此环形振荡器可以很好的运用于电压模式的PFM升压DC-DC转换器中。

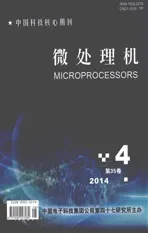

环形振荡器的基本原理是将延迟单元输入输出相接,在一定条件下就可以产生振荡频率,延迟单元一般主要分为单端输入输出和差分两种结构。对于单端结构,必须是奇数个(大于等于3)延迟单元输入输出相接才能产生振荡,单端环形振荡器结构如图1所示。

图1 单端环形振荡器结构

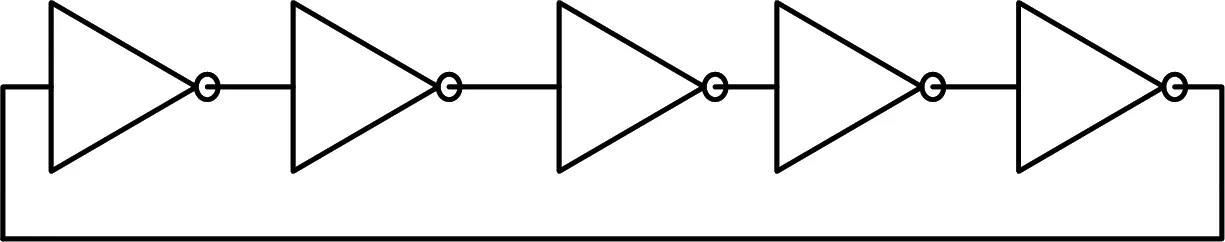

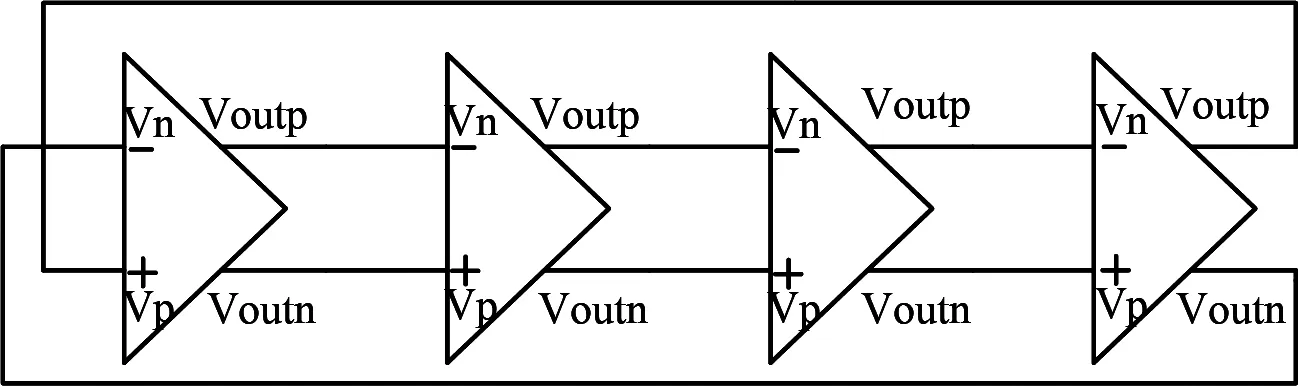

对于差分结构,可以分为偶数级和奇数级[2]。若采用偶数级(大于等于4)延迟单元,则其中一级采用正正相接的方式,剩下的级采用正负相接的方式,该结构原理图如图2所示。若采用奇数个(大于等于3)相连接,则每一级都要正负相接的方式,原理图如图3所示。

图2 差分偶数级环形振荡器结构

图3 差分奇数级环形振荡器结构

由于差分结构的延迟单元相对于单端来说,具有抗噪声能力强,频率稳定的特点,所以采用差分结构作为延迟单元组成环形振荡器。

2 延迟单元电路设计

采用五级差分结构的延迟单元构成环形振荡器,结构如图3所示。差分结构延迟单元大体可以分为电阻负载型、二极管负载型、电流源负载型、反馈信号控制型等多种结构[3],每种结构的延迟时间都与电容充放电的路径有关。采用一种附加了电流源的二极管连接的差分结构作为延迟单元[4],电路结构如图4所示。

图4 附加电流源的二极管连接的差分延迟单元

图4中M1、M2管是差分结构的输入差动对管,M0管是用NMOS管组成的尾电流源,就是通过控制尾电流源中的电流不同实现频率可调的。M3、M4管是二极管连接的负载结构,M5、M6管是与之对应的附加电流源结构,这样做的目的是为了提高电路的电压增益和抗干扰能力,输入晶体管的偏置电流一部分可以由PMOS电流源提供,那么流过二极管负载M3、M4管的电流就降低了。对于给定的栅源电压,相当于把晶体管的跨导降低了,所以电路的增益就增加了。

图4中差分延迟单元的延迟时间td与电路中的尾电流I、负载电容CL以及输出电压变化量ΔV的关系可以写成[5]:

由(1)可以看出延迟时间和尾电流源成反比,尾电流越大,延迟时间越小,振荡频率就越大,通过给尾电流源提供不同的电流,使得延迟时间不同,进而可以产生可调的振荡频率。

3 频率可调的实现

电压模式PFM升压DC-DC转换器的设计中,由于采用的是脉冲频率调制(PFM)的方法,因此就需要调节控制电路中振荡器的频率实现对输出电压的调节作用。调节振荡器频率则一般通过振荡器产生两种不同频率的方法来实现,这就要求振荡器在不同的控制信号下能产生两种频率的振荡。

在现有文献中,两种频率振荡器的设计都是通过环形振荡器在不同控制信号下充放电路径不同来实现的。如电子科技大学石刚同学在其硕士论文《一种PFM升压型DC/DC的设计研究》中所述的频率可调的环形振荡器如图5所示[6]。

图5中可以看出,环形振荡器采用的是单端输入输出结构的延迟单元。控制信号为COMP1,在其为低电平时,管子M3关闭,则电源电压只能通过管子M1对电容C2进行充电,此时得到一种振荡频率;当控制信号COMP1为高电平时,管子M3开启,则电源电压可以通过管子M1和管子M2、MP3一起对电容C2充电,则此时充电电流增大,延迟单元的延迟时间变小,频率上升。电路就是通过这种方式实现环形振荡器频率可调的。

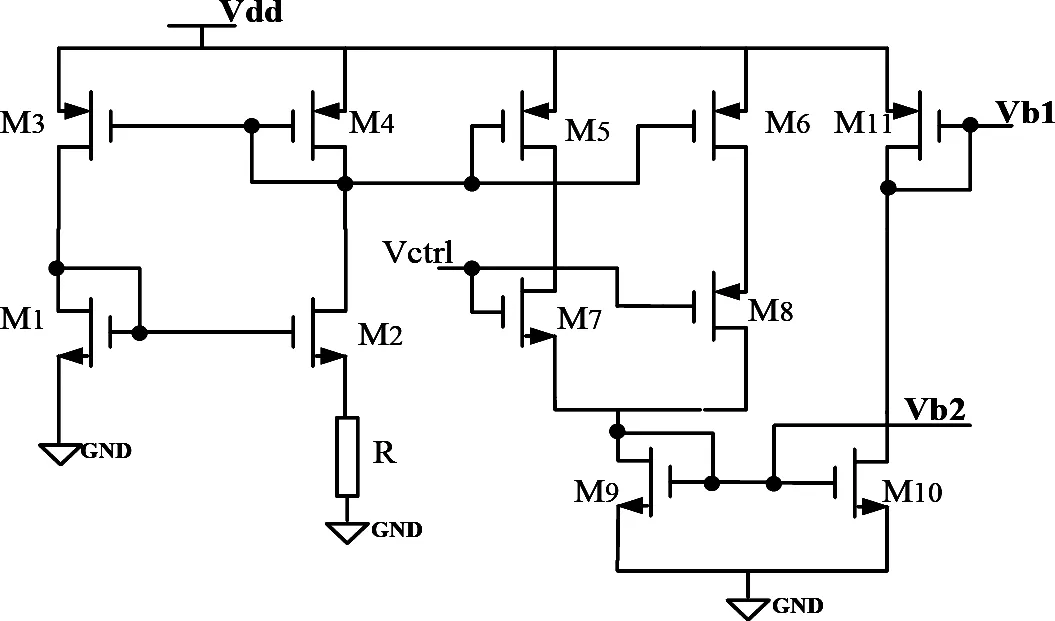

设计了一种区别于上述结构的频率可调的环形振荡器。延迟单元采用的是差分结构,通过在不同的控制信号下,给予差分延迟单元的尾电流源提供不同的电流来实现频率可调。差分延迟单元中尾电流源和PMOS负载电流源都需要合适的偏置电压来满足正常工作,设计的偏置电路是全文的核心,这个偏置电路既可以产生合适的偏置电压使差分延迟单元正常工作,又能在不同控制信号下提供不同的偏置电流实现频率可调功能,电路如图6所示。

图5 现有文献中采用的频率可调环形振荡器结构

图6 差分延迟单元偏置电路图

图6中管子M1、M2、M3、M4和电阻R组成与电源无关的电流偏置电路,其中M3、M4管的宽长比相同,M2管的宽长比是M1管宽长比的K倍,得到的电流是一个与电源电压无关的量[7]。

M5管和M6管具有不同的宽长比,进而可以复制M4中电流产生不同电流。M7、M8管是起到选择作用的器件,控制信号Vctrl来自于比较器输出,作用于管M7、M8的栅极。

当控制信号Vctrl为高电平时,管M7导通,管M8关闭,此时M5管的电流流向M9管产生偏置电压和电流。当控制信号Vctrl为低电平时,管M8导通,管M7关闭,此时M6管的电流流向M9管产生偏置电压和电流。差分延迟单元尾电流源复制M9管中电流,因为管子M5、M6的宽长比不同,所以电流就不同,进而使得延迟单元中尾电流源的电流不同,起到产生不同频率的作用。下面以电流变小为例讲述如何产生两种频率,当控制信号Vctrl为低电平时,M6管中电流会流到管子M9中,此电流相比于M5管中电流变小,差分延迟单元尾电流源电流也随之减小,同时流过管子M10的电流也变小,使得偏置电压Vb1增大,尾电流源减小和偏置电压的增大都会使得延迟时间上升,进而使得振荡频率降低,电路就可以产生两种不同的振荡频率。

相比于已有的频率可调的环形振荡器,设计的环形振荡器结构简单,频率方便可调,频率精确度高,可以很好的得到所需的振荡频率,运用于电压模式的PFM升压DC-DC转换器中。

4 整形电路设计

由于环形振荡器输出的电压不能达到全摆幅和较快的上升,在环形振荡器后面加入施密特触发器进行滤波和整形,施密特触发器的结构如下图7所示[8]。

图7 施密特触发器结构

设计的振荡器要用于电压模式PFM升压DC-DC转换器中,为了实现脉冲频率调制的作用,需要振荡器产生的两个频率的低电平时间相同,在周期不同的情况下进而占空比不同实现频率调节作用,合理设计施密特触发器的宽长比就能满足上述要求。

5 仿真结果及分析

为了更好的验证上文分析,将电路在Smic 0.18μm工艺下进行设计和仿真。环形振荡器不需要输入,但需要操作电压使其发生振荡。

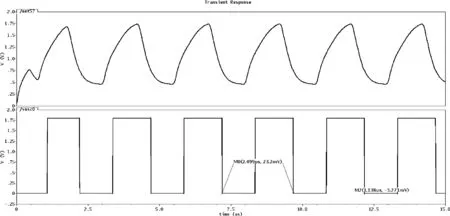

当控制信号Vctrl为高电平时,电路的仿真结果如图8所示,可以看出周期为2.5μs,即振荡频率为400KHz,低电平的时间是1.1μs,高电平的占空比为56%;当控制信号Vctrl为低电平时,电路的仿真结果如图9所示,周期为4.0μs,即振荡频率为250KHz,低电平的时间也是1.1μs,高电平占空比为72.5%。

图8 当控制信号Vctrl为高电平时电路的仿真结果

图9 当控制信号Vctrl为低电平时电路的仿真结果

6 结束语

设计了一款可以产生两种频率的环形振荡器,延迟单元采用差分结构,可以有效避免噪声和干扰。通过设计偏置电路给予控制信号,使得在不同控制信号下能给延迟单元尾电流源提供不同的电流,进而产生两种频率。该电路准确度高,易于控制,可以很好的用于PFM模式的DC-DC转换器中。

[1]胡乔.低压低功耗频率可调振荡器电路设计及仿真[D].成都:电子科技大学,2011.

[2]程梦璋,景为平.CMOS环型压控振荡器的设计[J].电子科技大学学报,2009,38(2):305-308.

[3]Roland E.Best Phase-Locked Loops Design,Simulation,and Applications(Fifth Edition)[M].北京:清华大学出版社,2007.

[4]拉扎维,陈贵灿,等译.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2002.

[5]Krishnakumar Sundarensan.A Process and Temperature Com-pensation in7-MHz CMOSClock Oscillator[J].IEEE JSSC,2006,l41(2):433-442.

[6]石刚.一种PFM升压型DC/DC的设计研究[D].成都:电子科技大学,2006.

[7]Mahdi Parvize,Amir Khodabakhsh,A Nabavi.Lowpower high-tuning range CMOS ring oscillator VCOs[J].IEEE International Conference,2008:40-44.

[8]EKEN Y A E,UYEMUR A.A 5.9GHz voltagecontrolled ring oscillator in 0.18μm CMOS[J].IEEE Jof Solid-State Circuits,2004,39(1):230-233.

Design on Frequency Adjustable Ring Oscillator

ZHAO Pan-pan,HAN Liang

(Microelectronics Center,Harbin Institute of Technology,Weihai264209,China)

A ring oscillator is designed and simulated in this paper.The five delay unit,using input/outputmethod to generate the oscillation frequency,uses a differential structure to effectively avoid noise.At the same time,two unused reference current ismade for the delay unit tail current source tomake the oscillator generate two different oscillation frequencies.By the process simulation of Smic 0.18μm,the oscillation frequencies of 400KHz and 250KHz are obtained respectively,meanwhile the equal low level time in different frequencies is achieved,which can be well used in PFM mode boost DC-DC converter,and the performance can meet the requirements.

Ring oscillator;Differential delay unit;Adjustable frequency

10.3969/j.issn.1002-2279.2014.04.003

TN4

:A

:1002-2279(2014)04-0008-04

赵盼盼(1989-),女,山东滨州人,工学硕士,主研方向:模拟集成电路设计。

2013-12-16