高速可编程网络创新实验设备设计与实现

2014-08-05刘中金金德鹏曾烈光

崔 波,刘中金,李 勇,苏 厉,金德鹏,曾烈光

(清华大学电子工程系,北京 1 00084)

高速可编程网络创新实验设备设计与实现

崔 波,刘中金,李 勇,苏 厉,金德鹏,曾烈光

(清华大学电子工程系,北京 1 00084)

面向下一代网络的新协议和体系架构研究是当前网络研究的重要组成部分,而基于实际设备的实验验证是证明研究结果正确性的主要途径。针对基于软件或传统网络设备的验证方式在有效性、灵活性等方面的不足,提出一种支持网络创新实验验证的高速网络硬件设备解决方案。该方案基于现场可编程门阵列设计,将控制平面与数据平面解耦合,同时采用高性能的网络与存储模块,满足网络创新实验对设备可编程、高性能、灵活管理控制等方面的需求。基于此方案设计并实现TNIP网络处理板卡。实验结果证明,该板卡支持高达16 Gb/s的网络通信,可以应用于复杂的网络创新实验。

网络设备;网络创新;实验平台;可编程硬件;现场可编程门阵列设计;虚拟化

1 概述

针对当前互联网诸如地址少、移动性差、服务质量无法保障、安全性差等问题,提出了众多演进和变革的技术,如MobileIP[1]、网络虚拟化[2]、内容命名网络(Named D ata Network, NDN)[3]、软件定义网络(Software Defined Network, SDN)网络[4]和OpenFlow[5-6]等。由于网络基本理论的缺乏,这些网络创新研究都需要通过实验的手段对其提出的体系结构、关键算法、协议及技术等进行验证[7]。传统的网络实验验证解决方案是软件仿真[8]或者在传统的网络设备(路由器、交换机、网络处理器等)上进行测试。软件仿真具有编程方便、配置灵活等优点,但是难以反映网络真正的行为特征,如流量负载、各种网络突发事件等。使用传统的网络硬件设备(交换机、路由器、网络处理器等)的实验验证保证了实验结果的有效性,然而由于传统网络硬件设备均基于IP结构,不能进行新型算法、协议或者新型网络架构的部署,这种功能固化的特征使得其不能胜任网络实验中对设备灵活性和扩展性的需求。

针对传统解决方案在网络性能、灵活性等方面的缺点,本文介绍一种新的网络创新实验设备解决方案。基于硬件的设计可以提供实际的网络环境,从而保证实验结果的真实性,而基于可编程的设计可以提供灵活的配置方式,方便各种不同网络算法或结构的部署。该方案采用现场可编程门阵列(File Programmable Gate Array, FPGA)为网络处理芯片,从而保证了设备良好的可编程可重用特性。在网络支持方面,方案中包含高速以太网接口以及相应的网络处理系统,以提供大规模的网络处理能力。解决方案中的控制平面可以有多样的选择,增强设备管理控制的灵活性。基于该解决方案,设计基于FPGA的高性能网络处理板卡:清华网络创新实验平台(Tsinghua Network Innovation Platform, TNIP)。该板卡搭载赛灵思Virtex FPGA,支持高达16 Gb/s的网络通信速率,ARM与PC双路控制增加了设备使用的灵活性。

2 网络创新实验设备解决方案

2.1 设计目标

软件仿真与传统硬件设备都不能很好地支持网络创新实验,这使得创新网络研究需要新的硬件设备。根据网络创新研究的性质以及其对网络测试环境的要求,该设备应该具有如下特性:

(1)设备需要有强大的网络处理性能。现实的互联网面临网络环境复杂、网络流量负载大、网络结构复杂等问题。硬件实验设备必须要能实现大流量的网络传输与处理,并有强大的组网能力来支持各种复杂网络结构的搭建,才可能为网络实验提供真实可靠的验证结果。

(2)要有可编程可重用功能。新型的网络研究设计了很多的网络算法、协议甚至网络体系结构,任一种都需要不同结构不同功能的网络设备来支撑,而功能单一、结构固定的传统网络设备显然不能满足所有的需求,最根本的解决办法是为设备提供可编程的功能,让研究人员定制自己需要的功能。

(3)设备要有足够的灵活性和可扩展性。随着技术的发展,网络早已不仅仅是电脑与服务器之间的通信了,网络设备有可能应用在智能手机、嵌入式电子系统、移动传感网络等各种领域,而网络创新实验的研究跟这些应用息息相关,也存在大量的不同环境下的网络实验需求。为此,用于网络实验的硬件设备也需要有足够的灵活性和可扩展性以适应不同情形下使用网络设备的需求。

2.2 解决方案的总体结构

本文提出一种基于可编程硬件的网络创新实验设备解决方案,该方案整体结构如图1所示。

图1 解决方案总体结构

方案中包含处理核心及其外围电路、网络模块、控制系统、存储系统、电源系统等5个部分。其中,处理核心器件为FPGA芯片,用于搭建网络设备的数据平面,实现数据处理与转发;外围电路保证FPGA的正常工作,提供必要的配置以及监测等功能;网络系统负责将接收到的网络数据进行初步的处理后送入FPGA进行进一步处理;控制芯片与控制平面共同组成该方案的控制系统;存储系统为方案提供了数据存储缓冲的空间。

选择FPGA作为设备的核心处理器件。FPGA的可配置逻辑块阵列包含大量的可配置逻辑,可以满足网络创新实验对设备可编程可重用的功能。尽管ASIC结构同样可以实现可编程的功能,但是ASIC芯片不可重复设计且设计周期长,相比之下,FPGA可重复配置、设计流程简单、开发周期短、成本低,更能胜任实验验证等任务。

网络模块负责网络数据的收发处理。该模块将从外部网络接收到的数据进行解码、校验等操作后发送到FPGA进行进一步处理。在相反方向,网络模块将设备要发送到网络的数据进行校验、编码等操作后通过网络接口发送到网络上。网络模块应能提供足够的数据吞吐量以满足那些对大数据速率的网络创新研究实验的需求。另外,一个好的网络实验设备需要支持构建尽量复杂的网络拓扑结构。

控制系统的设计采用了ForCES(Forwarding and Control Element Se paration)[9]框架的思想,将控制平面与数据平面相互分离,通过控制芯片进行桥接。这样的设计将数据平面的硬件设计与控制平面的软件设计解耦合,2个平面可以独立进行设计开发,提升了网络研究的效率。通过控制芯片的桥接,设备的控制平面可以在不同的平台上实现,只需要遵循既定的与数据平面的接口即可,大大增加了设备使用的灵活性以及可扩展性。例如,用PC实现控制平面可以将设备作为PC的扩展设备使用,例如可以用作PC网卡、硬件防火墙等;用ARM实现控制平面,则可以将设备用于嵌入式的环境中。

综上所述,通过采用可编程硬件的整体思路,对满足高性能网络处理与控制数据相分离所要求的系统结构相对应模块进行合理设计,该设备解决方案可以满足上文提到的可编程可重用、高性能、灵活控制等设计目标。因此,该设计方案能有效支持网络创新中的各种网络实验与测试的需求。

3 网络创新实验设备TNIP

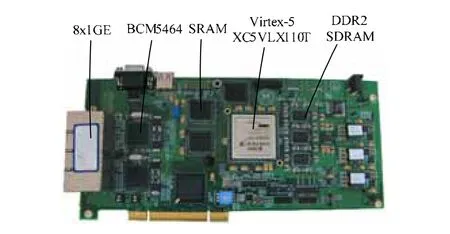

基于以上解决方案,设计了TNIP板卡,如图2所示。该板卡采用赛灵思Virtex系列FPGA作为处理核心,可以实现大规模的网络系统。网络模块提供了8个千兆以太网接口,可以实现16 Gb/s的高性能网络数据传输。在控制平面的实现上,板卡采用了ARM与PC双路控制的机制,用户可以灵活选择PC或ARM作为控制端。下文介绍TNIP板卡的详细实现方案。

图2 T NIP板卡

3.1 F PGA

作为系统的核心器件,FPGA用于部署系统的数据平面。FPGA中可编程逻辑资源的数量直接决定了该芯片可实现的系统的复杂程度。为保证该板卡能支持复杂系统的实现,FPGA需要有足够多的可编程逻辑资源。同时FPGA选型还考虑了其内部存储空间及相应功能模块(如MAC核、DSP单元等)的集成度。TNIP板卡的FPGA采用赛灵思公司Virtex-5系列FPGA芯片XC5VLX110T。该芯片包含丰富的逻辑资源与存储资源,可以满足较为复杂的网络系统设计,片上集成的DSP模块可以满足复杂的数据运算,而4个IEEE 802.3标准的以太网MAC硬核也可用于实现网络系统中MAC层的处理,提升网络系统的设计效率。

3.2 控制系统

控制系统由控制芯片与相应的控制平面共同组成。控制芯片作为桥接控制平面与数据平面的枢纽,定义了2个平面的通信接口。数据平面在FPGA上实现,用于处理网络数据的接收、包头处理、查找、转发等操作,而控制平面在相应的控制平台中实现,用于实现网络系统控制相关的所有功能。

TNIP板卡的控制芯片使用赛灵思公司的SPARTAN FPGA实现。板卡采用了ARM与PC双路平台控制的设计方案。用户可以利用PC开发功能完善的控制平面,也可以使用ARM芯片来开发嵌入式环境下的网络处理板卡。

3.3 网络模块

网络模块是网络设备中的基本单元。该模块包含了网络接口、物理层模块(PHY)、MAC层模块等。PHY实现网络物理层的编解码,MAC模块进行MAC帧的封包解包以及错误检测等操作。TNIP板卡提供了8个千兆以太网接口(RJ45)。物理层采用2个四路的PHY芯片实现。MAC模块可以使用FPGA芯片内部集成的MAC硬核实现,也可以使用FPGA通用逻辑编程实现,这样的设计允许用户自定义MAC功能,增强了板卡使用的灵活性。

4 板卡功能与性能评估

4.1 组网能力

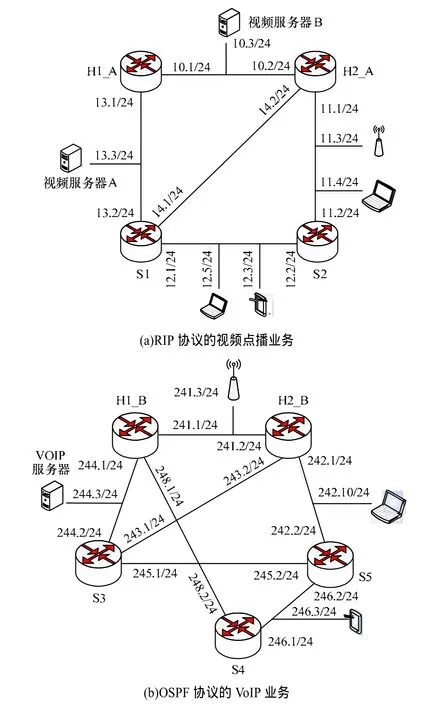

TNIP板卡组网实验在TUNIE实验平台[10]中实现。TUNIE是一个开放性的用于网络创新研究的网络实验环境。在此平台中,使用2个TNIP板卡配合软件虚拟化路由器搭建了2张网。每个网络拥有不同IP地址段。其中一张网络运行RIP协议,其上运行视频点播业务。另一张网运行OSPF协议,其上运行VOIP业务。2张网的拓扑结构如图3所示。H1_A/H1_B为在板卡1上实现的2个虚拟路由器,H2_A/H2_B则在板卡2上,S1~S5为软件虚拟路由器。

图3 网络拓扑示意图

实验结果显示,2张网络都可以正常生成各自的路由表,并正常转发数据,视频点播业务和VoIP业务都可以实时流畅运行,而且网络之间有良好的隔离性,一张网出现故障导致宕机,另一张网也可以正常运行。组网运行正常证明了TNIP板卡基本的网络功能正常。

4.2 虚拟路由器部署及性能

网络虚拟化是搭建网络实验平台的关键技术[2]。虚拟路由器作为虚拟网络载体需要着重研究。使用TNIP板卡可以很容易地实现高性能高可靠性的硬件虚拟化路由器。

使用该板卡设计实现了硬件虚拟化路由器,路由器结构如图4所示。图4中每条处理流水线都是一个虚拟路由器,独立维护各自的路由表项,独立进行路由操作。经过处理后的网络数据进入到输出仲裁模块进行仲裁并通过相关队列输出。

图4 硬件虚拟路由器结构

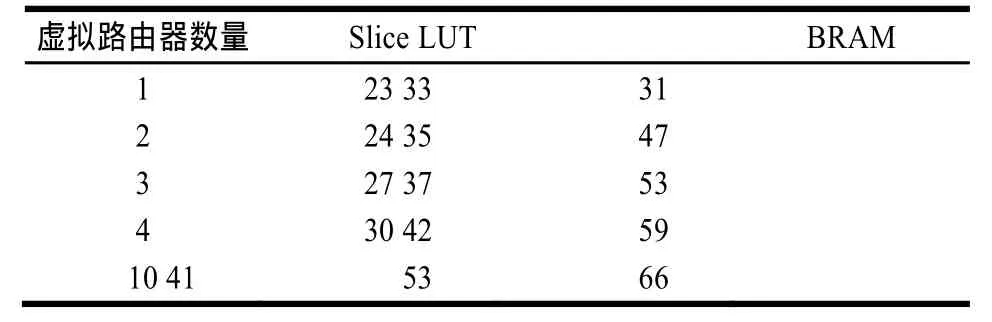

在实际部署中,针对不同数量的虚拟路由平面个数,进行了资源利用率统计,结果如表1所示。由于存在资源共用(输入输出FIFO、调度算法等)以及FPGA对不同复杂度系统的综合程度不同,资源利用率并非完全线性。可以看出,当虚拟10个路由平面时,资源利用率依然在70%以下,实际测试中这种情况下各路由平面均可以稳定工作。可见,TNIP板卡对网络创新实验的部署有很强的承载能力。

表1 不同数量虚拟路由器资源占用率比较 %

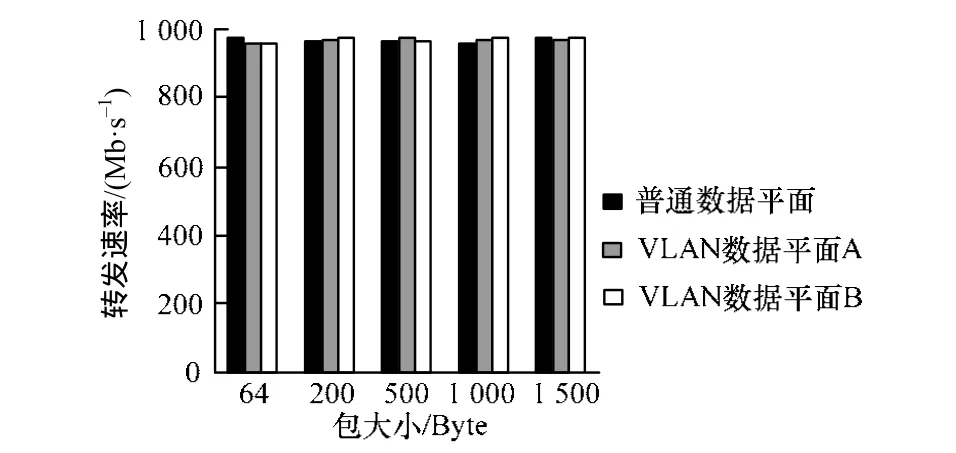

为了测试该硬件虚拟路由器的转发速率,在板卡上搭建了3个虚拟路由器,即3个数据平面,1个是以太网格式,另外2个是VLAN格式。由于板卡可以工作在线速,软件发包工具很难产生线速的数据包,为保证测量的准确性,实验中选择硬件发包工具[11]生成数据包。图 5为实际测得的转发速率。可以看出,每一个路由器都可以在趋近于1 G b/s的速率下正常处理网络数据包,该结果证明了板卡具有高速稳定的网络处理转发性能。

图5 转发速率测试结果

5 结束语

本文提出一种适应网络创新实验需求的硬件设备解决方案,采用FPGA与高性能的网络与存储模块实现了可编程重用、可灵活管理控制的网络处理板卡TNIP。实际组网与流量测试表明该板卡具有高速稳定的网络处理能力,并且可以承载复杂的网络功能,如虚拟路由器等的实现,也可以满足复杂网络环境的部署需求。16 Gb/s的网络通信带宽以及丰富的可编程逻辑资源使得该板卡可以胜任大部分网络创新实现的硬件验证需求。

随着网络容量的快速扩展以及业务流量的急速增加,核心网的端口速率已经达到了10 Gb/s甚至更高,今后的工作需要顺应这一趋势的发展,在该板卡的基础上设计更快更灵活的网络数据处理系统。

[1] Perkins C E. Mobile IP[J]. IEEE Communications Magazine, 1997, 35(5): 84-99.

[2] Carapinha J, Jiménez J. Network Virtualization: A View from the Bottom[C]//Proc. of the 1st ACM Workshop on Virtualized Infrastructure Systems and Arch itectures. Barcelo na, Spain: ACM Press, 2009: 73-80.

[3] Zhang Lixia, Estrin D. Na med Data Networking Project[R]. University of California, Technical Report: NDN- 0001, 2010. [4] Open Networking Foundation. Software-defined Networking: The New Norm for Networks[EB/OL]. (2012-04-13). https:// www.opennetworking.org/images/stories/downloads/sdn-resou rces/white-papers/wp-sdn-newnorm.pdf.

[5] McKeown N, Anderson T, Balakrishnan H, et al. OpenFlow: Enabling Innovation in Campus Networks[J]. ACM SIGCOMM Computer Communication Review, 2008, 38(2): 69-74.

[6] Curtis A R, Mogul J C. DevoFlow: Scaling Flow Management for High-performance Networks[J]. ACM SIGCOMM Computer Communication Review, 2011, 41(4): 254-265.

[7] Bavier A, Feamster N, Huang M, et al. In VI NI Veritas: Realistic and Co ntrolled Network Experimentation[C]//Proc. of Conference on Applications, Technologies, Architectures, and Protocols for Computer Communications. Ne w York, USA: ACM Press, 2006: 3-14.

[8] 张晓平. Cl ick软件路由器MPLS协议模块研究与实现[D].北京: 北京邮电大学, 2010.

[9] Yang L, Dantu R, Anderson T, et al. Forwarding and Control Element Separation(ForCES) Framework[S]. RFC 3746, 2004.

[10] Li Yong, Su Li. TUN IE: A Virtualized Platform for N etwork Experiment on Programmable Inf rastructure[C]//Proc. of the 19th IE EE Inter national Confere nce o n Net work Protocols. [S. l.]: IEEE Press, 2011: 125-126.

[11] Covington G A, Gibb G, Lock wood J W, et al. A Packet Generator on the N et FPG A Platform[C]//Proc. of the 17th IEEE Symposium on Field Programmable Custom Computing Machines. [S. l.]: IEEE Press, 2009: 235-238.

编辑 顾逸斐

Design and Implementation of Innovation Experiment Equipment for High Speed Programmable Network

CUI Bo, LIU Zhong-jin, LI Yong, SU Li, JIN De-peng, ZENG Lie-guang

(Department of Electronic Engineering, Tsinghua University, Beijing 100084, China)

New protocols and architectures for next ge neration Internet is an important part of current network research. Experimental verification based on physical equipment is the m ain approach to examine the feasibility and performance of the new technologies. With concerns of that software and traditional network facility based verification methods have some disadvantages. This paper proposes a device design solution to support net work innovation experiment. Based on Field Programmable Gate Array(FPGA), decoupling the data pla ne, control plane and using high performance network and storage modules, this paper can achieve the goals required by network innovation studies such as reprogrammability, high performance, flexibility of control and management, implements the design on TNIP network processing card. Experimental results show that T NIP can handle up to 1 6 Gb/s n etwork traffic an d ca n be used to de ploy network innovation experiments.

network equipment; network innovation; experiment platfo rm; programmable hardware; Field Programmable Gate Array (FPGA) design; virtualization

10.3969/j.issn.1000-3428.2014.05.065

国家“973”计划基金资助项目(2013CB3291005);国家自然科学基金资助项目(61171065, 61021001, 61133015);国家“863”计划基金资助项目(2013AA010601, 2013AA010605)。

崔 波(1990-),男,硕士研究生,主研方向:网络虚拟化技术;刘中金,博士研究生;李 勇,博士;苏 厉,讲师;金德鹏、曾烈光,教授。

2013-03-06

2013-05-03E-mail:thucuibo@163.com

1000-3428(2014)05-0313-04

A

TP393