基于FPGA的数字秒表设计与实现

2014-07-25王媛媛

王媛媛

(西安科技大学 电气与控制工程学院,陕西 西安 710054)

数字秒表是一种常用的计时工具,以其价格低廉、走时精确、使用方便、功能多而倍受广大用户的喜爱[1]。而基于FPGA的设计是当前数字系统设计领域中的重要方式之一[2]。同时,基于FPGA的片上系统与基于专用集成电路(ASIC)的片上系统相比,具有风险小、开发周期短、成本低、可擦写等优点[3]。其可以完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级时不需额外地改变PCB电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件工作,从而缩短了系统的开发周期,提高了实现的灵活性并降低了成本。本文基于FPGA开发平台,采用VHDL硬件描述语言设计了一款数字秒表,实现了以下功能:按键 1(K1),启动和停止秒表;按键 2(K2),复位(清零);蜂鸣器实现溢出报警;数码管实现计时显示。

1 基于FPGA的数字秒表设计

1.1 系统设计

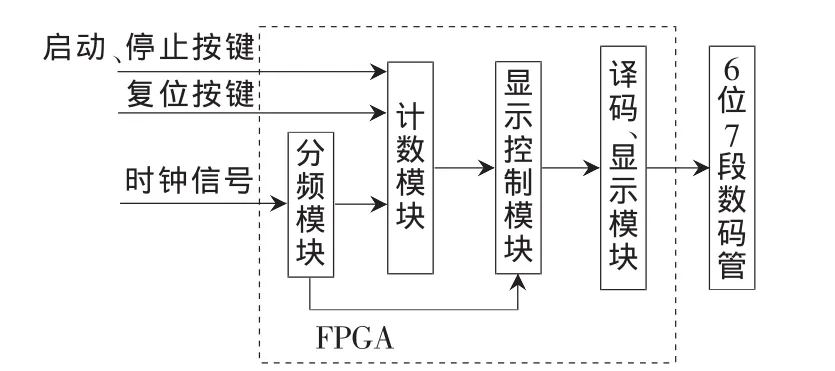

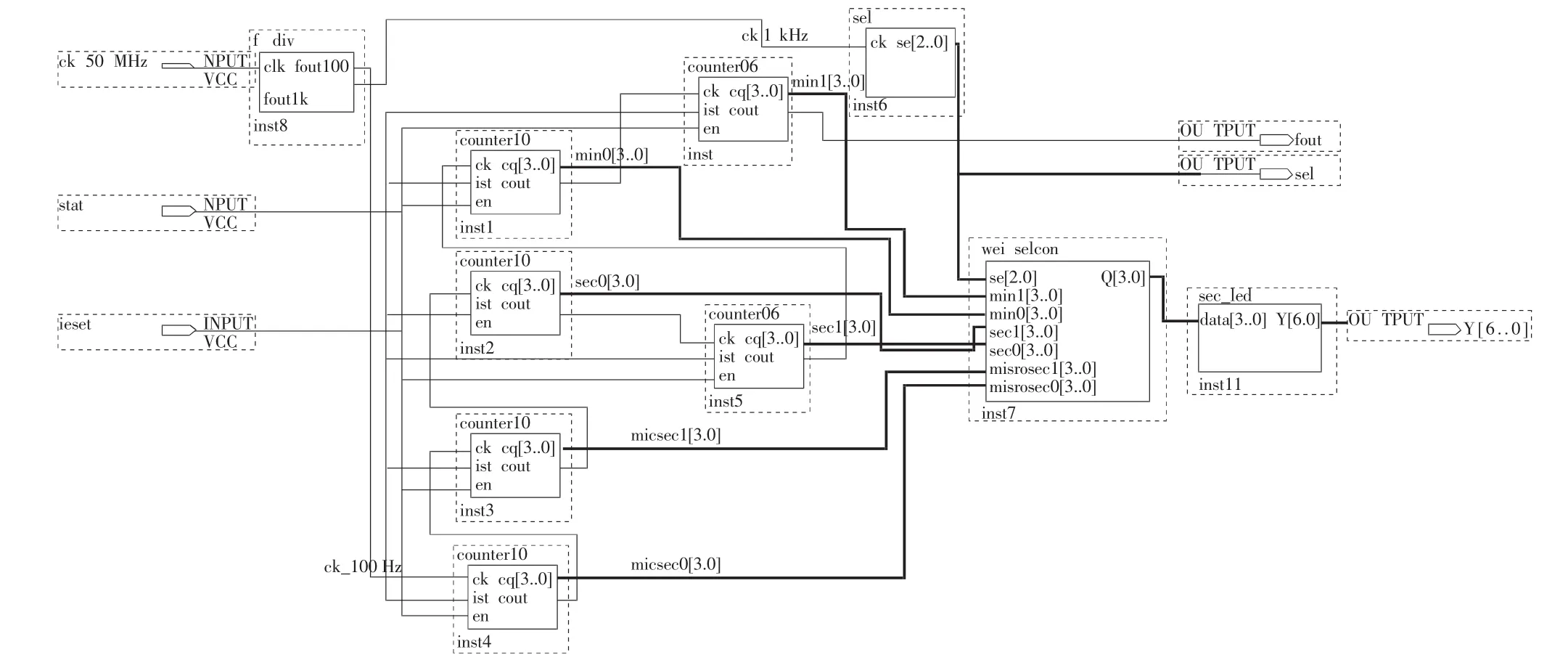

数字秒表常用于体育竞赛以及各种要求有较精确计时的场合,其主要指标参数和功能要求有:精度及分辨率,计时长度,启、停,复位等。根据设计的指标及功能要求,系统分为分频模块、计数模块、显示控制模块和译码、显示模块,其总体结构框图如图1所示。分频模块将FPGA开发板提供的50 MHz时钟信号进行分频,得到计数及数码管动态扫描显示所需的频率;计数模块由十进制和六进制计数器组成,用于实现秒表计时功能,其输出数据首先送给显示控制模块,该模块的主要功能是实现数码管的动态扫描显示控制,提供显示的位选控制信号和段选控制信号;最后是译码、显示输出,将计时时间进行译码并正确显示在数码管上。

图1 数字秒表总体结构框图

1.2 子模块功能设计与仿真

1.2.1 分频模块

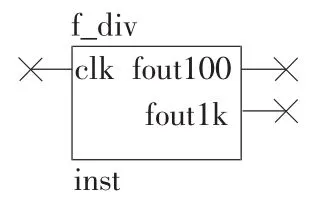

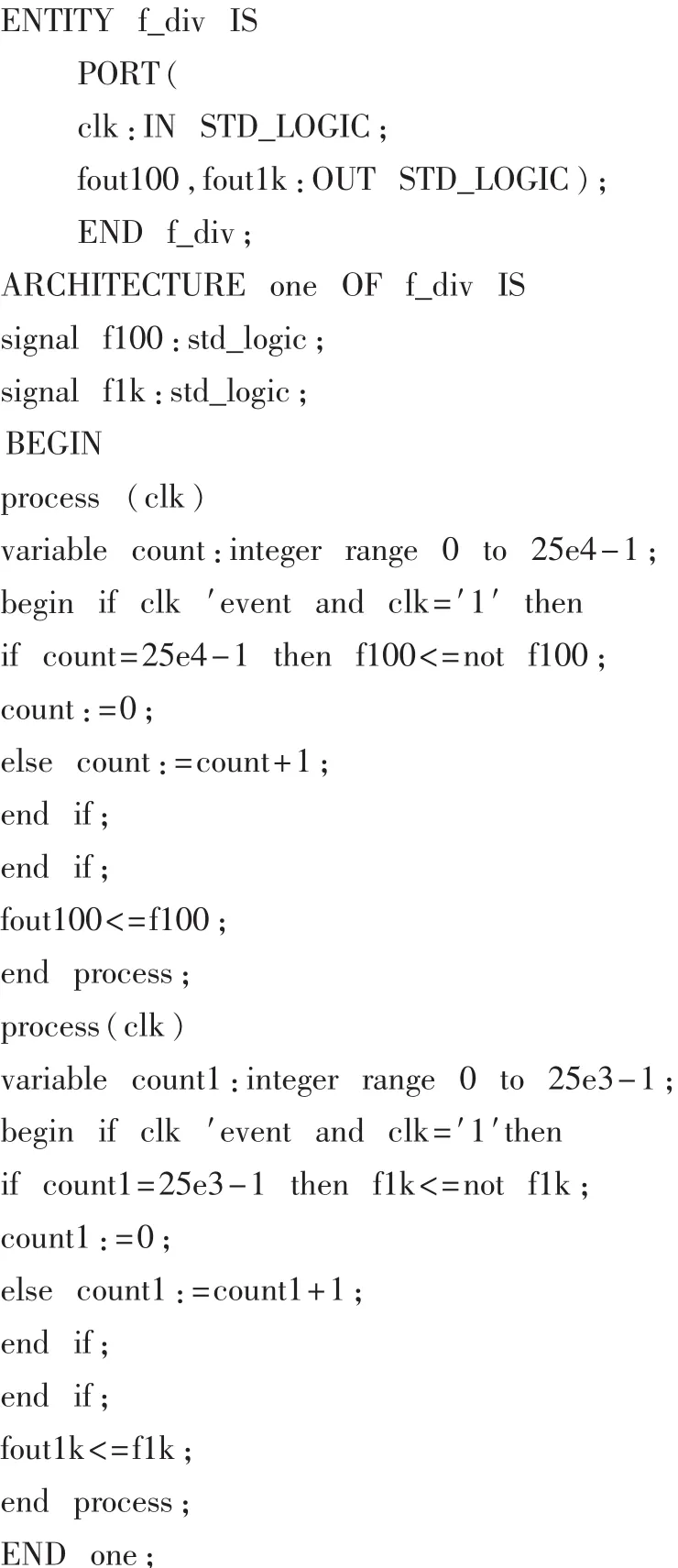

分频模块的主要作用是将较高频率的输入时钟信号进行分频,产生设计所需频率的时钟信号。模块框图如图2所示。FPGA开发板提供的时钟信号频率为50 MHz,而设计要求秒表精度为0.01 s,即需要计数时钟频率为100 Hz,同时显示扫描频率需 1 kHz,因此,通过分频模块对时钟信号进行分频,得到100 Hz和1 kHz的时钟信号,分别提供给计数模块和显示控制模块。该模块VHDL程序如下。

图2 分频模块框图

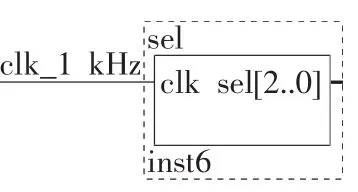

1.2.2 计数模块

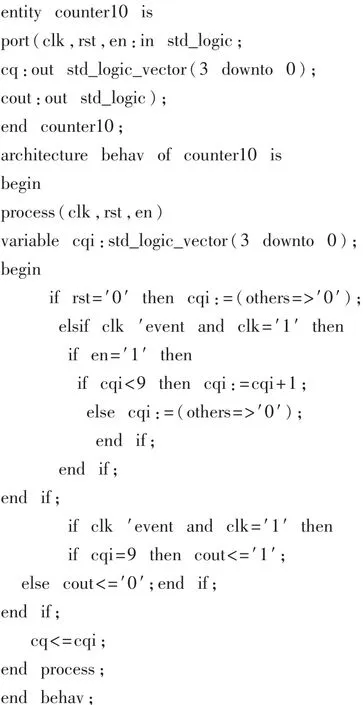

计数模块是秒表的核心模块,完成计时功能。本设计要求秒表分辨率为0.01 s,即10 ms,最大计时为:59 min,59.99 s。因此,该模块包括4个十进制计数器和两个六进制计数器。通过十进制和六进制计数器的级联组合,分别产生秒表的百分秒(0~99)、秒(0~59)和分(0~59)。十进制计数器为异步复位、同步使能计数器,其程序代码如下。

十进制计数器的仿真波形如图3所示。

图3 十进制计数器仿真波形

1.2.3 数码管动态扫描显示模块

通过分频模块和计数模块,已可以实现秒表的计时功能,接下来要将秒表的计时时间通过数码管显示出来。数码管显示方式有静态显示和动态扫描显示,本设计采用数码管动态扫描显示方式。

(1)数码管动态扫描显示原理分析

数码管显示的方式有静态显示方式和动态显示方式两种。静态显示的特点是每个数码管的段选必须接一个8位数据线来保持显示的字型码。当送入一次字型码后,显示字形可一直保持,直到送入新字形码为止。这种方法的优点是占用CPU时间少,显示便于监测和控制,缺点是硬件比较复杂、成本高。因此,在实际应用中,一般采用动态显示方式,即所有数码管的段选都并联在一起,由位选线控制哪一位数码管有效。所谓动态显示即轮流向各位数码管送出字型码和相应的位选,利用发光管的余辉和人眼视觉暂留作用使人感觉数码管是同时显示的。在编程时,需要输出段选和位选信号,位选信号选中其中一个数码管,然后输出段码,使该数码管显示所需的内容,延时一段时间后,再选中另一个数码管,再输出对应的段码,高速交替。在动态显示程序中,各个位的延时时间长短是非常重要的,如果延时时间长,则会出现闪烁现象;如果延时时间短,则会出现显示暗且有重影。

(2)显示控制部分

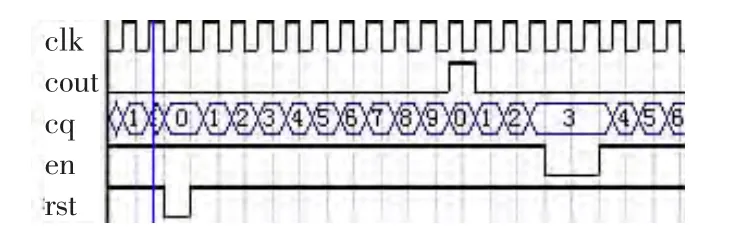

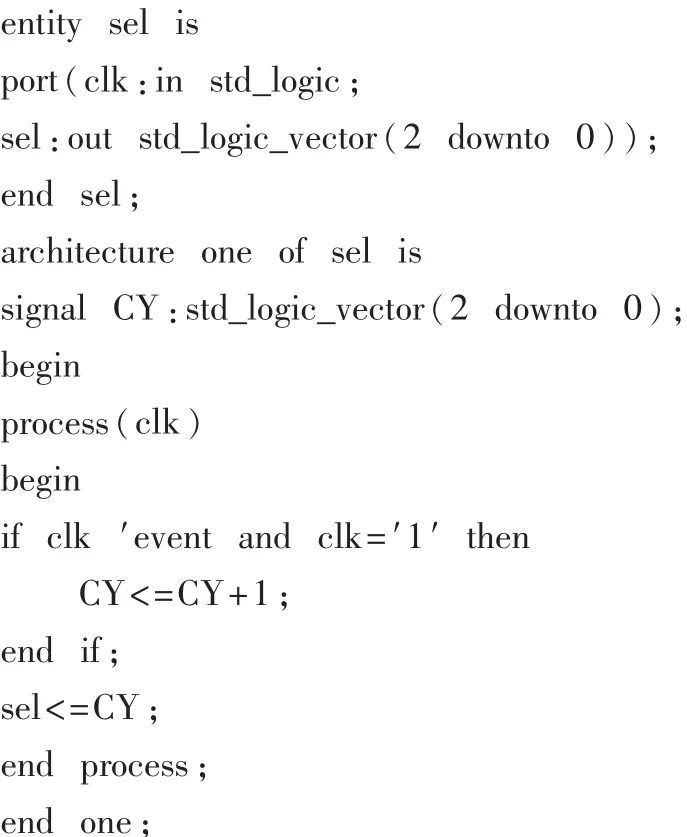

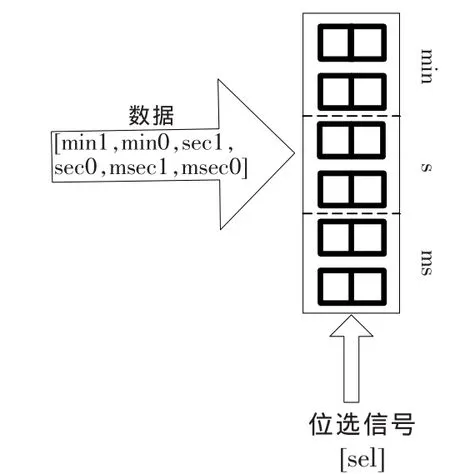

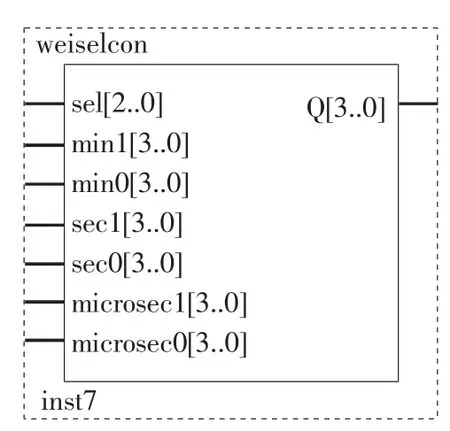

根据对数码管动态扫描显示原理的分析,结合设计的功能要求,选用开发板上6个共阴数码管扫描输出显示秒表的分、秒和百分秒,扫描频率一般只要超过人眼的视觉暂留频率24 Hz以上就可以点亮单个数码管而不闪烁,本设计采用1 kHz扫描频率。位选模块框图如图4所示。

位选程序代码如下所示。

图4 位选示意图

显示控制原理示意图如图5所示。位选信号在1 kHz时钟的作用下循环扫描每位数码管,使各数码管高速交替显示输出所送入的数据信号。在显示控制模块的作用下数码管分别显示对应内容:秒表的分、秒和毫秒,比如:显示 10:59:96,即 10分 59.96秒。显示控制模块框图如图6所示,显示控制程序如下所示。

图5 显示控制示意图

图6 显示控制模块框图

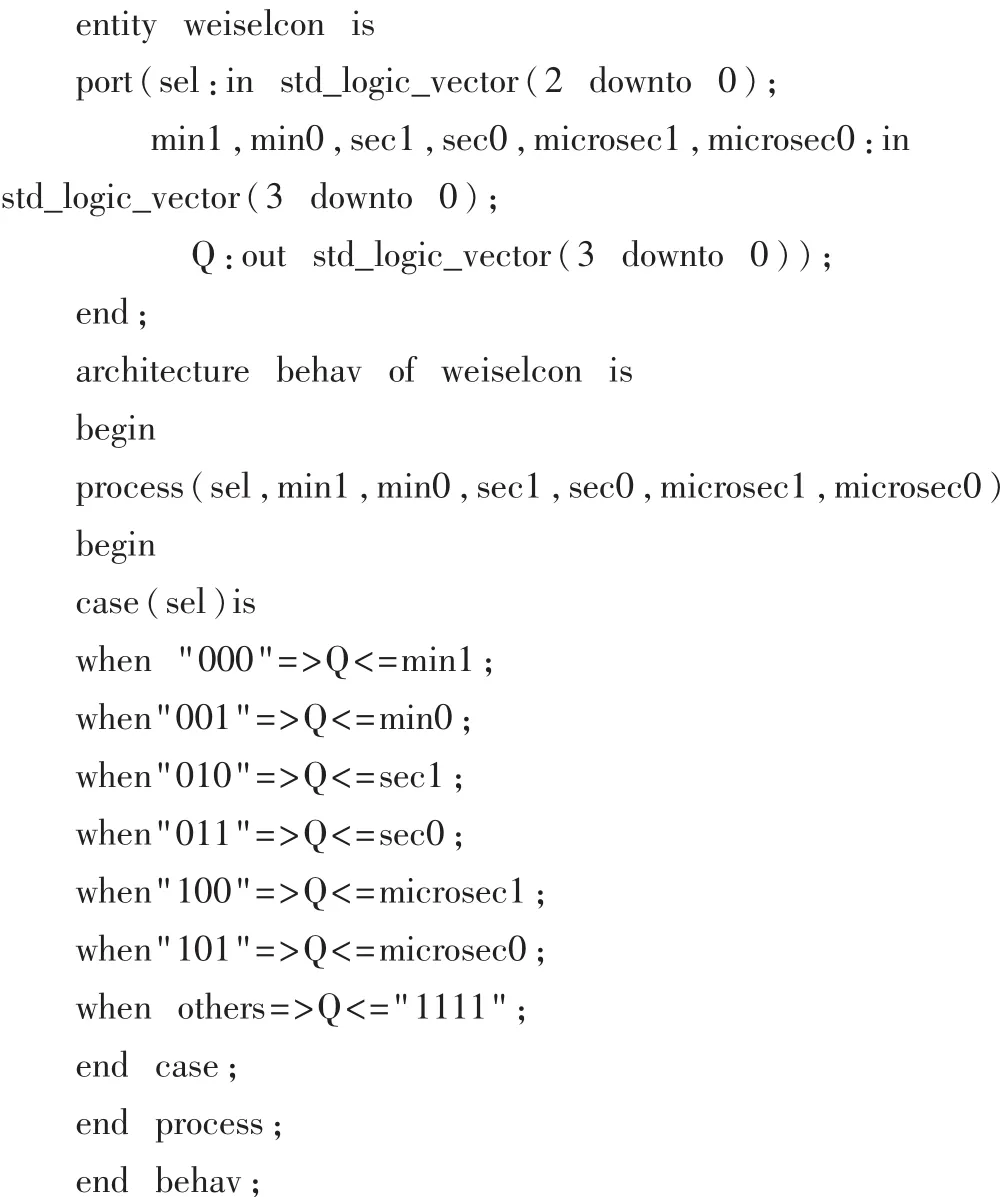

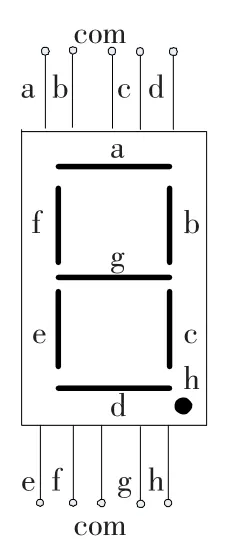

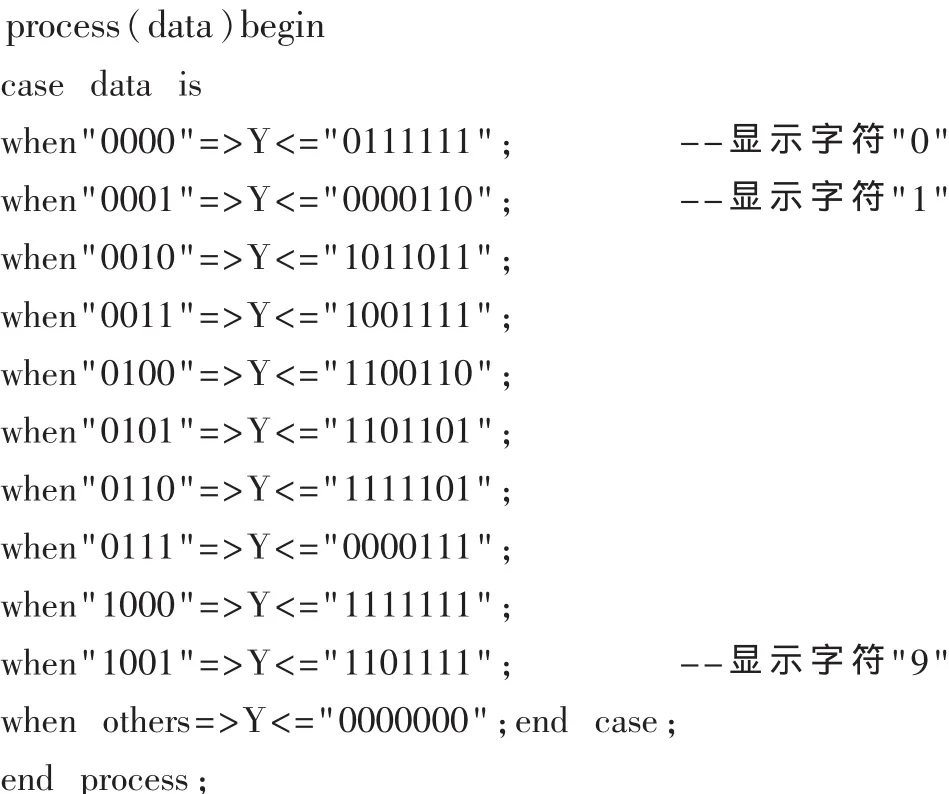

(3)译码、显示部分

LED数码管是由8个发光二极管封装而成的,每段为一个发光二极管,其字形结构如图7所示。选择点亮不同的段,可以显示出不同的字形,例如,当“a,b,c,d,g”字段被点亮时,显示字符“3”。

译码、显示部分的主要作用是将显示控制模块输出的二进制数据转换成0~9的十进制数据在数码管上显示。其VHDL代码如下所示。

图7 数码管示意图

2 基于FPGA的数字秒表的实现

在Quartus II开发平台上实现了数字秒表系统设计,其原理框图如图8所示。

图8 基于FPGA的数字秒表原理图

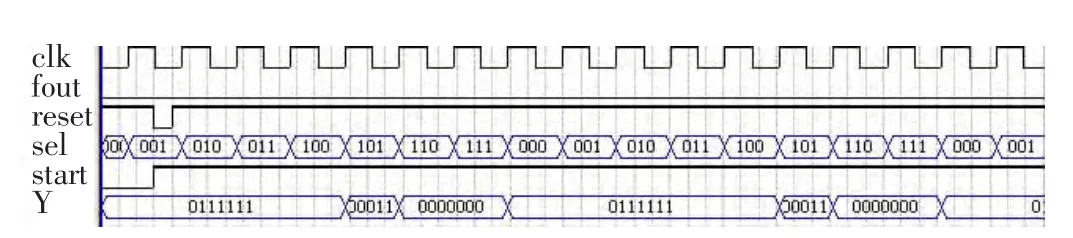

对系统整体进行了仿真分析,其仿真波形如图9所示。

图9 数字秒表系统仿真波形

3 编程下载与测试

本系统采用VHDL硬件描述语言完成了编程,并在Quartus II集成开发环境下进行了综合、编译和仿真分析,最后将设计引脚与硬件电路进行适配,将程序代码通过下载器下载至FPGA,本设计采用的是EP2C5Q208C8 FPGA。经过调试与验证,系统实现了如下功能:(1)具有复位功能,任何时刻都可以进行清零复位,复位时显示00:00:00;(2)具有启动、停止功能,可以实现秒表计时开启和计时中断停止,计时时长为59分59.99秒;(3)具有溢出报警功能。本系统实现了设计指标要求。

本设计基于FPGA开发平台,采用模块化设计思想、VHDL硬件描述语言和原理图输入方法,并经过实际电路测试,达到了预期的设计指标要求。与普通电子秒表系统相比,该系统具有外围电路少、精度高、集成度高、可靠性强等优点[4]。除此之外,也是基于FPGA的数字系统最为突出的特点,即当系统需要升级,或更新某项设计指标时,用户不需要重新设计或更换硬件电路,只需要通过软件修改程序即可,这样既可以节约成本,也可以大大缩短设计周期。

[1]樊金荣,谢智文.数字倒计时秒表的设计与实现[J].中南民族大学学报,2005,24(1):79-80.

[2]孙富明,李笑盈.基于多种 EDA工具的 FPGA设计[J].电子技术应用,2002(1):70-71.

[3]崔健,刘晋.基于 FPGA嵌入式系统的研究与应用[J].微型机与应用,2010(3):8-10.

[4]杨远成,赵创社,雷金利.基于FPGA的数字秒表的设计[J].现代电子技术,2008(12):52-53.