2.5 Gbps收发器中相位锁定检测电路的设计与仿真

2014-07-13邓军勇曾泽沧

邓军勇,蒋 林,曾泽沧

(西安邮电大学 电子工程学院,陕西 西安 710121)

2.5 Gbps收发器中相位锁定检测电路的设计与仿真

邓军勇,蒋 林,曾泽沧

(西安邮电大学 电子工程学院,陕西 西安 710121)

相位锁定检测电路是锁相环环路的关键电路,其性能的优劣直接影响了整个系统的工作。本文描述了相位锁定检测电路的工作原理,根据项目实际提出一种相位锁定检测方案,按照全定制设计流程采用SMIC0.18μm CMOS混合信号工艺完成了电路的设计、仿真。结果表明该电路在2.5 Gbps收发器电路中可以稳定可靠地工作。

相位锁定检测;CMOS电路;锁相环;收发器

锁相环是高速多通道串行收发系统中的关键电路,相位是否准确对齐对于系统性能有着重要影响[1-2]。电荷泵锁相环因其稳定性高,捕获范围大,便于集成等特点而别广泛应用于无线通信、频率综合器和时钟恢复电路中,为保证系统性能,锁相环通常都集成了相位锁定检测电路。

相位锁定检测电路通常包括模拟锁定检测和数字锁定检测两种方法,模拟检测方法采用经鉴频鉴相器PFD 输出的相位误差,产生脉冲信号对外部电容进行充电和放电,以指示当前相位是否锁定,精度往往较低;数字锁定检测方法具有可编程性且设计易于实现等优点,但相位误差参数受锁相环工作环境的影响较大,可能导致相位误差超出锁相环的最大锁定窗口[3-4]。

本文根据2.5 Gbps高速串行收发器的工作实际,设计了双环时钟数据恢复电路中锁相环路的相位检测电路,该电路模拟和数字方法,采用全定制的数字设计,电路工作精度高,可以达到时钟周期的1/218,能够满足G比特级数据收发的性能要求。电路采用SMIC 0.18μm CMOS工艺实现并基于spectre进行仿真,结果显示电路可以正常工作,符合预期要求。

1 锁定检测电路的结构

电荷泵结构的锁相环由鉴频鉴相器(PFD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)和分频电路组成。鉴频鉴相器比较输入参考时钟和反馈时钟的频率、相位误差,当反馈时钟落后于参考时钟(即正相差)时,产生UP信号;当反馈时钟超前于参考时钟时(即负相差)产生DOWN信号。电荷泵连接PFD和滤波器LPF,它实际是一个电压/电流转换器, 将PFD输出的误差电压电压转换成电流对低通滤波器进行充电、放电[5],通过低通滤波器转换为压控振荡器的控制电压的升高或降低,从而调整压控振荡器输出时钟相位累积的快慢,分频电路将VCO的输出时钟进行分频后送给PFD,与外部参考时钟进行比较,以输出频率、相位误差脉冲,锁定检测电路用于时钟的相位对齐检测,保证输入到时钟数据恢复环路的时钟的稳定[6-8]。

在本文设计电路所应用的环境中,锁相环输入的外部参考时钟频率为125 MHz,而分频器的分频比为20,那么VCO的输出时钟频率为2.5 GHz,但由PLL环路送给收发器中时钟数据恢复电路的是1.25 GHz的时钟,因此应将VCO的输出信号经过一个二分频及相位调整电路后才可以送给收发器供时钟数据恢复电路使用。

本文设计的相位锁定检测电路结构如图1所示。该电路主要包括两个可实现218分频的分频电路、18组两输入异或门构成的相位比较电路、一个18输入或非门构成锁定检测电路。输入参考时钟和反馈时钟分别进行18级分频,各级分频信号对应异或,其异或结果送给18输入的或非门。当各级分频时钟对应相同时,则异或门输出为0,此时经时序输出PLL_LOCKED信号为低电平表示锁定。

图1 相位锁定检测电路顶层原理图Fig. 1 Schematic view of phase-locking detection circuit

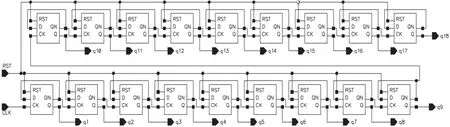

1)18级分频电路

由于将D触发器的输出端取反后连接到输入端,则输出信号即为时钟信号的2分频[9]。因此要对时钟进行218分频,则只需由将18个D触发器依次级联即可,电路如图2所示。每个D触发器采用主锁存器为负锁存器、从锁存器为正锁存器的主从结构,上升沿触发,带有异步复位,经过仔细地参数设计,触发器工作频率可以达到2.5 GHz以上,满足电路的工作速度要求。

2)相位比较电路

图2 18级分频电路图Fig. 2 Schematic view of 18-order clock division

相位比较电路由18组独立的两输入异或门构成,每个异或门用于比较锁相环的参考时钟的18个分频输出与由压控振荡器产生并经20分频后得到的时钟的18个分频结果,达到在时钟周期的1/18精度上的相位对齐。为了保证电路工作的时序要求,异或门的参数也经过仔细设计与调试,可以满足性能要求。异或门电路如图3所示。

3)锁定检测电路

锁定检测电路由一个18输入的准NMOS或非电路构成,在设计时可以增加一点考虑:这里的或非门是18输入,而且若时钟的第一级分频结果就不相同,则之后各级均不相同。因此可将第一级分频结果同时作为或非门的偏置信号,可以起到低功耗控制的作用。电路如图4所示。

2 电路仿真

为验证电路的功能性能是否符合要求,采用smic0.18um CMOS工艺完成电路设计后,在cadence的spectre上进行仿真,仿真结果如图5所示。从图中可以看出当输入时钟和反馈时钟同相以后,需要等待218个时钟周期后会输出有效锁定信号,整体闭环仿真中控制电压逐渐稳定,锁相环进入动态平衡。

图3 相位比较电路原理图Fig. 3 Schematic of phase comparation circuit

图4 锁定检测电路Fig. 4 Schematic of locked detection circuit

图5 相位锁定检测电路仿真结果Fig. 5 Simulation waveform of the phase detection circuit

3 结 论

文中描述了锁相环的关键电路,相位锁定检测电路的设计与仿真,通过分析常用的相位锁定检测方法,根据设计实际提出了一种全定制的数字实现方案,可以实现1/18时钟周期的精度检测,保证了电路的可靠稳定工作,采用SMIC 0.18μm CMOS 混合信号工艺完成了电路的设计、仿真,结果表明该电路在2.5 Gbps时钟数据恢复电路中可以稳定可靠地工作。

[1]Walker R,Agilent Laboratories Palo Alto, California. Clock and Data Recovery for Serial Digital Communication [J].ISSCC Short Course, February 2002.

[2]Savoj J,Razavi B.Design of Half-Rate Clock and Data Recovery Circuits for Optical Communication Systems[J].DAC 2001,June 18-22,2001,Las Vegas,Nevada, USA.

[3]Chang-Kyung Seong,Seung-Woo Lee.An 1.25-Gb/s Digitally-Controlled Dual-Loop Clock and Data Recovery Circuit with Enhanced Phase Resolution[J].International Symposium on Circuits and Systems, Kos, Greece,May 21-24,2006.

[4]Fuji Yang,Jay H.O’Neill, David Inglis,et al.A CMOS Low-Power Multiple 2.5-3.125Gb/s Serial Link Macrocell for High IO Bandwidth Network ICs[J].IEEE Journal of solid-state Circuit,VOL,2002,37(12).

[5]CHEN Ying-mei,WANG Zhi-gong,ZHAO Hai-bing,et al.A 10 Gbös CMOS clock and data recovery circuit[J].Research &Progress of SSE,2005,25(4):494-498.

[6]Horowitz M,Yang C K K,Sidiropoulos S.High-speed electrical signaling: overview and limitations[J].IEEE Micro,1998,18,(1):12-24.

[7]Lee K,Shin Y,Kim S,Jeong D K,Kim G,Kim B,Costa D V.1.04GBd low-EMI digital video interface system using small swing serial link technique [J].IEEE J. Solid-State Circuits,1998,33(5):816-823.

[8]Yang C K K,Ramin F R,Horowitz M A.A 0.5-mm CMOS 4.0-Gbit/s serial link transceiver with data recovery using over-sampling[J]. IEEE J. Solid-State Circuits,1998,33(5):713-722.

[9]任艳颖,王彬.IC设计基础[M]. 西安:西安电子科技大学出版社,2004.

Design and simulation of phase locking detection circuit in 2.5 Gbps transceiver

DENG Jun-yong, JIANG Lin, ZENG Ze-cang

(School of Electronic Engineering,Xi’an University of Posts & Telecommunications,Xi’an710121,China)

The phase locking detection circuit is a critical part of phase locked loop circuit, and its performance has great influence on the whole system. This paper analyzes the operating principle of phase locking detection circuit, proposes a digital scheme under full-custom design. The new scheme is design under SMIC 0.18μm CMOS mixed-signal process, and with simulation result, the circuit can word stably in the 2.5 Gbps transeceiver.

phase locking detection; CMOS; phase locked loop; transceiver

TN47

A

1674-6236(2014)07-0124-04

2013-10-17稿件编号201310099

国家自然科学基金项目(61272120,61201044); 陕西省教育厅专项科研计划项目(2010JK817)

作者简介:邓军勇(1981—),男,河北巨鹿人,硕士,讲师。研究方向:VLSI系统与计算机辅助设计。