基于FPGA的时间同步精度的设计与实现

2014-06-23宋鹏田乐

宋鹏,田乐

(西安工程大学电子信息学院,陕西西安710048)

基于FPGA的时间同步精度的设计与实现

宋鹏,田乐

(西安工程大学电子信息学院,陕西西安710048)

为了提高对时系统的精度,利用FPGA对传输对时信息进行解调.以北斗卫星的授时精度为基础,传输对时信息采用IRIG-B码,在FPGA对IRIG-B码解调中引入全数字Costas环,能够很好地提取出IRIG-B码的过零点信息,避免了过零点检测电路的零点漂移和脉冲抖动等问题.仿真结果表明,该算法减小了IRIG-B码的同步误差,提高了对时精度,达到电力系统中对时的精度要求.

IRIG-B;FPGA;时间同步;授时精度

0 引言

根据电力系统领域的授时要求,我国电网规定时间信号接收单元通过接收的时间信号,获得1pps (pulse per second)和包含北京时间时刻和日期信息的时间报文,其1pps的前沿与UTC(Universal Time Coordinated)秒的时刻偏差≤1μs,该1pps和时间报文作为主时钟的外部基准时间[1].

在终端时间统一设备,进行时间信息解码,需要将正弦波转换为矩形波,进行过零点检测.在波形变换过程中,过零点检测电路由于信道失真、信号不稳定、噪音等因素,在零点附近通常产生抖动、漂移,这样造成零点误判,输出时间精度降低[2-3].根据可编程逻辑器件(FPGA)的并行处理数据方式[4],本文采用FPGA对IRIG-B码解码,在解码中引入全数字Costas环,能够很好地提取IRIG-B码的过零点信息,输出1pps和时间报文,提高了时间同步精度.

1 IRIG-B码对时系统

北斗卫星导航系统(COMPASS)(北斗二代)是中国正在实施的自主发展、独立运行的全球卫星导航系统.由5颗静止轨道卫星和30颗非静止轨道卫星组成,空间卫星的任务是完成中心控制系统和用户收发机之间的双向无线电信号转发.北斗卫星系统中已成功发射16颗卫星,覆盖整个亚太地区.北斗全球卫星导航系统开放服务是在服务区免费提供定位、测速和授时服务,定位精度为10m,授时精度为50ns,测速精度为0.2m/s[5-6].

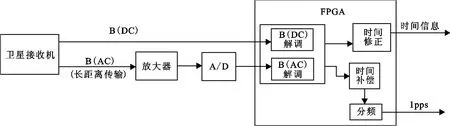

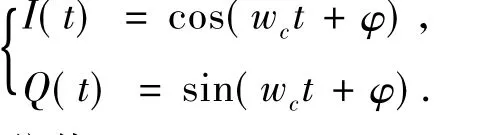

根据电力系统领域的发展和授时精度要求,本文时间统一终端设备采用北斗卫星导航系统接收机作为授时源,输出标准IRIG-B码.IRIG-B码是将串口对时的时间报文和数据脉冲对时的准时沿的优势结合在一起来传输时间信息,这种方式只需要传送一组信号,节约了主时钟系统资源[7].在终端系统设计中,采用FPGA对IRIG-B进行解码,其解调系统框图如图1所示.

图1 IRIG-B码解调系统图

图2 IRIG-B码示意图

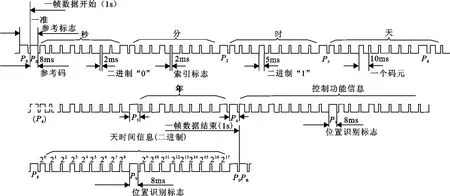

IRIG-B格式时间码是每秒一帧的时间码,其中B(DC)码的波形如图2所示.由图2可以看出,IRIG-B码为脉宽调制的时间码,它每秒一帧,每个脉冲称为码元.IRIG-B码是脉宽调制的时间格式.索引计数间隔的5ms和2ms分别代表了二进制“1”和“0”.参考码元(PR)的“准时”参考点为参考码元的前沿.

在实际应用中,根据IRIG-B码传输距离的不同,IRIG-B码有非幅度调制DC码(直流码)和幅度调制AC码(交流码)两种码型.非调制IRIG-B码是一种标准的TTL电平信号,适用于传输距离不远的场合,可达到ns级精度.对于长距离传输,正弦调制IRIG-B码对时只能达到ms级的对时精度[8-10].为了达到电力系统的对时的精度要求,采用FPGA进行IRIG-B(AC)码解码,其环路采用Costas环法进行零点追踪,对时精度可达到μs级.

2 提高接口终端B码的精度

直流B码,可使用电缆进行近距离的传输,其时间精度较高,在传输距离达到200m时,依然可以保证较高精度的信号传输质量.而IRIG-B(AC)用于远距离传输,其传输距离可以达到500m,因而其应用范围更广泛.由于经过了调制与解调的处理过程,因而B(AC)码信号的时间精度就会有所降低.

2.1 IRIG-B码精度的提高

IRIG-B(DC)传输采用RS-422标准接口,对输入的直流码进行电平转换后,得到TTL电平的B码信号.采用FPGA进行IRIG-B(DC)解码,在每一个IRIG-B码元的上升沿到来时开始计数,下降沿到来时停止计数,然后读出计数值,分别判断出是2ms或5ms或8ms,据此来判断码元的值,同时做6个状态机将秒、分、时、天、月、年区分出来,根据每次的码元及状态的判断,确认属于哪种状态并转移到这种状态,直至这一帧数据的完成.在一帧数据完成后输出数据,转换成串口数据输出.同时在连续两个8ms处解出1pps.采用FPGA进行IRIG-B(DC)解码,采取以下几种措施提高IRIG-B(DC)的对时精度:

(1)增加外部时钟频率外部时钟频率增加1倍,精度也会相应的增加1倍.这种方法是最简单直接的办法,但这种方法并不是任何时候都可以应用的.此法虽然能提高IRIG-B(DC)的解码精度,但同时增加了整个系统的功耗,并且由于板子运行速率的原因也是不能随意增加外部的时钟频率.

(2)采用脉宽判容错技术通过软件或硬件将1,2,3ms脉冲判别为2ms脉冲,4,5,6ms脉冲判别为5ms脉冲,7,8,9ms脉冲判别为8ms脉冲,做到脉宽判别容错.

(3)严格同步、失步判据在解码时,当连续3ms数据正确时允许同步,同时当连续3ms数据错误时判为失步,以便在最大程度上克服误码.

(4)减小1pps脉宽在设计中选择1pps信号来同步编码过程中的各个信号,1pps脉冲的上升沿来了之后,清零芯片内设计的各个计数器,使之开始记数.但由于1pps脉冲的脉宽较大,如果直接用它做清零信号,会带来较大的误差,因此需要把它的脉宽调整,使用调整后的脉冲,可以提高编码的精度.

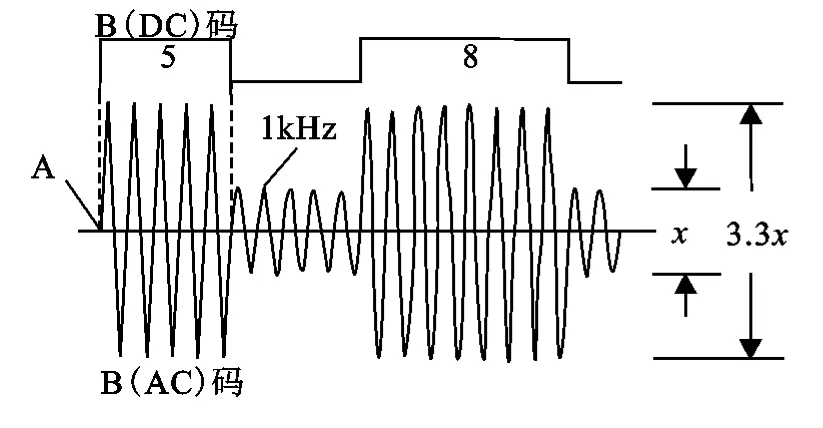

为了便于传递标准时间格式码,可用其对标准正弦波载频进行幅度调制,标准正弦信号必须与产生直流B码的信号共源,以保持两者之间的时间关系不变.标准正弦波载频的频率与码元速率严格相关,一般为码元速率的10倍.B码的标准正弦波载频频率为1kHz.同时,其正交过零点(图中A点)与所调制格式码元的前沿相符合,标准的调制比为10∶3,IRIG-B(AC)码调制示意图如图3所示.

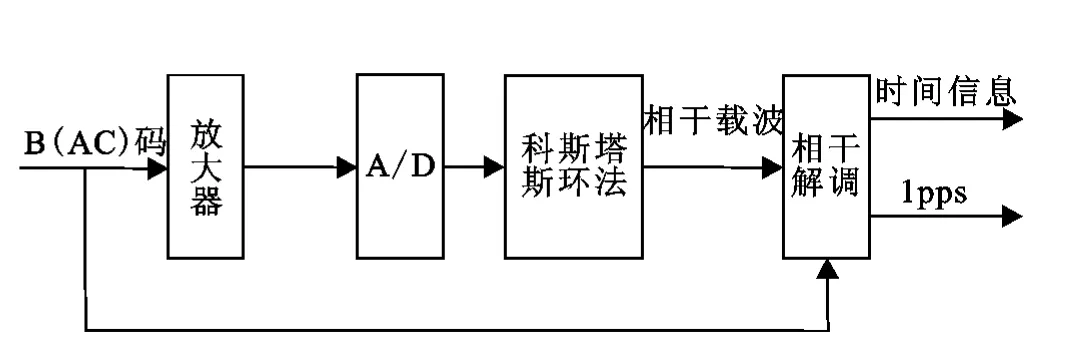

由于信道带来的噪声和失真,IRIG-B(AC)码在经过零检测电路形成的时间基准脉冲会有抖动和零点漂移,会把噪声传递到输出端,导致输出时间信号的抖动[2].对B(AC)码的解调中引入了全数字锁相环,该环路通过对输入的B(AC)码进行跟踪,从而得到其同频同相的载波,这样也就精确地得到了B(AC)码携带的过零点信息.这一方法完全克服了以往解调方式中采用过零点检测电路所存在的缺点.IRIG-B (AC)码解调原理图如图4所示.

图3 IRIG-B(AC)码调制示意图

图4 IRIG-B(AC)码解调原理图

解调IRIG-B(AC)信号时,必须恢复出同步载波信号.目前用于同步载波恢复的方法通常有两类,一类是在发送信号的同时,在适当的频率上还发送导频信号,实际中这种方法很少采用.另一类是直接从接收到的信号中提取,可以用平方变换法和COSTAS环法等.由于在获得相同的工作性能时,COSTAS环法的工作频率是平方变换法工作频率的1/2.因此,COSTAS环法在实际中更为实用[11-14].本文采用全数字Costas环法恢复B(AC)码的载波,用作IRIG-B(AC)码的同步时钟.Costas环的构成原理图如图5所示.

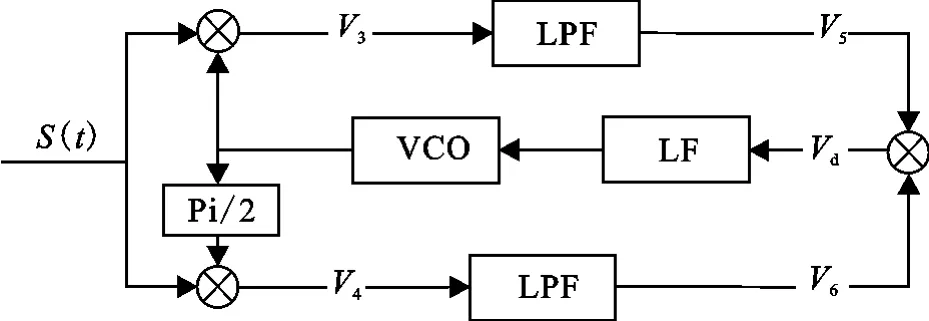

Costas环中的压控振荡器(VCO)输出两路互为正交的载波信号,接收到的输入信号s(t)分别与同相和正交的载波信号进入两个鉴相器中进行鉴相,通过低通滤波器(LPF)滤波后输出不含倍频项的基带信号,再相乘得到误差信号,送入到环路滤波器(LF)后输出与相位差相关的控制电压来控制本地载波源的输出[6].

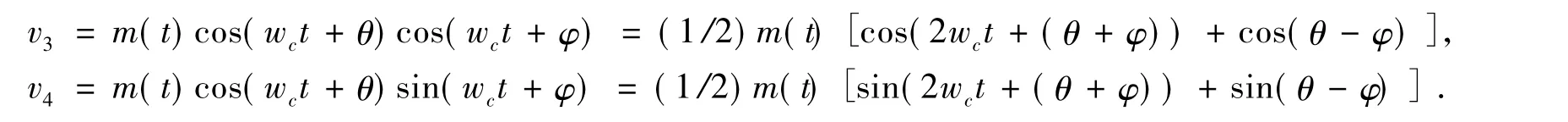

假设输入信号为s(t)=m(t)cos(wct+θ).其中m(t)为调制信号;wc为输入信号角频率;θ为输入信号初始相位.

本地VCO输出的两路载波信号为

图5 全数字Costas环原理图

其中φ为VCO输出载波频率信号的相位值.

输入信号和本地载波的两路正交信号相乘倍频后得到如下所示的两路信号:

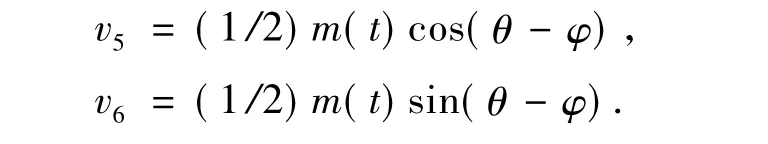

经过低通滤波器除掉倍频项后,得到鉴相器输入式:

两路信号经过鉴相相乘后得到加在环路滤波器上的误差控制信号:

当θ-φ总是小于1弧度的时候,sin(θ-φ)≈(θ-φ),误差信号就是和相位差相关的一个信号,最终使稳态相位误差减少到很小的数值,而没有剩余频差.环路锁定时,有v5≈(1/2)m(t).最终,VCO输出的载波信号就是系统所需要的载波信号.c1,c2分为Costas环路滤波器上下两个支路的增益因子,相关值的计算公式为

其中ξ为环路阻尼系数(工程上一般取0.707);wn为环路阻尼振荡频率,且wn=8ξBL/(4ξ2+1);BL为环路等效噪音宽带;T为环路更新时间;Kd为环路总增益.

2.2 数据仿真

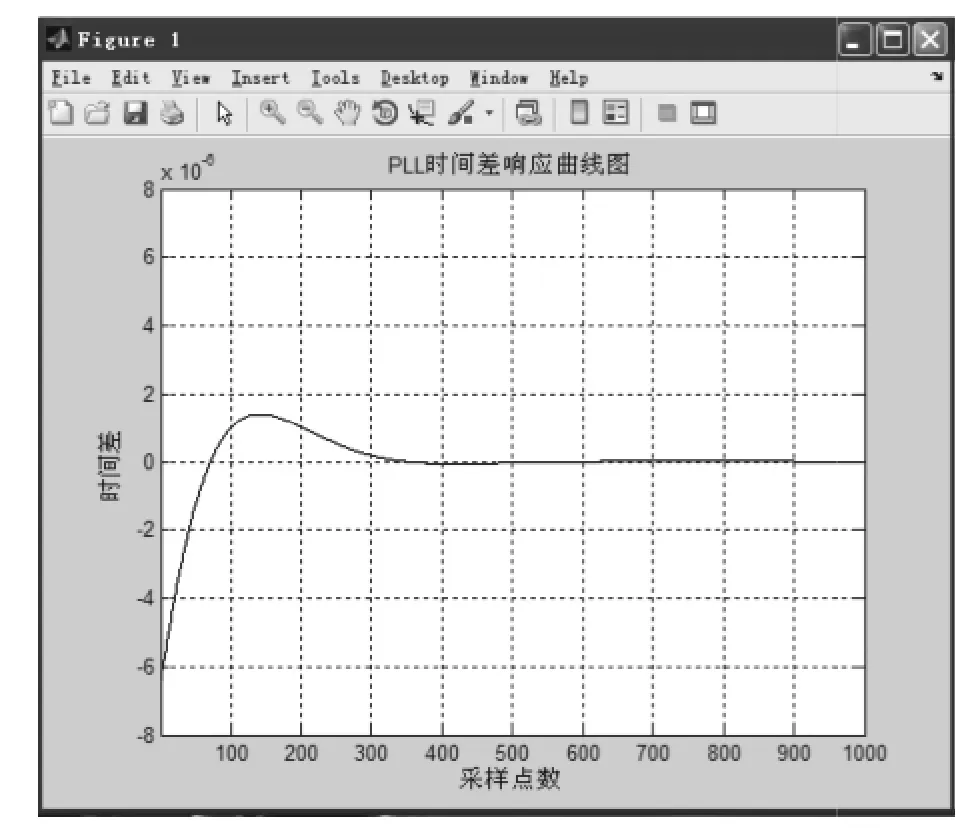

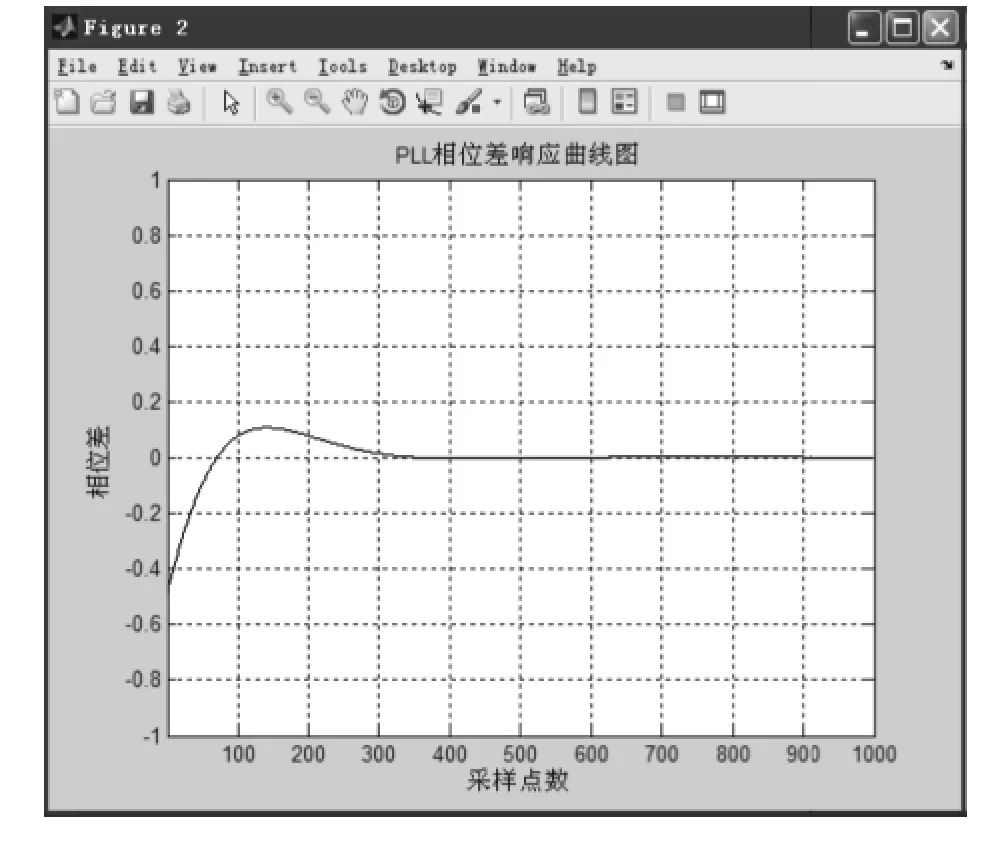

在Costas环的设计中,首先要处理好环路的时钟问题.在B(AC)码解调中,AD模块对输入B(AC)码信号以8kHz的速率采样.B(AC)码本身的载波频率为1kHz,即一个周期采样8个点.取环路噪声等效宽度为15Hz,环路更新时间为1ms.FIR低通滤波器的工作时钟为8kHz,本地NCO的累加时钟为8kHz,输出1kHz的载波.环路参数取c1=0.022 013,c2=0.000 247 22.用Matlab进行仿真,其结果如图6所示.环路在第350个左右采样点的位置锁定,跟踪时间约40ms.基于FPGA采用Costas环进行IRIG-B(AC)码的时间解调,在复位开始运行约40ms后,输出相位与输入的相位差开始趋近零.因为进行的是关于时间精度的问题,所以有必要将相位差转换为时间差.因为,

其中w为角速率(rad/s);Δφ为相位差(rad);Δt为时间差(s).

图7 输出与输入信号的时间差图

图6 输出与输入信号的相位差图

这样就可以将相位差转换为时间差,得到输入与输出之间的时间差.采用Matlab进行仿真,结果如图7所示.从图7可以得出跟踪时间约40ms后,输出的时间与输入的时间差趋近零,采用Costas环可以提高IRIG-B(AC)码的解码精度达到μs级别,满足电力系统的要求.

3 结束语

目前很多时间同步系统都采用GPS作为同步时钟源,虽然GPS是目前最成熟的授时定位系统,但是由于GPS受控于美国国防部,因此不能保证中国用户的利益.高精度的授时在我国国防科研、电力领域有着重要的保障作用,因此在获取时间信息方面要避免依赖别国技术而产生的危害,通过拥有自主知识产权的北斗系统,可以产生精度满足要求更为安全的时间信息来保障科研需求.

随着航天、通信、电力等领域对时间统一系统的要求越来越高,设计和实现高精度、体积小的时间统一终端变得日益重要.基于FPGA的IRIG-B(AC)码对时系统的设计与实现,在IRIG-B(AC)码解调中引入全数字Costas环,能够很好地提取出B(AC)码的过零点信息,这避免了在以往解调电路中使用过零检测电路时存在的零点漂移和脉冲抖动等问题,使得恢复的载波与输入B(AC)码的同步误差缩小至1μs的精度.采用FPGA进行IRIG-B编码方式对时的优点是精度高、数据全、不需要人工预置,缺点是编码复杂.

[1]谢黎,黄国方,沈健.数字化变电站中高精度同步采样时钟的设计[J].电力系统自动化,2009(1):61-64.

[2]刘俊俊,缪小松.提高过零检测精度的方法研究[J].工业控制计算机,2009,22(10):80-81.

[3]马红皓,胡永辉.GPS&IRIG-B时间系统分析[D].电子科技,2007,190(7):212.

[4]宋晓梅,杨金涛,荣庆华.基于FPGA的全数字触发器的设计[J].西安工程大学学报,2009,23(4):98-103.

[5]许宏国.北斗共视授时技术研究与设计[D].哈尔滨:哈尔滨工程大学,2007.

[6]冯娟,史浩山,赵宏伟.基于北斗授时信息的B码转换设计[J].信息安全与通信保密,2008(12):92-93.

[7]王卿,宋铁成.基于GPS技术进行精度授时的方法[J].电气电子教学教报,2007,29(4):34-38.

[8]VYAEHESLAV I V,lllYA E K,IRINA P C.Accurate time synchronization for digital communication network[J].Microwave&Telecommunication Technology,2007(10):259-260.

[9]郜洪亮,刘遵义.基于GPS和FPGA的便携式高精度同步时钟的研制[J].电力系统保护与控制,2009,37(2):80-82.

[10]周国平.基于FPGA时间同步技术的实现[J].电力系统,2010(8):72-74.

[11]National Semiconductor.DP83640 Precision PHYTER-IEEE 1588 Precision Time Protocol Transceiver[EB/OL].http:// www.national.com/analog.2009.

[12]Psomnath Paul.Low-overhead design technique for calibration of maximum frequency at multiple operating points[C]//Proc of IEEE International Conference on Computer-Aided Design.San Jose,2007:401-404.

[13]汪世辉,许生旺.基于匹配滤波和时间恢复算法的B(AC)码数字解调技术[J].飞行器测控学报,2008,27(4):41-43.

[14]张颂,杨景曙,胡海娜.直扩导航系统中数字科思塔斯环的FPGA设计与实现设计应用[J].世界电子元器件,2008 (12):80-84.

On improving the accuracy of time synchronization in the power system

SONG Peng,TIAN Le

(School of Electronics and Information,Xi'an Polytechnic University,Xi'an 710048,China)

In order to improve the accuracy of the system,the transmission of time information was demodulated based on FPGA.The COMPASS timing accuracy as a basis,IRIG-B code as the transmission timing information,in the use of FPGA demodulated IRIG-B code to introduced digital Costas loop,can well be extracted IRIG-B code zero crossing information,to avoid the zero-crossing detection circuit and pulse jitter zero drift problems.Simulation results showed that the algorithm reduce the IRIG-B code synchronization errors and improve accuracy for time to reach the power system on the accuracy requirements.

IRIG-B;FPGA;time synchronization;accuracy

TP 29

A

1674-649X(2014)01-0089-05

编辑:田莉;校对:孟超

2013-07-10

陕西省自然科学基础研究计划资助项目(ZD13JC2-15)

宋鹏(1976-),男,陕西省大荔县人,西安工程大学副教授,博士.E-mail:songpeng310@163.com