雷达信号处理器远程监控设计与实现

2014-06-23张开生李春化

张开生 陈 明 李春化

(西安电子工程研究所 西安 710100)

0 引言

现代雷达系统中,雷达控制计算机和信号产生板之间的控制信号主要是通过串口方式进行传输的,虽然串口传输方式电路结构简单、技术成熟且使用方便,但是串口传输方式具有其自身固有缺陷:传输距离受限、传输速度不高、抗干扰能力差。随着我国雷达技术的发展以及雷达组网的建设,大多数固定式雷达都架设在没有遮挡的较高塔台上,本地终端计算机安装在距离雷达较远的雷达操作室内,同样机动式雷达在结构设计上也用屏蔽网将雷达操控区与雷达机柜分割开,这样可以减弱雷达工作时微波辐射和噪声干扰[1]。同时,由于计算机技术和互联网技术的不断发展,越来越多的设备需要网络接入功能,以实现设备的远程监控[2]。因此,串口传输方式由于其固有缺陷,已经越来越难以满足系统的要求,需要一种新的控制信号传递方式。

针对串口控制的缺点,本文提出了基于SOC的雷达远程控制器,整个系统以Xilinx的Virtex-V FXT芯片为硬件核心,利用FPGA内部的逻辑资源搭建一个以软核CPU为核心的嵌入式系统,通过移植操作系统和网络协议栈,为系统提供多任务处理能力和网络接入能力。在远端的操控室中对雷达参数进行设置,然后将雷达参数通过以太网发送给信号处理器,从而实现对信号处理器的远程控制和参数修改。这种控制方式同传统的串口相比具有:传输距离远、传输速率高且抗干扰能力强的特点。

1 系统总体设计

本文主要针对现在雷达系统中以FPGA为基础的信号处理器,目前大多数信号处理都是基于FPGA器件,因为FPGA器件在底层算法实现上具有处理速度快、可重构性强和可编程的特点。在信号处理中,FPGA主要担当着中频数据的正交分解、采样速率转换、FFT等一些运算结构简单、数据处理量大和处理速度高的算法实现。在现代雷达系统中,根据特定的环境或者要求快速可靠的对算法的某些参数进行配置、修改或选择显得尤为重要。

目前对FPGA内部参数的配置、修改或选择主要是通过串口实现,但是串口传输距离受到限制,同时也只能进行点到点通讯,由于以太网传输方式相对串口传输方式的优点,可以将串口传输改为以太网传输。

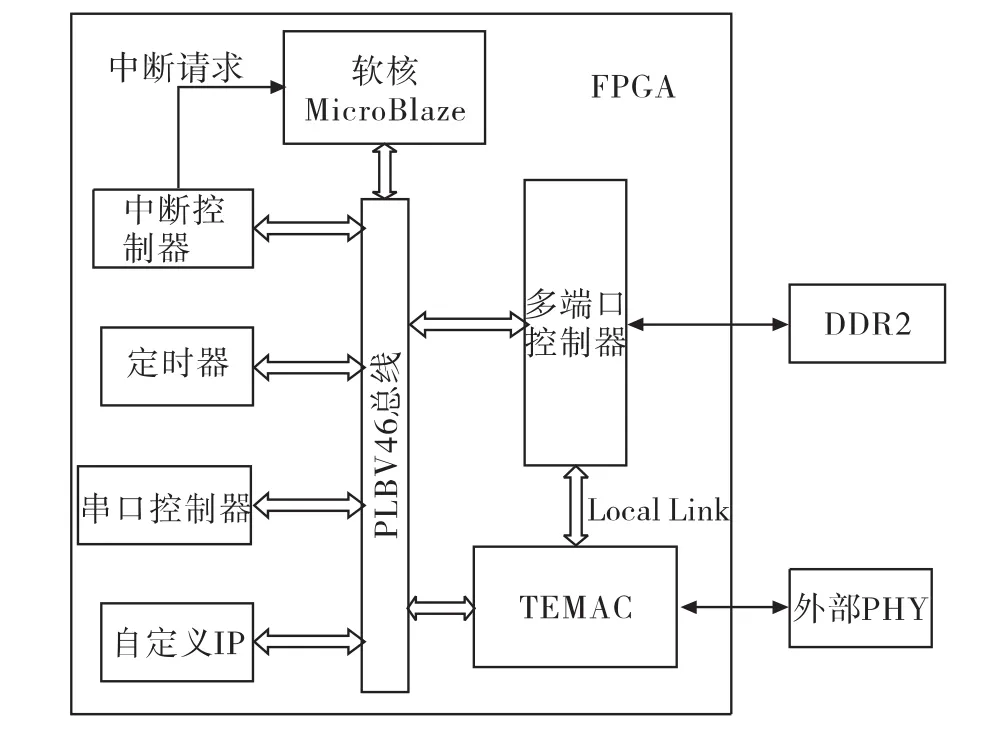

本设计的基础是利用FPGA内部逻辑资源编写雷达信号处理算法,当逻辑资源有富余的情况下,在FPGA内部嵌入软核CPU。所谓软核是完全用HDL(硬件描述语言)描述的实现特定功能的IP,它与实现技术无关,可以按使用者的需要进行修改,需要用户进行综合,并在其SOC上实现[3]。软核虽然占用了可编程逻辑器件的逻辑资源,但是为可编程逻辑器件提供了控制能力,增强了整个系统的灵活性。本设计采用的软核CPU是Xilinx公司提供的MicroBlaze。系统总体设计思路是以硬件为基础,在硬件平台上移植实时操作系统作为软件开发的系统平台,在硬件和操作系统的基础上进行应用层的开发,从而实现硬件与软件的有机结合,并扩展系统功能,使得整个系统具有结构层次分明的特点。为了提升系统的灵活性、降低开发和调试难度,所有硬件和软件的设计均采用模块化思想。在具有完整雷达信号处理器功能的硬件基础上,以FPGA为核心并辅以必要的外围电路模块构建嵌入式硬件服务器平台:控制计算机作为远程控制的客户端,服务器和客户端作为系统的硬件平台。系统总体框图如图1所示。

嵌入式硬件平台由软核CPU、程序和数据存储器、中断控制器、标准输入输出设备、网络传输设备、电源模块和其他外围设备组成。其中大部分硬件设备在FPGA内部都提供了相应的控制器。因此只需要调用相应的控制器并辅助以外围电路就可以很方便的搭建嵌入式系统硬件平台。

图1 系统总体框图

操作系统是连接底层硬件和用户之间的桥梁,用户通过操作系统的用户界面输入命令,操作系统则对命令进行解释,驱动硬件设备,实现用户要求[4]。因此操作系统对嵌入式系统而言是必不可少的。为了提高任务响应速度,本设计移植Xilinx公司的xilkernel作为操作系统,该操作系统移植方便、实时性强、并且Xilinx公司提供了良好的技术支持;在移植完操作系统之后,在操作系统基础上添加网络协议,为系统提供网络接入功能。由于嵌入式系统的存储空间受限,本设计选用源码开放的LWIP作为网络协议栈,另外该协议栈移植简单,功能完善,很适合嵌入式系统。在硬件平台的基础上移植了操作系统和网络协议之后,整个嵌入式软件开发平台就已建立起来,开发者就可以在此平台上进行应用层面的开发。

对于应用层开发,为了说明本设计在雷达信号处理器中的应用,实现了一个雷达发射信号脉冲参数的远程控制,其原理是在硬件层面中添加用户自定义的IP核作为远程控制的硬件。该IP核主要完成雷达发射信号脉冲的产生,通过在远程控制计算机上运行的客户端程序对发射信号脉冲参数进行设置,同时在雷达信号处理器中运行服务器程序,为客户端提供服务响应,当客户端设置的数据通过以太网传输到雷达信号处理器后,服务器程序接收配置数据然后更改IP核参数,从而实现信号处理器的远程控制;另外服务器程序也可以为客户端程序提供状态检测服务,实现雷达信号处理器的远程监控。

2 系统硬件设计

本系统采用的硬件平台式Xilinx的ML507评估套件,其搭载的核心芯片为Vertex-5 FXT。该芯片提供了丰富的硬件资源,内部集成以太网控制器硬核,片内Block RAM由36Kbit存储块组成(最多可达10Mbit),4个以太网MAC模块和内嵌6个PLL和12个DCM(时钟管理管道)用于满足复杂的时钟和时钟域需求。开发工具选择Xilinx公司提供的 EDK(Environment Development Kit)和 ISE,EDK主要完成嵌入式系统搭建和自定义IP核总线接口的创建,ISE主要完成对自定义IP核代码编写与功能仿真调试。

FPGA内部有一个PLBv46 master总线,所有内部模块都通过PLBv46总线slave接口进行连接,同时所有内部模块均使用内部的逻辑资源或固有硬件资源。CPU选择Xilinx公司的MicroBlaze,它是Xilinx公司提供的一款硬件功能可剪裁的软核CPU,该CPU采用哈佛RISC架构,具有32位独立的数据总线和地址总线,专门针对Xilinx的FPGA进行了优化。MicroBlaze使用32位指令集,3级流水,有32个32位的通用寄存器,可选的硬件乘法器,不支持用户自定义指令、协处理器、Cache、MMU,外部总线主要使用IBM的CoreConnect标准[5]。

在雷达信号处理器基本功能完整的情况下,以FPGA为核心构建嵌入式系统,整个系统硬件组成如图2所示。该系统由一片DDR2芯片用于存放和运行嵌入式系统的程序,其由内部的多端口控制器通过总线进行控制;一片Marvell 88E111芯片作为网络芯片,该芯片由内部的TEMAC进行控制,实现网络数据的收发;中断控制器实现各个模块的中断管理并向CPU发送中断请求;定时器为操作系统提供时钟基准;串口用于调试信息的输出和输出;嵌入式系统的搭建过程详见参考文献[6]。

图2 硬件系统组成框图

对于自定义IP核,采用软硬件协同的方法实现对自定义IP核的访问与控制,自定义IP核主要完成雷达信号处理器发射脉冲和定时信号的产生。该IP核主要利用EDK(嵌入式开发套件)软件提供的IP核接口软件创建IP核总线接口,内部逻辑在ISE软件中通过verilog语言实现功能描述,其主要功能是输出不同形式的脉冲重复信号,其占空比、重复周期、输出模式以及其他参数均可以通过IP核内部寄存器进行修改。对内部寄存器的修改可以通过编写相应的驱动程序来完成,图3的功能仿真图显示的是:将输入的ADC_Clk进行2分频作为发射脉冲信号的计数时钟ADC_div_clk,输出的发射脉冲信号为8个计数周期,高脉冲为2个计数周期。

图3 功能仿真

3 软件设计

选择EDK中内嵌的SDK(Software Development Kit)作为软件开发环境,为了实现各种任务的切换和处理,需要在硬件平台的基础上移植操作系统,为了在规定的时间内,对服务进行响应,需要一个实时操作系统,对于本平台可以移植ucos-II或者Xilinx公司提供的xilkernel,前者是一个完全开源的实时操作系统,而后者的内核操作和任务调度函数是通过函数库的形式提供给用户的,但是这两个操作系统在应用层系统函数上差别不大,为了较少移植难度,选择Xilinx公司的xilkernel作为本系统的操作系统。另一方面为了实现网络数据的传输,需要移植网络传输协议栈,选用的LWIP协议栈为系统提供网络服务,LWIP协议是一套用于嵌入式系统的开放源码的轻型TCP/IP协议栈,被设计用于存储容量有限的嵌入式系统[7],LWIP协议在设计之初就考虑了移植问题,同操作系统之间提供了专用的函数接口,在特定操作系统上移植只需要利用操作系统的系统函数实现接口函数功能即可,另外对于选定的PHY芯片,需要移植相应的网络芯片驱动程序。

对于发射脉冲触发信号IP核,编写相应的IP核驱动程序,实现对内部寄存器的读取,从而为上层软件提供标准的接口函数,实现对IP核的控制。

在移植完操作系统和网络协议栈之后,利用操作系统函数、网络协议函数和发射脉冲信号编写远程控制函数,在嵌入式系统上利用网络协议搭建一个网络服务器,远程控制计算机上编写客户端程序,客户端与服务器之间通过TCP协议进行可靠连接,客户端与服务器之间定义一套相应的通信协议,实现客户端和服务器之间的通信处理。控制流程为:

图4 处理流程图

a.在控制计算机上通过客户端程序对脉冲信号进行参数设置;

b.由于嵌入式系统内部的软核CPU效率较低,因此设置的参数与寄存器值的转换在控制计算机上完成;

c.转换之后的寄存器值通过网络传送给服务器

d.服务器接收到相应的命令后,对命令进行解析并对相应的寄存器进行修改,从而实现对脉冲信号参数的控制;

同时服务器程序也可以读取IP核的硬件信息或雷达信号处理器的其他信息,将信息进行打包然后传给客户端,客户端接收到数据之后对数据包进行解析,最后显示接收到的状态信息,从而实现雷达信号处理器的远程监控。

4 测试与结果分析

客户端程序运行在搭载Linux系统的控制计算机中,利用Linux系统提供的函数编写客户端程序,实现参数的设置、寄存器值转换、寄存器值发送和参数接收功能。服务器程序通过接收客户端发送的功能号和寄存器值,对相应的寄存器进行读取和更新,在完成相应操作之后向客户端发送应答信息和状态信息,客户端实现状态信息的显示。

测试时在客户端设置脉冲发射信号周期为100μs,脉冲宽度为40μs,客户端输入数据截图见图5。将输入数据转换为IP核内部寄存器存储格式,将设置的参数通过网络传输到服务器端,服务器接收到寄存器信息后更新寄存器值,实现参数修改。实际输出发射脉冲信号如图5所示。

图5 周期100μs脉冲宽度40μs输出实验图

图5中输入时钟为62.5MHz,分频系数为8,分频之后得到分频后时钟为7.812MHz,将该时钟作为计数器的计数时钟,由于计数器的值只能为整数,所以需要对计算出的计数器阈值进行截断处理,计数器阈值计算方法如下式:

其中N为计数器阈值,T为要输出脉冲宽度(单位:μs);fCNT为计数器输入时钟频率(单位:MHz),此处为7.812。以40μs脉冲宽度为例,理论计数器值为312.48,但由于数据的截断,得到的N值实际为312。因此由于数据截断所引起的最大误差为:

可以看出Errmax同输入时钟分频系数和输入时钟有关,对于计数器而言,分配系数越小,由数据截断所引起的误差越小,本实验中理论最大误差为:-0.128μs。试验中实际输出脉冲周期为99.96μs,脉冲宽度为39.92μs,实际输出信号在理论误差范围内,说明通过远程控制方式对雷达信号处理器参数控制的可行性。

5 结束语

本文讨论了基于FPGA的SOC的雷达信号处理器远程控制系统的实现方法,在信号处理器内部搭建服务器平台,同外界信息交换通过以太网实现,大大提高了系统设计的灵活性,同时提高了软件和硬件的扩展性和控制能力。在标准的传输协议的下,可以将控制计算机对雷达信号处理器的控制与监控变得模块化,使得硬件和软件同时具有可剪裁性。如果将雷达信号处理器中需要控制的模块添加一个标准的总线接口,将其连接到嵌入式系统中,即可实现对接入模块的远程控制。因此,本设计思想在雷达信号处理器中具有广阔的应用前景。

[1]范晖,曹俊武,徐谨,汪旭东.网络化显控终端系统的软件设计[J].测控技术.2011,30(8):87-90.

[2] 梅大成,柴志勇.基于SOPC的以太网实时数据采集系统设计与实现[J].计算机应用.2009,29(12):108-112.

[3]杨强浩.基于EDK的FPGA嵌入式系统开发[M].北京:机械工业出版社.2008.

[4]杨刚,肖宇彪,陈江等.32位嵌入式系统与SoC设计导论[M].北京:电子工业出版社,2006.

[5]赵峰,马迪铭.FPGA上的嵌入式系统设计实例[M].陕西:西安电子科技大学出版社,2008.

[6]张开生,陈明,周子超.FPGA上实时操作系统uCOS-II的实现.电子科技.2013,(10):36-39.

[7]Adam Dunkels.Design and implementation of the LwIP TCP/IP stack[M].Swedish Institute of Computer Science,2001.