基于ARM的频率源驯服设计与实现

2014-06-21杨剑青杨晓琴谢亮芦旭刘彪樊战友

杨剑青,杨晓琴,谢亮,芦旭,刘彪,樊战友,2

基于ARM的频率源驯服设计与实现

杨剑青1,2,3,杨晓琴4,谢亮1,芦旭1,刘彪5,樊战友1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院大学,北京 100049;4. 中国疾病预防控制中心,北京 102206;5. 中国兵器装备集团公司制导航空弹药研究开发中心,长沙 410100)

介绍了一种基于ARM处理器和CPLD技术的频率源驯服的软、硬件设计与实现方法。在ARM的控制下采用数字PID控制算法产生晶振控制电压,根据所测量的频率值与标称频率值之间的差值大小来调整对应电压控制字的步进幅度,进而达到快速对本地晶振驯服的目的。实验结果表明,驯服后的晶振输出的频率准确度比驯服前提高了大约一个数量级,达到了设计要求。

频率源驯服;准确度;ARM处理器

0 引言

时间作为一个基本物理量广泛应用于基础科学研究、国民经济和国防建设等领域。当前,我国正在大力布局建设的北斗卫星导航系统也是在我国高精度的时间频率标准相关学科技术迅猛发展的基础上发展起来的。无论是何种导航系统,时间基准都是其建立的根本。导航卫星上都携带有高精度原子钟,利用导航卫星提供的时钟信号驯服本地高稳晶振可以得到高准确度的频率信号,该方法具有成本低,效率高,成品体积小等优点,应用前景广阔,本设计就是在这样的思想基础上提出来的[1-2]。

早期的频率源驯服系统采用模拟或半数字体制,存在成本高,不易建立模型,调试困难和受环境因素影响大等缺点。随着数字技术的普及与发展,新研制的可驯频率源基本都是数字型,目前可驯钟技术发展迅速且日趋成熟,并在很多工程实践中得到广泛应用[3]。

1 频率源驯服系统的结构设计

频率源驯服系统所要达成的目标是:借助参考时钟对本地石英晶体振荡器输出频率信号进行脉冲计数测频,将测量所得频率值与标称频率比对,计算并产生电压调整量对石英晶体振荡器进行控制以达到对其输出频率信号进行校准的目的。本文中的频率源指压控恒温晶体振荡器。

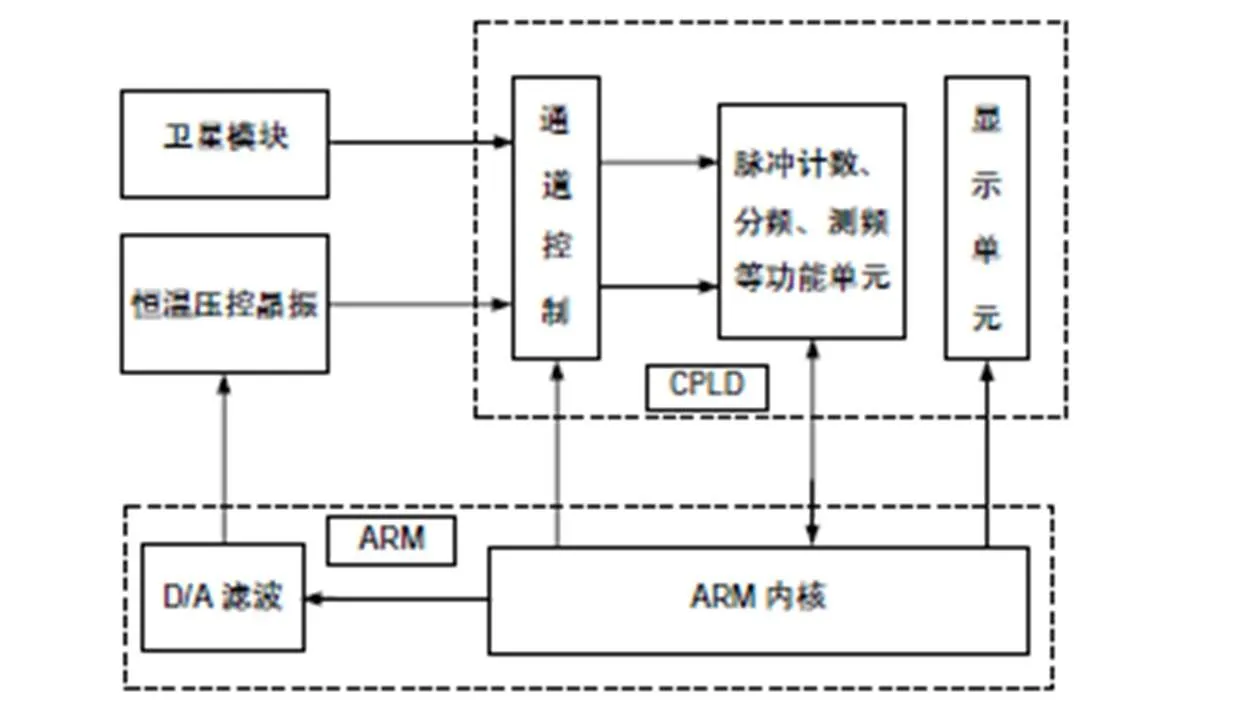

该频率源驯服系统主要由参考秒脉冲信号1PPS(pulse per second)、本地恒温晶振、脉冲计数测频单元、计算与控制器(即处理器)、数模变换单元和LMB162A显示液晶屏幕组成,其中脉冲计数测频单元由CPLD(complex programmable logic device)编程实现,而处理器和数模变换单元由ARM编程实现。该频率源驯服系统总体结构框图如图1所示。

图1 频率源驯服系统结构框图

通过运用复杂可编程逻辑器件(CPLD)实现如下功能:对本地晶振输出的频率脉冲信号进行计数,并测量出本地晶振输出频率值。脉冲计数测频单元将得到的脉冲计数值送到ARM处理器中,处理器根据计数值求出晶振频率值,并根据测量值与标称值之间的差值判断晶振输出频率信号的变化快慢,产生相应的控制电压输送到晶振控制端;处理器持续地接收脉冲计数值,从而实时监控晶振输出频率变化的快慢并作出相应的控制使其频率尽可能地维持在标称频率值附近。

图1中卫星模块所提供的秒脉冲信号1 PPS作为校频系统的参考时钟,参考时钟亦可是其他标准时间,在实验阶段同时采用国家授时中心钟房秒信号作为辅助参考时钟。本系统要求参考时钟精度比本地晶振输出秒脉冲信号的精度至少高1~2个数量级,否则无法保证脉冲计数测频所得频率值的准确性,亦失去频率测量校准的意义。此处参考时钟有两个作用:一是作为脉冲计数测频单元的参考时钟;二是通过脉冲计数测频单元为控制器提供中断控制信号。由于信号通过脉冲计数测频单元会有延迟,这样可以保证参考秒信号与脉冲计数值同时抵达控制器。

本地恒温晶振(VCXO)是系统的时钟频率源,为CPLD提供时钟信号,也是被校准的对象。

脉冲计数分频、测频等功能单元的功能是对本地恒温压控晶振输出的频率脉冲信号进行脉冲计数并测量得到本地恒温压控晶振的输出频率。

控制器单元主要对脉冲计数测频单元送来的脉冲计数值和中断控制信号(参考秒信号)进行综合分析、判断与计算,求出当前频率值,并根据频率值判断产生合适的控制电压,同时产生相应的控制信号控制LMB162A液晶屏幕显示等。

数模变换单元的功能是产生模拟电压,是嵌入在ARM处理器中的一个功能模块,电压分辨率为 1mV,使用时在对ARM处理器D/A单元初始化并写电压控制字即可实现数模变换产生电压值。

在显示单元中,LMB162A显示液晶屏幕接收来自ARM处理器的控制信号,将晶振工作状态是否锁定(locked)、电压控制字以及计算得出的频率值等信息实时地显示在液晶屏幕上。

在系统启动后,首先,由卫星导航接收机在信号有效后所提供的1PPS信号作为脉冲计数测频单元的闸门信号并在控制器中产生中断,控制器根据中断的次数决定程序的执行顺序。脉冲计数测频单元模块对经过波形调整的晶振10 MHz信号进行脉冲计数测频。与脉冲计数测频单元相关的控制信号有3个,它们分别是START_CTRL、END_CTRL和Shift_Clk。START_CTRL和END_CTRL分别为脉冲计数测频单元的开启和关断控制信号,高电平有效。在设计中START_CTRL和END_CTRL要结合标准秒信号的上升沿共同作用才能清零脉冲计数测频单元(开始计数)或者使脉冲计数测频单元停止计数。在可驯钟初始化完成后系统开始正常工作,脉冲计数测频单元在START_CTRL有效后的第一个秒脉冲上升沿开始计数,而在关断信号END_CTRL有效后的第一个秒脉冲上升沿停止计数并锁存计数值以备控制器读取,控制器在这一特定脉冲的上升沿产生中断并将计数值读出,控制器在读取数据并作处理后与标称频率值进行比对,并产生控制电压对本地晶振进行驯服。控制器将补偿计算后的频率值以及产生的电压控制字实时显示在LCD屏幕上。

2 硬件电路设计

该设计中所使用的本地恒温晶体振荡器为广东中晶电子有限公司出品,型号为CO3605-10.000,所选用的CPLD是Altera的MAX®3000A系列,ARM(advanced RISC machines)控制芯片为LPC1768 Cortex- M3微控制器,选用的显示模块是LMB162A字符型液晶显示模块[4]。

计数测频单元由在CPLD内部形成的多个十进制计数器(74HC390)链路组成,以完成对全局时钟的计数测频功能。另外由4个74165(并进串出移位寄存器)构成一个32位移位寄存器,对中间的计数值和测量结果锁存并输出到ARM,由ARM基于测量数据,并根据事先设计好的一些算法,进行分析、处理、最后产生相应的控制信号。

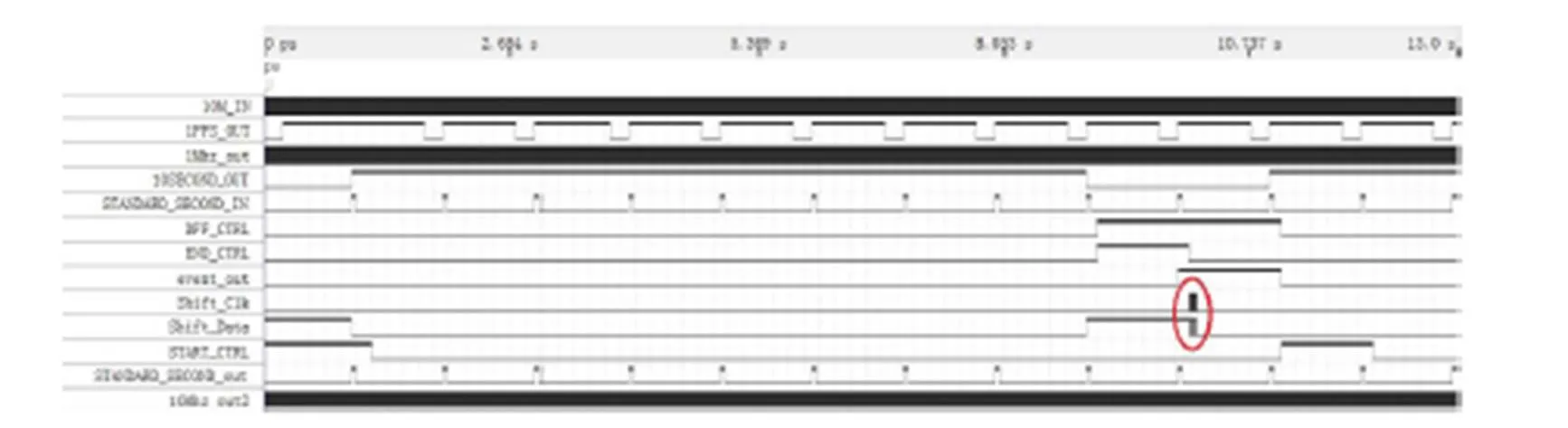

在完成相应控制信号的设置后,对CPLD功能进行仿真,结果如图2所示。

图2 CPLD功能仿真图

为便于观察图2中控制信号—锁存器移位时钟(Shift_Clk)和数据值(Shift_Data)的变化,将图中该部分仿真结果放大如图3所示,可看到在关门信号之后控制器输出移位时钟信号及数据值变化情况,从图3中我们可以读出计数值为89999999,经过补偿加1后为90000000,这一数值正是从开门到关门的9s内所应该计得的正确计数值(说明:各控制信号以及频率时钟在设置时软件都是按照标称值处理计算的,所以结果也是无误差的理想结果)。

图3 移位时钟和数据值的仿真图形

3 软件设计

图4为控制器软件设计流程图。ARM上电后首先对LMB162A显示、数模转换器DAC、外部中断和引脚连接等各功能模块及参数进行初始化,使DAC产生2.5 V控制电压(2.5 V为压控晶振的中心电压)并由LCD显示。设置与运算相关的一些控制参数,如设置多长时间完成一次频率测量。然后开启中断,进入循环程序。在循环程序中,检测中断程序中设置的标志位并进行相应的处理。如果发生中断,一些紧急、用时少的任务直接在中断程序中处理;不甚紧急、用时较多的任务则通过设置标志在中断之外的专门处理子程序中处理。专门处理子程序执行完要清除相应的标志位。专门处理子程序的主要任务就是根据并进串出移位寄存器送来的测量数据,计算并判断可驯频率源目前的输出频率的大小以及与其标称值的误差程度,然后根据相应的算法,通过调节D/A单元,产生相应的调节修正信号,使加在可驯频率源上的控制电压发生变化。这样的测控过程要循环多次。并且控制过程中被驯频率源的输出频率可能会出现一会儿大于其标称频率,一会儿又小于其标称频率的震荡现象。但最终被驯频率源的输出频率会稳定在以其标称频率为中心的一个很小的、误差允许的范围内。

为了避免或减小输出频率的震荡现象,软件中采取了PID(proportional integral derivative)控制算法。PID控制算法的增量型数学表达式如下所示:

式(1)中,为n时刻控制量的增量(本设计中为控制电压步进值),为比例增益,为比例带,为积分系数,T为控制周期,为积分时间,称为微分系数,为微分时间。当频率被校准到系统最小频率范围内时,锁定控制电压并延迟1h,之后再重新进行校频过程[5]。

4 测试原理及方法

在完成电路的焊接工作后,首先用万用表对电路的电源及信号走线的通断状况进行全面的检查,在确认无误的情况下将编写好的程序分别下载到相应的芯片中,在整个测试工作中主要用到了个人计算机、高精度时间间隔计数器、示波器、万用表等设备及仪器。程序成功下载到芯片中后我们就开始对系统进行正式的运行监测,通过安装在个人计算机上的串口数据接收软件、示波器以及LCM1602C显示屏,我们对系统的实时运行状态进行观察与监测,并自动记录数据。在运行中,一旦发现数据异常或者出现系统运行错误的情况,马上分析原因并对芯片中的程序做出修正直至系统能稳定无误地运行。

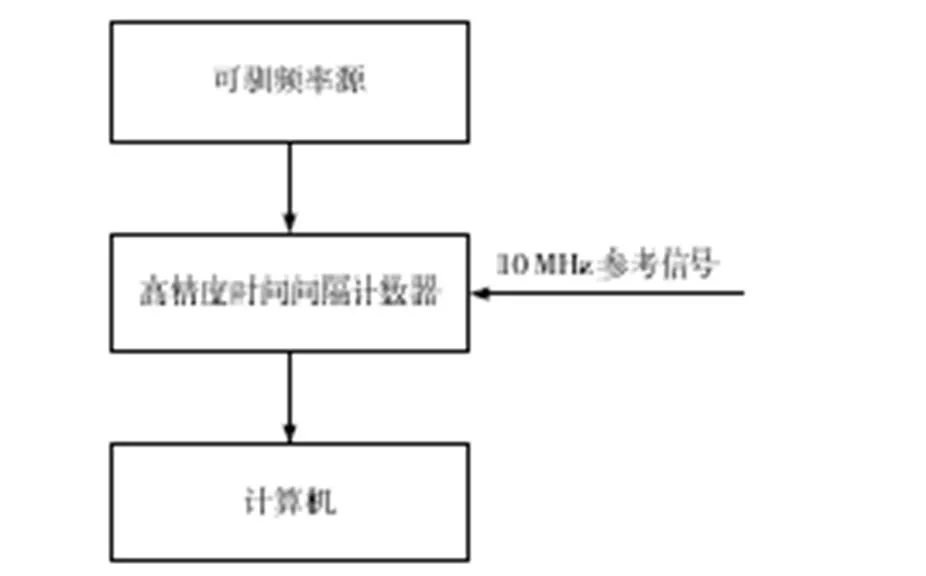

可驯频率源输出频率信号测试原理如图5所示。测试工作需要的仪器与工具主要是可驯频率源,高精度时间间隔计数器和个人计算机。辅助设备包括万用表、示波器等。图5中可驯频率源将校准后的频率信号输送给高精度时间间隔计数器,高精度时间间隔计数器对接收的频率信号进行测量得出频率值并将该频率值同步送到个人计算机进行记录,以待后续分析用。

图5 可驯钟输出频率信号测试原理图

5 实验结果

图6为我们设计与实现的可驯频率源的硬件电路实物图。由图6可以看出,系统采用了ARM和CPLD相组合的数字集成电路对压控振荡器进行驯服,极大地减少了分立器件的使用,从而缩小了电路规模。

图6 可驯频率源硬件电路实物图

该电路板采用双层设计,供电电压为5 V。CPLD芯片采用JTAG(Joint Test Action Group,联合测试行动小组)方式进行编程和调试,ARM芯片则使用较为方便的ISP(internet service provider)方式进行程序下载。

在工程完成后对本地压控晶体振荡器驯服前后的频率值进行了统计和分析。本地压控晶体振荡器标称频率10.000MHz,准确度优于1×10-8,压控电压范围2.5V±2.5V,短稳优于2×10-11,工作电压 +5×(1±5%)V,工作电流≤3000mA。

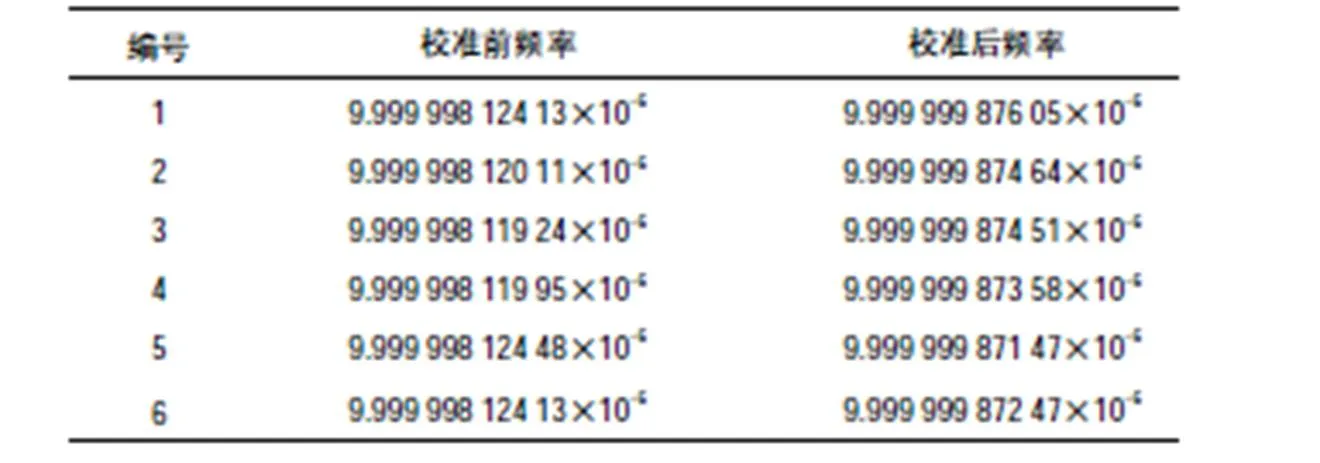

在统计和分析前,首先要对晶振的频率值进行采集,本地晶振频率信号通过串口传送到计算机并由专门的串口调试工具采集和记录频率值。在系统经过12h连续不间断的运行后得到一组频率值数据,然后运用软件MATLAB对得到的这一组频率值数据进行计算,得出频率准确度[6]。其中驯服之前的频率准确度为1.756×10-7,驯服之后为1.125×10-8。压控振荡器的频率准确度较驯服之前提高了一个数量级。表1为晶振校准前、后稳定状态的部分数据。表1中第1栏编号表示在相应频率数据中每隔10 min取样值编号,后2栏分别表示校准前、后记录的频率值。

表1 晶振校准前、后部分数据 Hz

6 结论

本文在频率源驯服的设计思路和控制方式上与以往可驯钟的实现有较大不同。以往系统对电压控制字的产生主要通过对可驯频率源和参考钟之间的时差值进行处理而获得,而本系统的核心是对晶振输出频率的测量,且不需要高分辨率的时间间隔计数,减少了系统的复杂度。系统所有的控制信号均由ARM处理器产生,减少了控制信号对信号源的干扰。本文给出的测试数据和统计结果表明,经过驯服之后的压控振荡器输出频率的准确度相较于驯服之前提高了一个数量级。因此,该方法设计的可驯压控振荡器可广泛应用于高频电路系统,如手持通讯设备、测量设备,以及通信导航等领域。

[1] 张帆, 胡永辉, 何在民. GPS可驯钟的设计与实现[C]//第三届中国卫星导航学术年会电子文集, 北京: 中国导航学术年会组委会, 2012.

[2] 李方洲, 张建平. 高精度压控晶振频率控制特性分析及控制系统[J]. 电子测量技术, 2000, 1: 22-24.

[3] 向渝. 数字可驯钟系统设计与应用研究[D]. 西安: 中国科学院国家授时中心, 2008.

[4] 谢亮, 芦旭, 吴成英, 等. 基于ADF4360-8的锁相环频率合成器的设计与实现[J]. 时间频率学报, 2013, 36(2): 75-83.

[5] 王锦标. 计算机控制系统[M]. 北京: 清华大学出版社, 2008.

[6] 李孝辉, 杨旭海, 刘娅, 等. 时间频率信号的精密测量[M]. 北京: 科学出版社, 2010.

[7] 周立功. ARM嵌入式系统基础教程[M]. 北京: 北京航空航天大学出版社, 2005.

[8] 谭浩强, 张基温. C语言程序设计教程[M]. 3版. 北京: 高等教育出版社, 1991.

Design and implementation of frequency-sourcedisciplining based on ARM

YANGJian-qing1, 2, 3, YANG Xiao-qin4, XIE Liang1, LU Xu1, LIU Biao5, FAN Zhan-you1,2

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China;2. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center,Chinese Academy of Sciences, Xi′an 710600, China;3. University of the Chinese Academy of Sciences, Beijing 100049, China;4. Chinese Center for Disease Control and Prevention, Beijing 102206, China;5. Guidance Aerial Ammunitions Research and Development Center, Chinese Weapon Equipment Group Company, Changsha 410100, China)

Ahardware/softwaredesign and its implementation for frequency-source disciplining based on ARM processor and CPLD(complex programmable logic device) are introduced. Under the control of ARM processor, the control voltage for crystal oscillator is obtained by adopting the digital PID control algorithm, and then the size of step of corresponding voltage control bit is adjusted according to the frequency difference between the measurement and the nominal value, which aims at achieving a fast tamable local crystal oscillator. The experiment results show that the accuracy of the output frequency of the crystal oscillator is improved by one order of magnitude after disciplining, which meets the design requirements.

frequency-sourcedisciplining; accuracy; ARM processor

TN874+.2

A

1674-0637(2014)04-0206-07

10.13875/j.issn.1674-0637.2014-04-0206-07

2013-11-26

国家自然科学基金资助项目(10773012)

杨剑青,男,硕士,主要从事量子频标、精密时间频率测量终端技术的研究。