一种结合硬件特征的并行内存故障检测方案

2014-06-02吴俊敏

胡 蝶,吴俊敏,2

一种结合硬件特征的并行内存故障检测方案

胡 蝶1,吴俊敏1,2

(1. 中国科学技术大学计算机科学与技术学院,合肥 230027;2. 中国科学技术大学苏州研究院,苏州 215123)

针对March类内存检测算法越来越复杂、检测时间越来越长,且更适用于对嵌入式内存芯片的检测等问题,提出一种结合硬件特征的并行内存故障检测方案。该方案包括2种并行检测方法:(1)根据DDR2的结构和工作原理设计的芯片级并行,可以并行检测一个DDR2内部的多个内存芯片。(2)根据访存控制器的结构和工作原理设计的访存控制器级并行,可并行检测多个DDR2内存条。对于芯片级并行,访存带宽越大,即并行检测的芯片个数越多,并行效果越好,从1个芯片到并行检测8个芯片,内存的检测时间几乎是呈线性递减的。对于访存控制器级并行,访存控制器数量越多并行效果越好,从1个LMC到2个LMC,内存的检测时间几乎减少了一倍。实验结果表明,2种并行检测方法不仅能够成倍加快检测速度,而且更适用于用户对内存的检测。

故障模型;March算法;DDR2内存条;芯片级并行;访存控制器级并行

1 概述

内存故障可以简化为以下5种故障模型:固定故障 (Stuck-at Fault, SAF)[1],转换故障(Transition Fault, TF)[2],耦合故障(Coupling Fault, CF)[3],寻址故障(Address Decoder Fault, ADF)[4],数据保留故障(Data Retention Fault, DRF)[5]。

根据故障模型,人们设计出了许多March算法,如MATS、March X、March C、March A、March Y等。随着存储技术的不断发展,内存芯片的密度越来越高,不仅耦合故障的发生概率越来越大,还出现了更难检测的动态故障。为了满足需求,人们又设计出了多种更复杂的March算法,如March SR[6]、March SS[6]、March DSS[7]、March AB[8]、March MSS[9]。这些复杂的March算法虽然能够检测多种故障类型,检测时间却成倍地增长。另外,这些算法都是被设计用来检测一个内存芯片内部的单元是否存在故障,并且已存在大部分并行检测算法[10]是从硬件方面设计的,更适用于对嵌入式内存芯片的检测[11],并不适用于用户。

针对以上问题,本文提出一种结合硬件特征的并行内存故障检测方案,它能够有效地解决上述2个问题:既可以成倍地降低March算法的检测时间,又能让用户利用March算法在短时间内对内存进行检测。该方案包含2种并行内存检测方法:(1)根据DDR2的结构和工作原理而设计的芯片级并行;(2)根据访存控制器的结构和工作原理而设计的访存控制器级并行。

2 DDR2结构分析

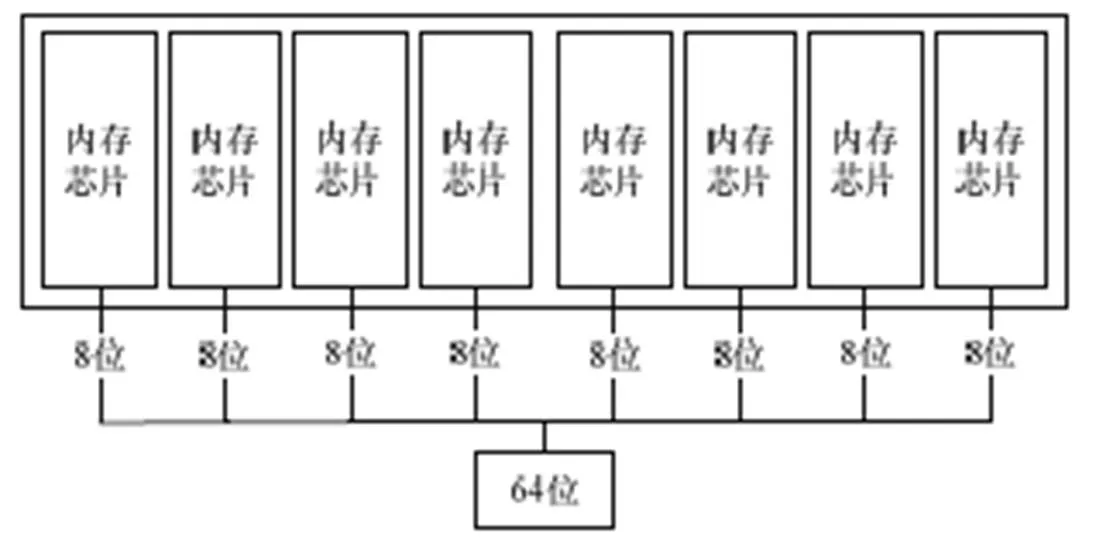

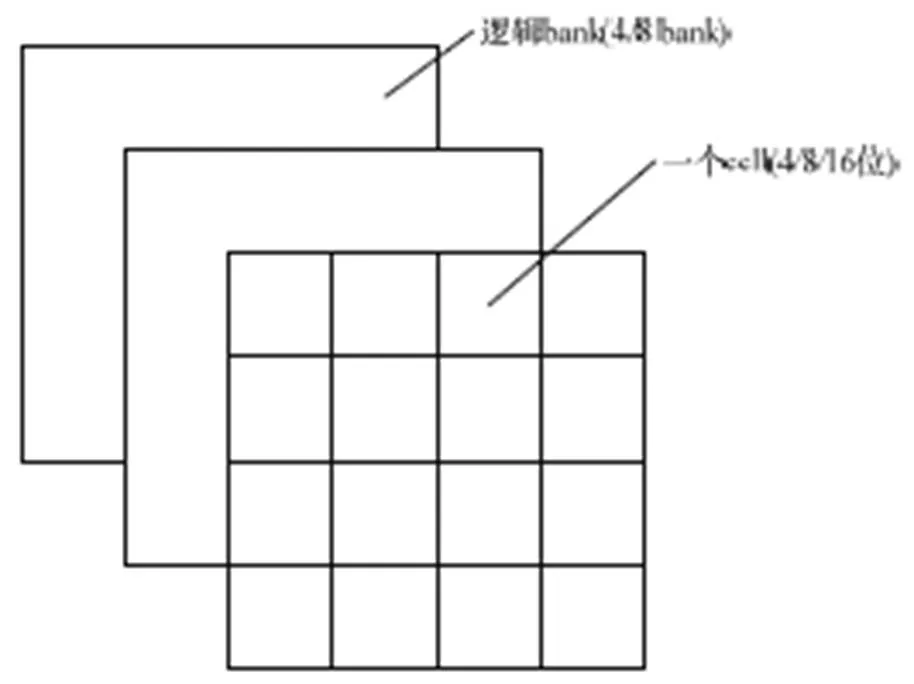

如图1所示,内存条是由多个内存芯片构成的。内存芯片是由4个或8个逻辑bank(L-bank)组成。图2是内存芯片的结构示意图。逻辑bank[12](L-bank)是一张以内存单元为单位写入的矩阵,每个内存单元称之为cell,一个cell的大小为4/8/16位,即内存芯片的位宽。对于每个L-bank,只要指定一行(Row),再指定一列(Column),就可以定位到某个cell。在一个时钟周期内,内存芯片只允许对一个L-bank进行操作,而不是对芯片内所有L-bank同时操作。L-bank的地址线是通用的,只要再有一个L-bank编号加以区别就可以了(L-bank 0~L-bank 3)。

图1 内存芯片位宽为8位的DDR2结构

图2 内存颗粒内部结构

目前,CPU与内存之间(就是CPU到DIMM槽)的接口位宽是64位,即一个物理bank(P-bank),这64位由多个内存芯片共同组成,例如位宽是8位的内存芯片,一个P-bank由8个内存芯片组成,如图1所示。每次CPU与内存条交换64位的数据时,分别从所有的内存芯片中存取一个cell。

3 并行检测原理

本文根据2个硬件特征设计了2种并行内存检测方法:(1)根据DDR2的组成结构和工作原理并行检测内存条中的多个内存芯片,这种检测称为芯片级并行;(2)根据访存控制器的设计和工作原理并行检测多个内存条,这种检测称为访存控制器级并行。

3.1 芯片级并行

双列直插式存储模块(Dual-Inline-Memory-Modules, DIMM),负责访存控制器与内存模块之间的数据交换。DIMM提供了64位的数据通道,这64位数据分别来自同一个物理bank(P-bank)中的所有内存芯片,目前DDR2的P-bank通常由8个数据位宽是8位的内存芯片组成,所以每次读/写内存时,相当于从这8个内存芯片中分别读/写 1个字节的数据(即一个cell)。因此,在检测内存时,以 64位为单位,每次读/写8个字节,并行检测8个内存芯片,从而成倍地提高内存检测的速度。

访存操作每次处理的数据单元可以是一个字节,半个字和一个字。通常,一个字节是8位。对于32位机,一个字为32位,半字即16位。对于64位机,一个字为64位,半字即32位。因此,根据DDR2工作原理,当内存芯片位宽是8位时,32位机一次能够并行读/写的内存芯片个数可以是1个、2个和4个;64位机一次能够并行读/写的内存芯片个数可以是1个、2个、4个和8个。把这种一次并行读/写个芯片的检测方法叫作-chip(s)并行,其中=2。

实验环境是64位机,既可以采用32位模式,也可以采用64位模式。因此,可以研究1-chip并行、2-chips并行、4-chips并行和8-chips并行之间的关系。图3是芯片级并行检测算法流程。

图3 芯片级并行检测算法流程

3.2 访存控制器级并行

多核体系结构的计算机一般会有2个或者2个以上访存控制器(Local Memory Controller, LMC)。图4是LMC的结构,LMC之间可以并行操作内存,因此,可以利用多个LMC并行检测多个DDR2内存条。

图4 内存控制器结构

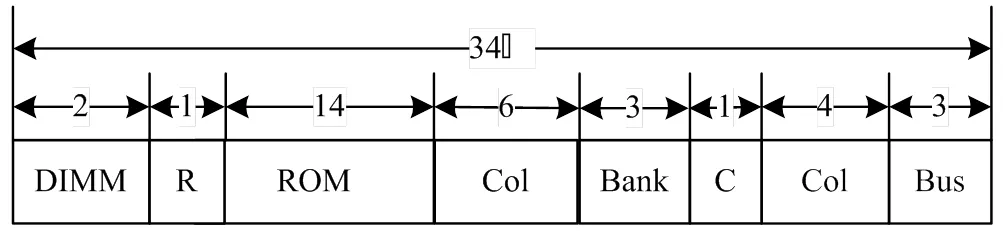

这里根据Cavium Networks公司的MIPS多内核处理器CN54/5/6/7XX具体描述怎样并行检测。CN54/5/6/7XX有 2个访存控制器(LMC),每个LMC支持4个DIMM,每个DIMM最大支持2 GB的内存条。CN54/5/6/7XX最大支持16 GB的内存。有49根地址线,只用最低34根地址线构成16 GB的地址空间。16 GB的内存安排如下:

DR0: 0x0 0000 0000 0000 to 0x0 0000 0FFF FFFF = low 256 MB

DR1: 0x0 0004 1000 0000 to 0x0 0004 1FFF FFFF = mid 256 MB

DR2: 0x0 0000 2000 0000 to 0x0 0003 FFFF FFFF = upper 15.5 GB

如图5所示,34位地址的地址映射关系如下[13]:

第7位:当前读/写的字节位于哪一个访存控制器。0:访存控制器0,即LMC0;1:访存控制器0,即LMC1。

第33位、第32位:当前读/写的字节位于哪一个DIMM。00:DIMM0;01:DIMM1;10:DIMM2;11:DIMM3。

第31位:当前读/写的字节位于哪一个Rank(物理bank)。0:Rank0,即物理bank0;1:Rank1,即物理bank1。

第2位~第0位:当前读/写的字节位于哪一个内存芯片上。000:内存芯片0;001:内存芯片1;010:内存芯片2;011:内存芯片3;100:内存芯片4;101:内存芯片5;110:内存芯片6;111:内存芯片7。

第10位~第8位:当前读/写的字节位于内存芯片的哪一个逻辑bank中。000:L-bank0;001:L-bank1;010:L-bank2;011:L-bank3;100:L-bank4;101:L-bank5;110:L-bank6;111:L-bank7。

第30位~第17位:当前读/写的字节所在逻辑bank内的行地址。

第16位~第11位和第6位~第3位:当前/读写的字节所在逻辑bank内的列地址。

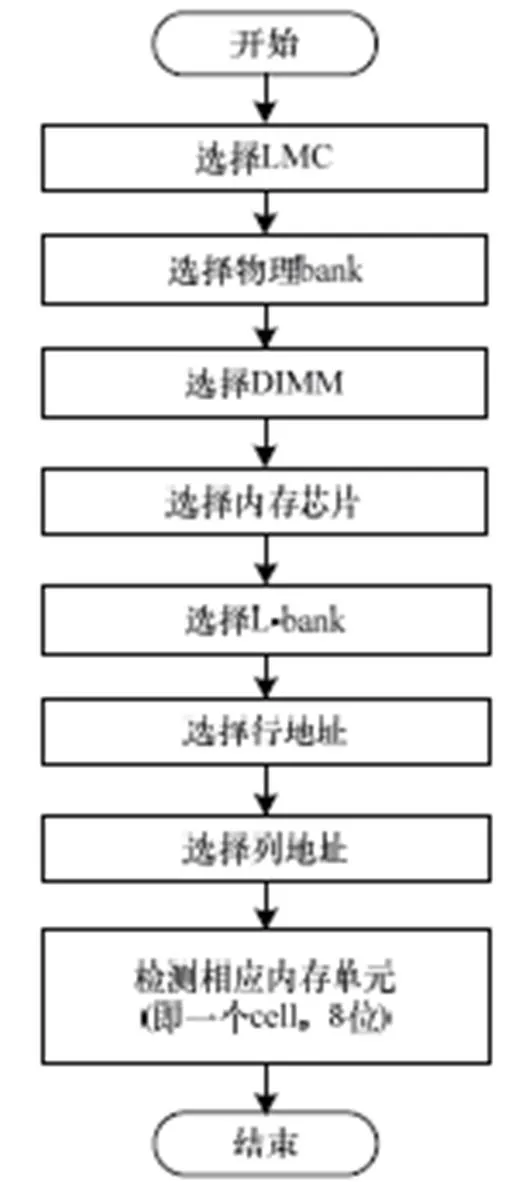

图5 34位地址的地址映射

从以上地址映射关系来看,不可以使用传统的内存检测方法,即按照地址顺序依次检测内存,必须按照地址的映射关系从新排序内存的地址顺序来检测内存。从新排序的思想就是:把每一个对应的地址块按照所在位置左移,然后加起来,就是新的内存检测的地址顺序,如第7位是LMC,则把它左移7位。又因为一个周期内可以读/写 64位,即8个字节,这8个字节又分别来自不同的内存芯片,所以每次进行64位读/写,每次对8个内存芯片读/写一个字节,这样可以结合芯片级并行,从而成倍地提高内存检测速度。下列代码是按照地址映射关系从新排序的内存检测代码,检测流程如图6所示。

If( coremask == 0) //核0检测LMC0管理的内存

LMC = 0;

Else if( coremask == 1) //LMC1管理的内存核1检测

LMC = 1;

For( DIMM = 0; DIMM <= 3; DIMM++ ) //选择DIMM

For( Rank = 0; Rank <= 1; Rank++ ) //选择物理bank

For( Chip = 0; Chip <= 7; Chip++ ) //选择内存芯片

For( Bank = 0; Bank <= 7; Bank++ ) //选择芯片内部的//L-bank

For( Row = 0; Row < 214; Row++ ) //选择行 //地址

For( Col = 0; Col < 210; Col++ ) //列地址

{

Addr = (LMC<<7) + (DIMM<<32) + (Rank<<31) + Chip+ (Bank<<8) + (Row<<17) + ((Col&0xF)<<3) + ((Col&0x3F0)<< (11-4));

读/写64位即8个字节;

…

}

图6 按照地址映射关系排序的并行检测流程

4 实验结果分析

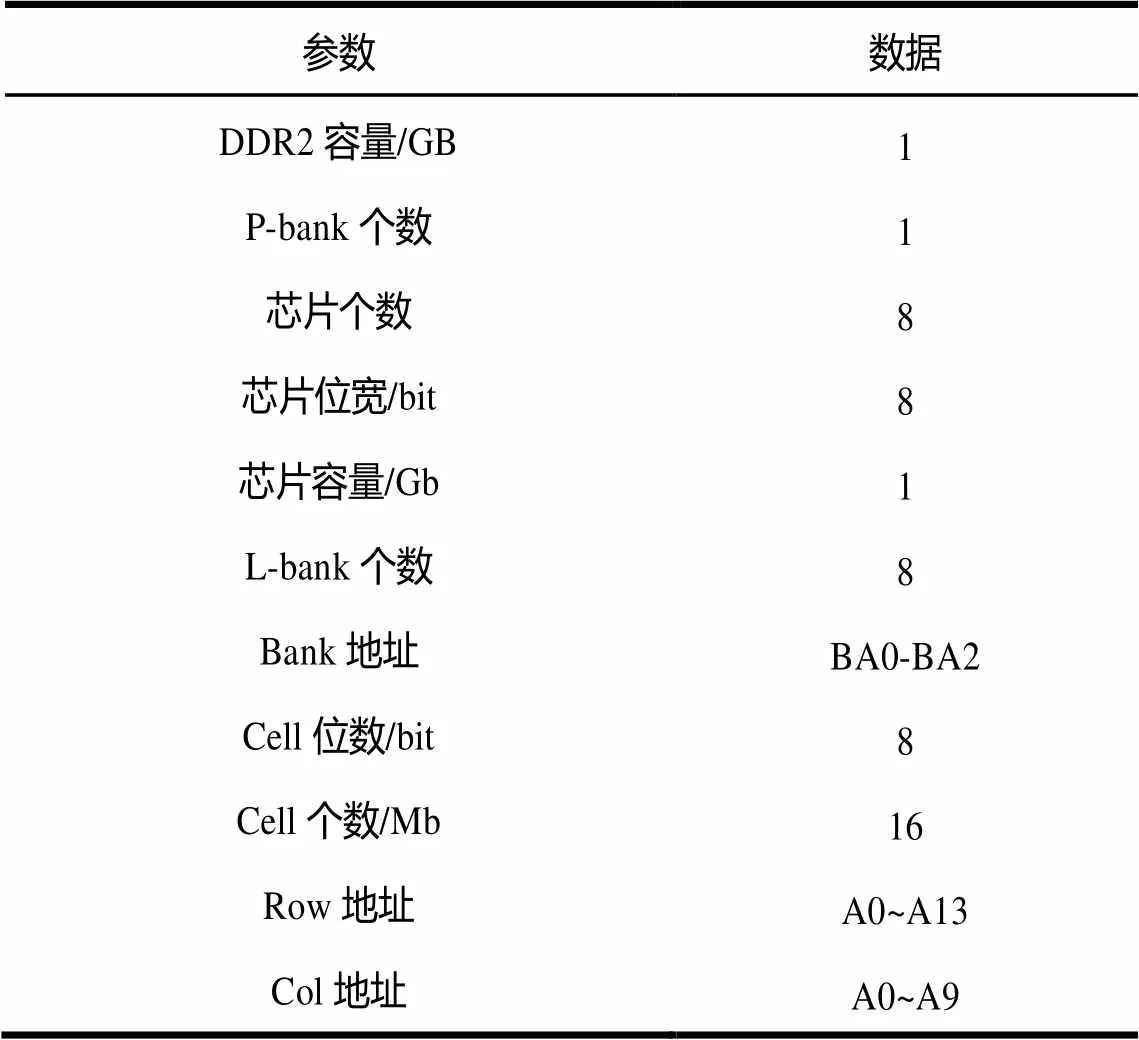

本文实验基于Cavium Networks公司的MIPS多内核处理器CN54/5/6/7XX。CN54/5/6/7XX配置了12个64位的CPU,2个访存控制器(LMC),每个LMC支持4个DIMM,每个DIMM最大支持2 GB的内存条。CN54/5/6/7XX最大支持16 GB的内存。内存条规格如表1所示。

表1 内存条DDR2规格

实验主要面向3个方向:(1)面向芯片级并行,实验分析了1-chip并行、2-chips并行、4-chips并行和8-chips并行之间的关系;(2)面向访存控制器级并行,由于实验环境只提供了2个LMC,因此只比较了1-LMC并行和2-LMC并行;(3)结合芯片级并行和访存控制器级并行,实验分析了2种并行检测方案结合的效果。

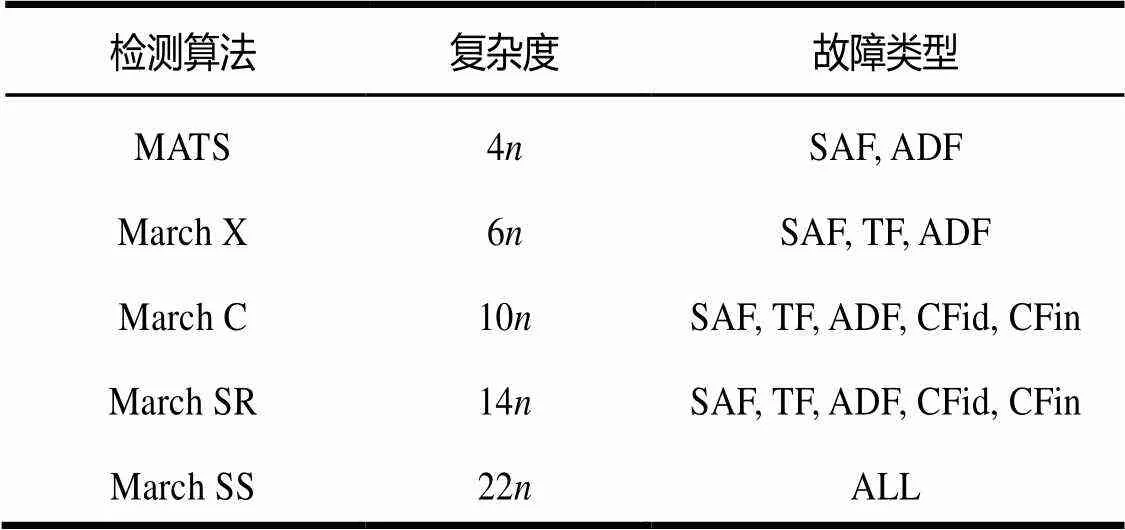

为了使实验具有全面性,选择了5种具有代表性的March算法,它们分别是:MATS, March X, March C, March SR和March SS。根据表2可知,它们的复杂度依次递增,故障覆盖率也随之递增[14]。

表2 实验使用的5种算法

4.1 芯片级并行

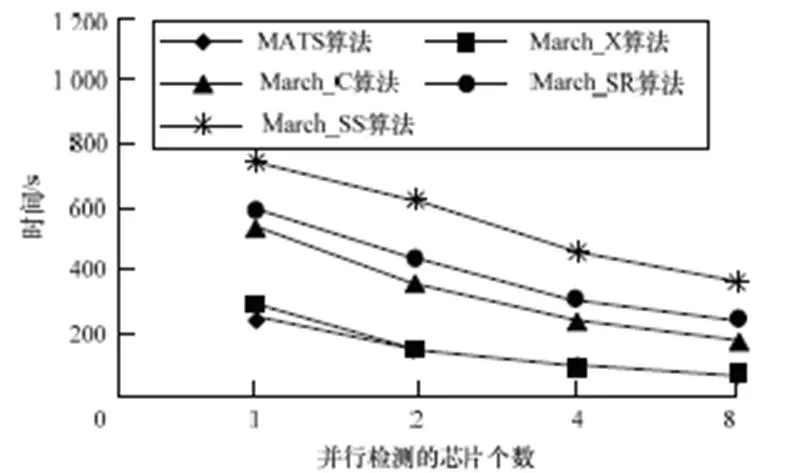

实验对每一种算法分别采用1-chip、2-chips、4-chips和8-chips检测200 MB内存所用的时间。其中,这200 MB位于同一个LMC管理下的同一个物理bank。在DDR2内部,这200 MB分别来自8个内存芯片,每个芯片25 MB。

图7是1-chip、2-chips、4-chips和8-chips的检测时间比较折线图。无论是简单算法还是复杂算法,从一个芯片到并行检测8个芯片,内存的检测时间几乎是成线性递减的。得出结论:对于芯片级并行,访存带宽越大并行效果越好。

图7 芯片检测时间比较

4.2 访存控制器级并行

可以利用个访存控制器同时并行检测个DDR2内存条。实验对各个算法分别采用1-LMC和2-LMC检测200 MB内存的时间。其中,对于1-LMC,这200 MB位于同一个LMC(可以使LMC0或者LMC1)管理下的同一个物理bank。在DDR2内部,这200 MB分别来自8个内存芯片(每个芯片25 MB);对于2-LMC,这200 MB内存位于2个LMC(即LMC0和LMC1),每个LMC管理100 MB。

图8是各算法采用1-LMC和2-LMC的检测时间柱状比较,一次访存操作的内存位数分别为8位、16位、32位和64位。1-LMC表示200 MB内存位于同一个LMC管理下的同一个物理bank中的8个内存芯片,2-LMC表示 200 MB内存位于2个LMC,每个LMC管理100 MB。

图8 各算法检测时间比较

无论是简单算法还是复杂算法,从1个LMC到2个LMC,内存检测时间几乎减少了一倍。得出结论:对于访存控制器级并行,访存控制器数量越多并行效果越好。

4.3 结合芯片级并行和访存控制器级并行

4.1节和4.2节的实验表明,芯片级并行和访存控制器级并行都可以有效加速内存检测,如果把它们结合起来会达到更好的效果。根据图9可知,对于任意算法都是64位的2-LMC检测时间最少。2种方法结合会更有效地加快内存检测速度。但是,在检测同样大小的内存时,访存控制器级并行必须把内存分配到2个或更多的LMC上。

图9 芯片级并行和访存控制器级并行的比较

5 结束语

本文提出一种结合硬件特征的并行内存故障检测方案,该方案是根据DDR2和访存控制器的工作原理而设计的,从2个方面加快内存检测速度,一个是芯片级并行,另一个是访存控制器级并行。对于芯片级并行,访存带宽越大并行效果越好,从一个芯片到并行检测8个芯片,内存的检测时间几乎是呈线性递减的。对于访存控制器级并行,访存控制器数量越多并行效果越好,从1个LMC到 2个LMC,内存的检测时间几乎减少了一倍。若结合使用2种方法会得到更好的加速效果,但是,在检测同样大小的内存时,访存控制器级并行必须把内存分配到2个或更多的LMC上。

[1] 任爱玲, 凌 明, 吴光林, 等. 一种用于嵌入式内存测试的高效诊断算法[J]. 应用科学学报, 2005, 23(2): 178-182.

[2] 石 磊, 王小力. 一种基于存储器故障原语的March测试算法研究[J]. 微电子学, 2009, 39(2): 251-255.

[3] Hamdioui S, Al-Ars Z, Goor A J. Testing Static and Dynamic Faults in Random Access Memories[C]//Proc. of the 20th IEEE VLSI Test Symposium. [S. l.]: IEEE Press, 2002: 395-400.

[4] Irobi S, Al-Ars Z, Hamdioui S. Detecting Memory Faults in the Presence of Bit Line Coupling in SRAM Devices[C]//Proc. of IEEE International Test Conference. Austin, USA: IEEE Press, 2010: 1-10.

[5] Hamdioui S, Al-Ars Z, Goor A J, et al. Linked Faults in Random Access Memories: Concept, Fault Models, Test Algorithms, and Industrial Results[J]. Computer-aided Design of Integrated Circuits and Systems, 2004, 23(5): 737-757.

[6] Hamdioui S, Goor A J, Rogers M. March SS: A Test for All Static Simple RAM Faults[C]//Proc. of IEEE International Workshop on Memory Technology, Design and Testing. [S. l.]: IEEE Press, 2002: 95-100.

[7] Al-Harbi S M, Noor F, Al-Turjman F M. March DSS: A New Diagnostic March Test for All Memory Simple Static Faults[J]. IEEE Trans. on Computer-aided Design of Integrated Circuits and Systems, 2007, 26(9): 1713-1720.

[8] Bosio A, Carlo S D, Natale G D, et al. March AB, A State- of-the-art March Test for Realistic Static Linked Faults and Dynamic Faults in SRAMs[J]. Computers & Digital Techniques, 2007, 1(3): 237-245.

[9] Harutunvan G, Vardanian V A,Zorian Y. Minimal March Tests for Unlinked Static Faults in Random Access Memories[C]// Proc. of the 23rd IEEE VLSI Test Symposium. [S. l.] IEEE Press, 2005: 53-59.

[10] 高 剑. 存储器并行测试方法[J]. 电子测试, 2009, (2): 47-49.

[11] 吴光林, 胡 晨, 李 锐, 等. 一种并行内建自测试嵌入式SRAM方案[J]. 电路与系统学报, 2003, 10(8): 51-56.

[12] Sharma A. 先进半导体存储器——结构, 设计与应用[M]. 曹 莹, 孙 磊, 伍 冬, 等, 译. 北京: 电子工业出版社, 2005.

[13] Cavium Networks. Cavium Networks OCTEON Plus CN54/ 5/6/7XX Hardware Reference Manual[Z]. 2009.

[14] Benso A, Member S, Bosio A. March Test Generation Revealed[J]. IEEE Trans. on Computers, 2008, 57(12): 1704- 1713.

编辑 顾逸斐

A Parallel Memory Fault Detection Scheme Combined with Hardware Characteristic

HU Die1, WU Jun-min1,2

(1. School of Computer Science and Technology, University of Science and Technology of China, Hefei 230027, China; 2. Suzhou Institute for Advanced Study, University of Science and Technology of China, Suzhou 215123, China)

March algorithms are designed very complex, and they are designed to be used to test memory chips, does not apply to the user. In order to solve above problems, this paper presents a parallel memory test method which utilizes the hardware features. It includes two parallel methods: one is chips-level parallel method which is designed according to the working principle of DDR2, and it can detect several memory chips. The other is Local Memory Controller(LMC)-level parallel method which is designed according to the working principle of memory controller, and it can detect several DDR2 memories. For chips-level parallel method, if more chips can be tested, the test time is faster. From testing one chip to eight chips, the test time is almost linearly decreasing. For LMC-level method, if there are more LMCs, the time is faster. From one LMC to two LMCs, the test time is reduced by almost doubled. Experimental results show that this method can greatly reduce the test time of the two algorithms, while still allow users to test memory.

fault model; March algorithm; DDR2 memory bank; chips-level parallel; memory controller level parallel

1000-3428(2014)03-0310-05

A

TP306

国家自然科学基金资助项目(61272132);中央高校基本科研业务费专项基金资助项目(WK0110000020);中国科学院计算技术研究所国家重点实验室开放基金资助项目(CARCH201204)。

胡 蝶(1987-),女,硕士研究生,主研方向:计算机内存测试技术;吴俊敏,副教授。

2012-12-19

2013-02-27 E-mail:hudie@mail.ustc.edu.cn

10.3969/j.issn.1000-3428.2014.03.066