基于FPGA平台的Piccolo功耗分析安全性评估

2014-05-22王晨旭李景虎喻明艳王进祥

王晨旭 李景虎 喻明艳 王进祥

基于FPGA平台的Piccolo功耗分析安全性评估

王晨旭*①②李景虎②喻明艳①②王进祥①

①(哈尔滨工业大学微电子中心 哈尔滨 150001)②(哈尔滨工业大学(威海)微电子中心 威海 264209)

为了评估Piccolo密码算法的功耗分析安全性,该文提出一种针对Piccolo末轮的攻击模型,基于SASEBO (Side-channel Attack Standard Evaluation BOard)实测功耗数据对该算法进行了相关性功耗分析攻击。针对Piccolo末轮运算中包含白化密钥的特点,将末轮攻击密钥(包括轮密钥24L,24R,2,3)分成4段子密钥,逐个完成各个子密钥的攻击,使80位种子密钥的搜索空间从280降低到(2×220+2×212+216),使种子密钥的恢复成为可能。攻击结果表明,在实测功耗数据情况下,3000条功耗曲线即可恢复80位种子密钥,证实了该攻击模型的有效性和Piccolo硬件面向功耗分析的脆弱性,研究并采取切实有效的防护措施势在必行。

密码学;数据安全;Piccolo;相关性功耗分析;攻击模型;防护措施;侧信道攻击标准评估板

1 引言

密码算法是数据安全的基础,近年来,在无线传感器网络(WSN)和射频识别(RFID)应用中,资源消耗和数据安全这对矛盾体的出现给传统加密算法带来了新的挑战,占用资源少、功耗低的轻量级分组密码算法应运而生。其中,CLEFIA[1]和PRESENT[2,3]是两种最典型的轻量级密码算法,并已于2012年成为ISO标准;在CHES2011会议上,索尼公司继CLEFIA之后提出了更加紧凑的轻量级分组密码算法Piccolo,该算法在0.13 μm工艺下只需683个等效门(Gate Equivalents, GE)即可实现加密操作[4]。文献[5]对近年来出现的轻量级密码算法进行了硬件资源评估,指出Piccolo算法在所有测评的分组密码算法中占用最小的硬件资源,尤其适合在资源受限的环境中,为目前稍显尴尬的RFID加密应用提供了一种可行的解决方案。

本文第2节简要介绍了本文所采用的一些符号标记,描述了Piccolo算法;第3节介绍CPA攻击的基本原理;第4节则描述了Piccolo功耗攻击模型和猜测功耗矩阵的建立方法;第5节给出了实验配置和部分攻击结果,并对结果进行了简要讨论;最后给出了本文的结论和下一步工作展望。

2 Piccolo算法简介

Piccolo分组密码算法的分组长度为64 bit,支持80 bit和128 bit两种密钥长度,分别用Piccolo-80和Piccolo-128表示,对应的迭代轮数分别为25轮和31轮。本文以Piccolo-80为研究对象,为方便解释,下文在无特殊说明的情况下,Piccolo均指Piccolo-80。以下首先给出本文所用符号标记的含义,而后对算法做简要介绍。

2.1 符号标记含义说明

2.2 密钥扩展部分

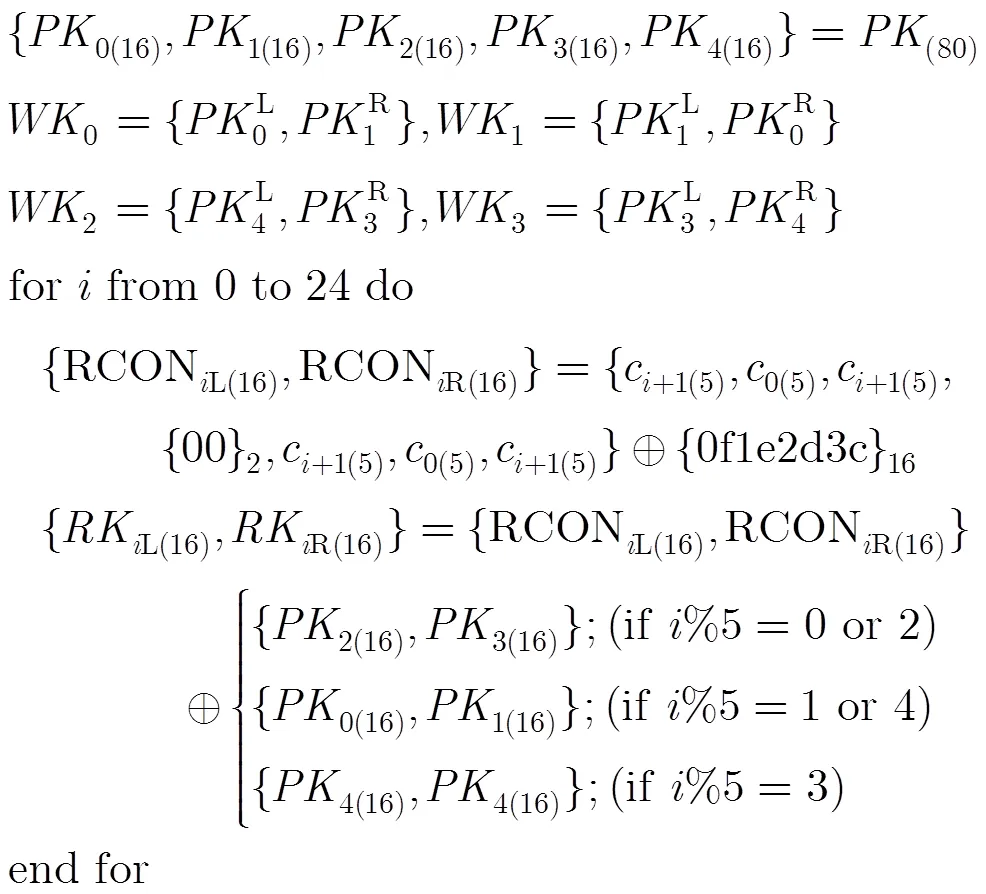

式中,RCONL和RCONR分别表示第轮的轮常数的左半部分和右半部分,c为的5 bit二进制表示,例如22={10110}2。

由上述过程不难看出,最后一轮中所涉及的白化密钥2和3对应于种子密钥中的3,4,轮密钥24L和24R与中的0,1则只是相差一个轮常数RCON24L和RCON24R。因此,如果能够获取2,3,24L和24R,则能够通过其它方式破解2以获得Piccolo的所有80 bit种子密钥。

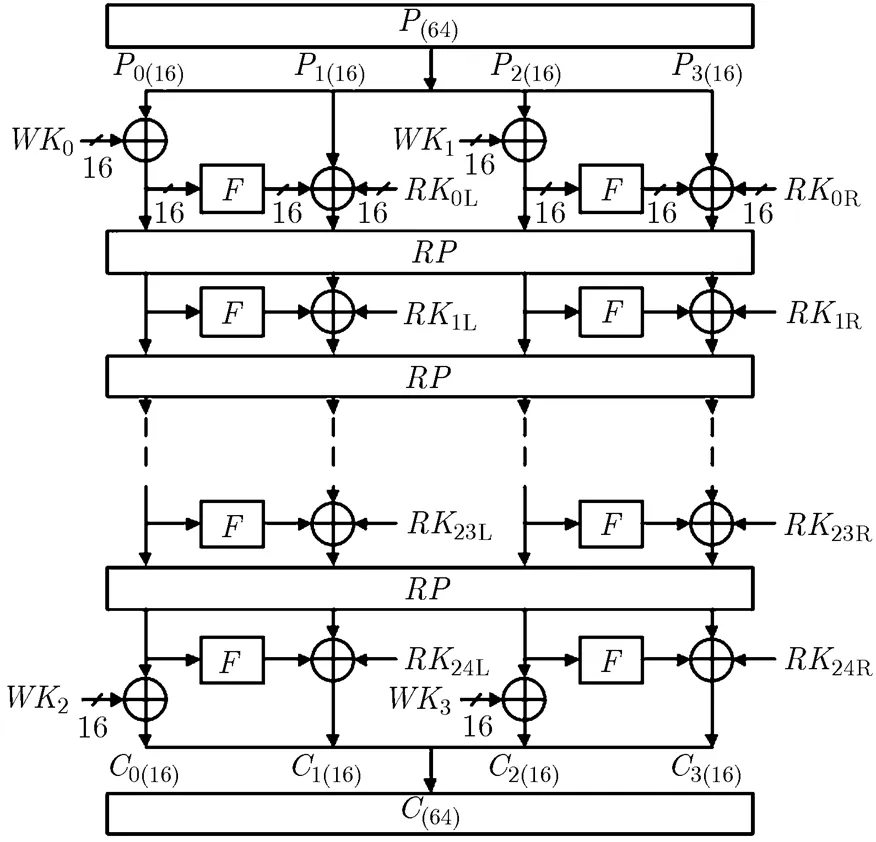

2.3 数据处理部分

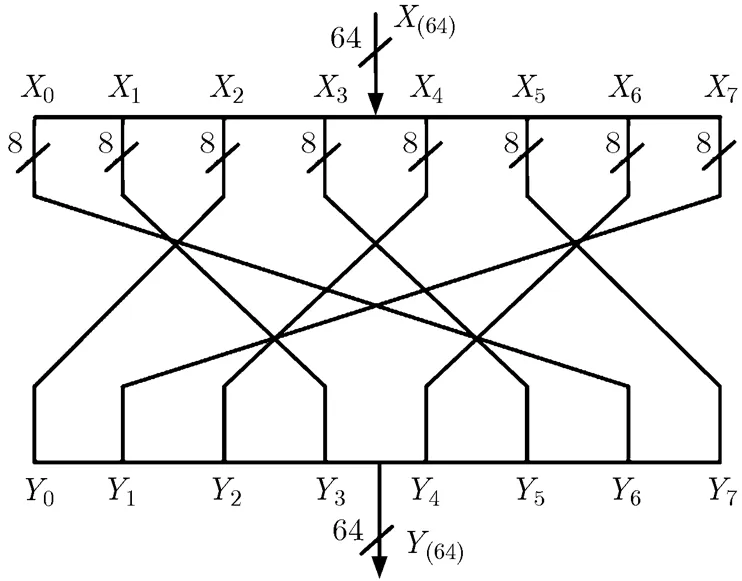

Piccolo算法采用广义Feistel结构,数据处理部分以64 bit明文、白化密钥和轮密钥为输入经由25轮迭代后产生64 bit密文输出,如图1所示,从图中可以看出,除最后一轮外,每轮包含两类变换,分别是函数: GF(216)→GF(216)和轮置换: GF(264)→GF(264),最后一轮不包含轮置换。

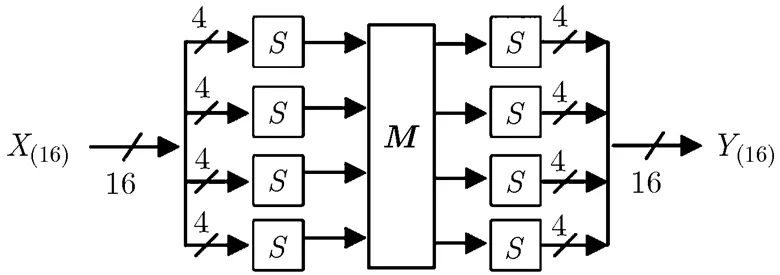

函数: Piccolo的: GF(216)→GF(216)也被称为超级S盒[16],采用3层结构,具有更强的混淆能力,如图2所示。图中,S盒: GF(24)→GF(24) 是Piccolo中唯一的非线性操作;代表混淆矩阵,矩阵的引入使输入的每一位扩散影响输出的每一位,后文将能看到这一点会增加功耗分析攻击的难度。

图1 Piccolo密码算法数据处理流程

图2 Piccolo密码算法的F函数

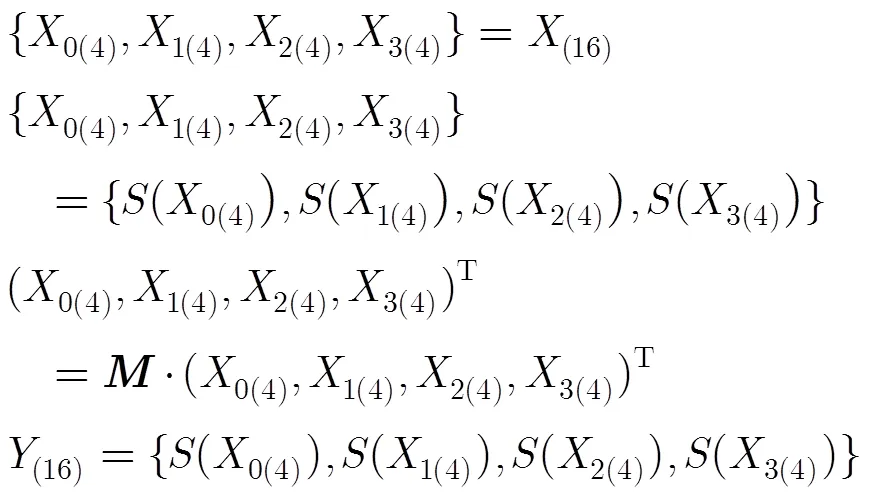

上述关系可以用如下过程进行表示。

轮置换:: GF(264)→GF(264)以字节为单位进行置换,其过程如图3所示。

3 CPA攻击的基本原理

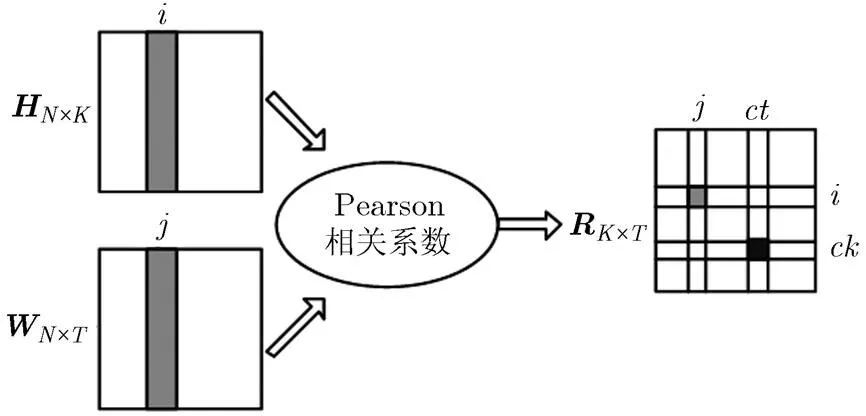

在一个典型的同步时序电路中,一个时钟周期内(两个上升沿之间)触发器保持稳定,整个电路的功耗主要是由组合电路翻转带来的动态功耗;当上升沿到来后的极短一段时间内,各触发器状态更新,整个电路的功耗则由触发器的翻转引起的动态功耗组成,其值必定与触发器的翻转个数(以汉明距离予以表示)相关。由此可知,加密过程中密码芯片所产生的功耗必然与运算期间某些中间值存在一定的相关性。CPA攻击方法的主要思想就是通过分析这种相关性达到破解算法密钥的目的,一般情况下,这种相关性比较小,因此需要大量的加密获取不同情况下的功耗数据,结合统计分析技术才能够成功破解密钥。在统计学理论中,通常用Pearson相关系数来评价两个向量和之间的相关性[6]。

图3 Piccolo密码算法的RP置换过程

下面以密文攻击(以最后轮的轮密钥为攻击目标)为研究对象,描述密文CPA攻击一般步骤:

图4 CPA的统计分析过程

4 Piccolo算法的CPA攻击

4.1 Piccolo的硬件实现

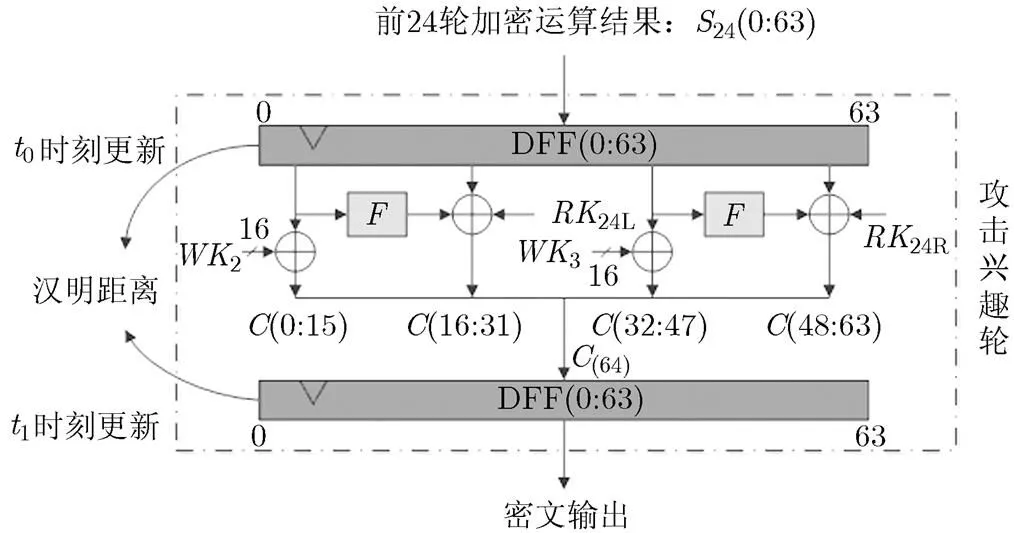

Piccolo算法的ASIC硬件实现方式主要有两种,一是基于轮的并行实现方法,它可以得到较高的数据吞吐率,但消耗的硬件资源较多。二是将输入数据进行分组,每组分别处理,再予以拼接,即串行实现方法,这种方法能够显著地减小硬件资源消耗,683GE即可实现[4]。本文评估了第1种实现方法的安全性,对串行实现方式的评测也可以采用类似方法。并行实现方式对输入64 bit明文数据并行处理,每轮的处理结果保存在64个触发器中(本文以DFF(0:63)表示,并用DFF(0)表示这些触发器的最高有效位),历经25轮运算后输出64 bit密文。本文所完成的Piccolo设计占用1624GE, 26个时钟周期能完成一个分组的加密。

4.2 攻击模型

通常情况下,密文攻击相对于明文攻击更加实用,因此,后文主要以密文攻击为说明对象来评测Piccolo算法的实现安全性,即以获取最后轮的轮密钥24L,24R和白化密钥2,3(为解释方便,下文将2,3,24L和24R统称为攻击密钥)为攻击目标。虽然Piccolo算法采用了类似DES算法的Feistel结构,但是由于超级S盒和白化密钥的存在,Piccolo的CPA攻击与传统密码算法如DES, AES和PRESENT相比存在较大难度。

图5 Piccolo算法并行实现方式最后一轮抽象图

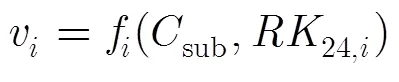

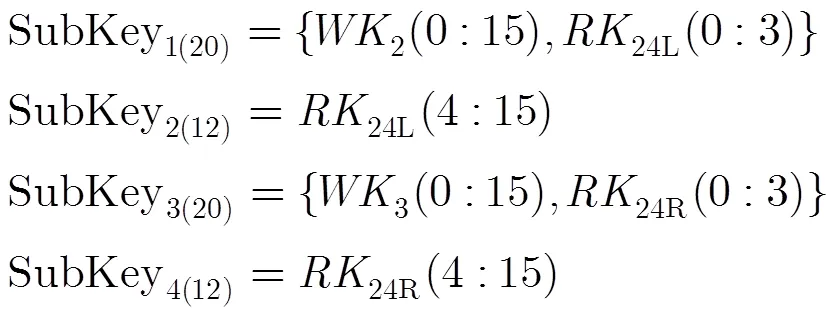

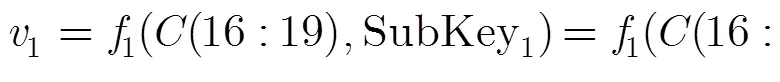

根据部分相关性原理,如果一个电路结构的整体和电路的功耗具有相关性,电路结构的一部分也和电路的功耗具有一定的相关性,因此,部分触发器的翻转对总功耗也会产生一定的影响,为方便计算,考虑基于DFF(0:63)中的部分触发器的汉明距离进行功耗建模,将2,3,24L,24R按下式进行拆分组合为SubKey1(20), SubKey2(12), SubKey3(20)和SubKey4(12)4段子密钥。

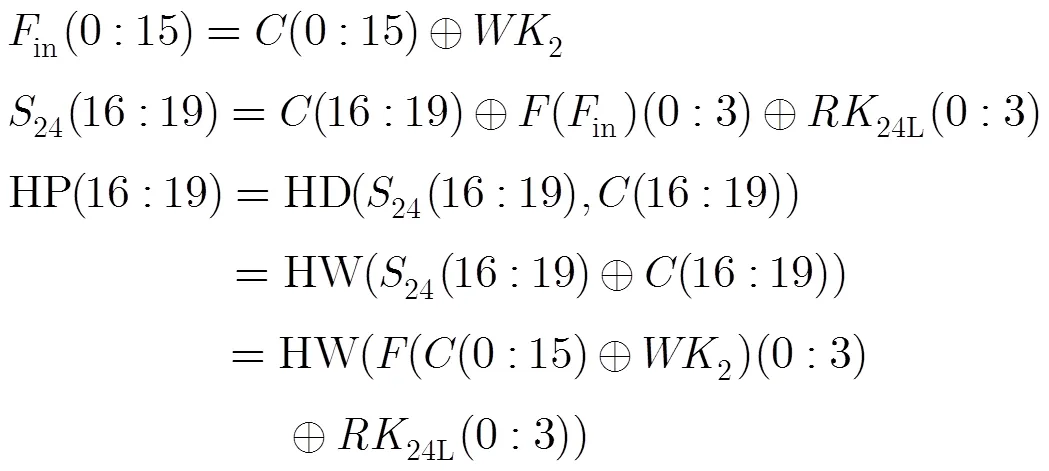

式中in(0:15)表示函数的输入;HP(16:19)表示基于DFF(16:19)的功耗模型值。

根据上述模型,对于某个特定的64 bit明文,通过对SubKey1(20)的220次遍历可以得到一个关于HP(16:19)的1×220的汉明距离矩阵,这个矩阵代表了在不同的SubKey1(20)猜测下,触发器翻转时刻的猜测的功耗信息。如果对条明文进行计算,则可以得到一个×220的矩阵,这个矩阵即为我们攻击SubKey1(20)所需的猜测功耗矩阵1,该矩阵用来与实际功耗矩阵做统计分析。

根据上述模型,通过条不同的明文和对SubKey2(12)进行遍历可以得到一个关于HP(20:31)的×220的猜测功耗矩阵2,该矩阵用来与实际功耗矩阵做统计分析以攻击24L(4:15)。

4.2.3针对SubKey3(20)和SubKey4(12)的功耗建模

由于Piccolo算法左右两侧的高度对称性,对SubKey3(20)和SubKey4(12)的攻击方法与SubKey1(20)和SubKey2(12)基本一致,所不同的是这里需要分别选取24(36:39)和24(40:31)为中间值进行功耗映射。

5 攻击实验配置与攻击结果

5.1 攻击实验配置

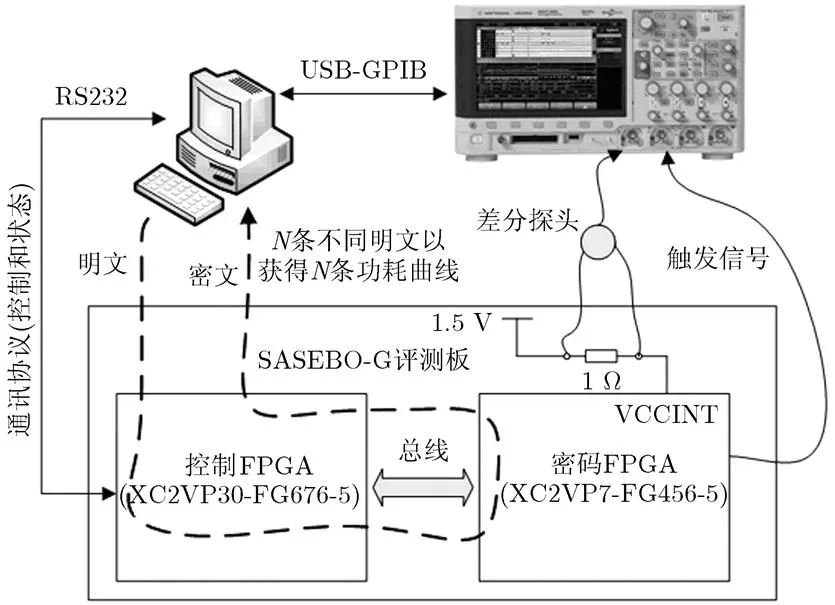

SASEBO(Side-channel Attack Standard Evaluation BOard)系列板是用于评测抗侧信道攻击能力的基准平台[18],由日本AIST信息安全研究中心开发。本文采用SASEBO-G[19]作为基准搭建了如图6所示的功耗采集平台,其中,PC机采用目前主流计算机,PC机与SASEBO-G通过RS-232相连,并通过GPIB适配器控制示波器(Agilent MSO8064A)的行为。示波器的通道2采用普通单端探头用于接收SASEBO-G板上的触发信号,通道1采用差分探头用于探测SASEBO-G板上密码FPGA芯片的电流变化。

图6 功耗采集平台硬件原理图

基于图6的功耗采集解决方案如下:首先制订PC机与下位机(SASEBO-G)之间的通讯协议;在SASEBO-G评测板上,Piccolo算法实现在密码FPGA芯片内,控制FPGA主要完成上述通讯协议的解析和密码FPGA的控制;在PC机上用NI公司的LabVIEW®实现流程控制,LabVIEW产生64 bit的随机明文,通过RS232经由控制FPGA发送到密码FPGA芯片中进行Piccolo加密,期间密码FPGA芯片向示波器产生一个触发信号,保证每次Piccolo加密时示波器采集的数据都能准确对齐;控制FPGA等待加密结束,将存储在密码FPGA中的密文读出并经由RS232送往PC机;LabVIEW负责接收并存储密文,然后向示波器发出指令以存储此次采集到的数据,一条功耗曲线采集完毕。

为了达到上述要求并方便控制,我们在实现Piccolo密码算法时加入了局部总线接口和可编程寄存器,并在控制FPGA中实现了一个基于ARM7的最小SoC系统,采用固件实现与PC机的通讯和协议解析,此最小系统中仅仅包括ARM7核,UART和一个用于与密码FPGA芯片通讯的局部总线控制器。

实验中,最小SoC系统运行于24 MHz,而Piccolo密码算法运行于4 MHz,波特率设定为115200;设定5000组明文输入,示波器采样率为2 GSa/s,由于触发信号保证了每次Piccolo加密时示波器采集的数据都能准确对齐,为了降低测量噪声,将示波器设置为20次平均采样模式,即每组明文重复执行加密过程20次,由示波器将20次采集到的数据自动平均,因此,Piccolo实际执行加密的次数为5000×20。

5.2 采用3000条功耗曲线时的攻击结果

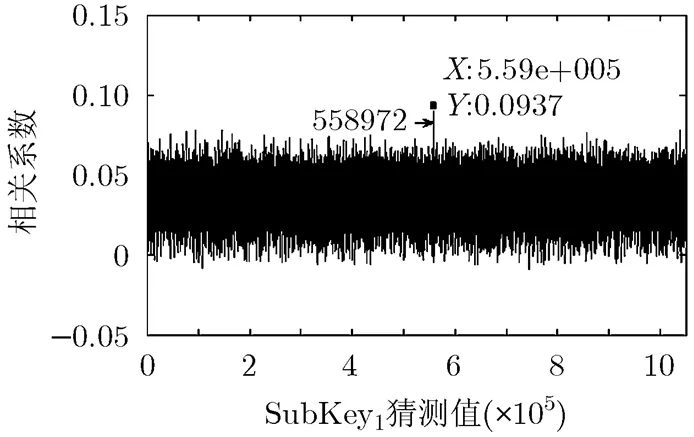

由于对SubKey1和SubKey2与对SubKey3和SubKey4的攻击过程基本一致,因此这里仅仅给出对前两个子密钥的攻击结果。实验中,Piccolo加密时的种子密钥取{00112233445566778899}16,在3000条功耗曲线时,计算1矩阵与矩阵的相关系数矩阵1,取相关系数矩阵1各行的最大值,这些最大值可以构成一个220×1的向量,该向量结果见图7,图中横坐标表示密钥猜测值,纵坐标表示了相应的相关系数。

由图7可以发现,当= {558972}10={8877c}16时,相关系数达到最大值0.0937,这说明在本次攻击中{8877c}16={1000_1000_0111_0111_1100}2最有可能是SubKey1的真实值,由此可推出2的攻击密钥值为{1000_1000_0111_0111}2,而24L(0:3)的攻击密钥值为{1100}2,事实上,2和24L(0:3)的真实密钥值也的确如此。

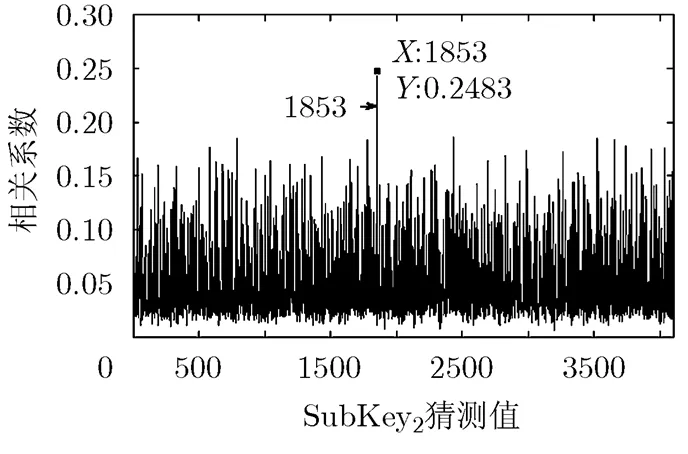

图8给出了在3000条功耗曲线时对SubKey2的攻击结果,在

={1853}10={73d}16={0111_0011 _1101}2

时获得了最大的相关系数0.2483,即24L(4:15)的攻击密钥值为{0111_0011_1101}2。综上,使用3000条功耗曲线对Piccolo进行密文CPA攻击后,得到24L={c73d}16,2={8877}16,这些结果与预期值相同,表明攻击成功。

5.3 安全性评估方法与结果

5.4 讨论

5.4.1相关度 根据上述讨论,在1时刻,实际Piccolo硬件的功耗可近似用DFF (0:63)全部64个触发器的动态功耗表征;但是,在攻击模型建立时,SubKey1依赖于DFF(16:19)共4个触发器,而SubKey2则有赖于DFF(20:31)共12个触发器,因此,攻击SubKey2时用到的功耗模型更加接近于真实情况。这造成了在成功攻击SubKey2时的相关系数(0.2483,见图8)比攻击SubKey1时的相关系数(0.0937,见图7)要高。

事实上,实验中攻击SubKey1的MTD1为3000条,而在成功攻击SubKey2时的MTD2只需要1750条,MTD2远小于MTD1主要是因为针对SubKey2的功耗模型信噪比更高,与实际功耗具有更高的相关度。

5.4.2种子密钥的恢复 通过CPA攻击实验,我们已成功获取2,3,24L和24R,依据轮密钥扩展算法可以容易恢复出Piccolo的0,1,3和4。为了获取完整的80 bit,还需单独针对2进行攻击,如果使用最简单的方式穷举破解2,那么采用本文提议的CPA攻击方法所需要的完整密钥搜索空间为(2×220+2×212+216)。

6 结束语

本文提出了一种密文CPA攻击模型,基于SASEBO平台和实测结果首次评估了Piccolo面向功耗分析攻击的安全性。攻击结果表明,基于此攻击模型在实测功耗数据的情况下,只需3000条功耗曲线即可完全恢复出Piccolo算法的80 bit种子密钥,因此在Piccolo的硬件实现中引入相应的抗功耗分析攻击措施是不可忽略的。虽然本文只是成功实施了密文攻击,容易使用相似的方法实现明文攻击,相形之下,由于首轮运算中包含了函数,所以明文攻击要比密文攻击稍显复杂。

图7 3000条功耗样本时对SubKey1的攻击结果

图8 3000条功耗样本时对SubKey2的攻击结果

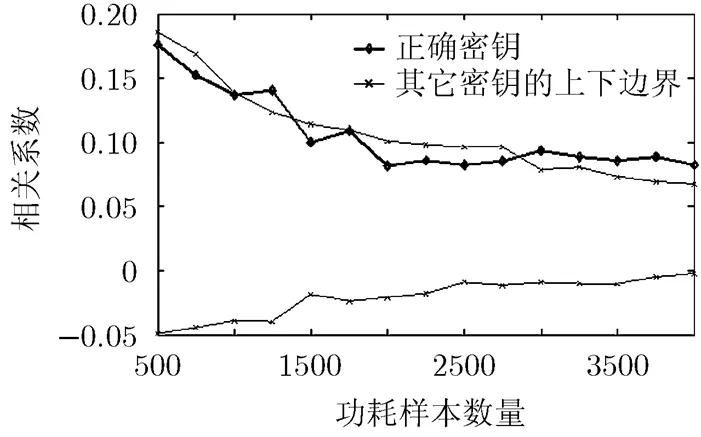

图9 SubKey1猜测值相关系数与功耗样本数量的关系

在本文提出的CPA攻击方法中,为获取80 bit种子密钥共需要(2×220+2×212+216)次遍历运算,这虽然是可能的,但其时间和空间复杂度都比较大,因此探究降低遍历计算复杂度的方法并研究适用于轻量级分组密码算法的抗功耗分析攻击措施将是下一步的研究重点。

[1] ISO/IEC 29192-2-b:2012. CLEFIA: a lightweight block cipher with a block size of 128 bits and a key size of 128, 192 or 256 bits[S]. 2012.

[2] ISO/IEC 29192-2-a:2012. PRESENT: a lightweight block cipher with a block size of 64 bits and a key size of 80 or 128 bits[S]. 2012.

[3] Bogdanov A, Knudsen L R, Leander G,.. PRESENT: an ultra-lightweight block cipher[C]. Proceedings of the 9th International Workshop on Cryptographic Hardware and Embedded Systems(CHES2007), Vienna, Austria, 2007: 450-466.

[4] Shibutani K,.. Piccolo: an ultra-lightweight blockcipher [C]. Proceedings of the 13th International Workshop on Cryptographic Hardware and Embedded Systems (CHES2011), Nara, Japan, 2011: 342-357.

[5] Kumar A and Aggarwal A. Lightweight cryptographic primitives for mobile Ad hoc networks[C]. Proceedings of 2012 International Conference on Security in Computer Networks and Distributed Systems(SNDS2012), Trivandrum, India, 2012: 240-251.

[6] Brier E, Clavier C, and Olivier F. Correlation power analysis with a leakage model[C]. Proceedings of the 6th International Workshop on Cryptographic Hardware and Embedded Systems(CHES2004), Boston, USA, 2004: 135-152.

[7] Liu H Y, Qian G Y, Satoshi Goto,. Correlation power analysis based on switching glitch model[C]. Proceedings of the 7th Web Information Systems and Applications Conference(WISA2010), Huhehot, China, 2010, 6513: 191-205.

[8] Li H Y, Wu K K, and Yu F Q. Enhanced correlation power analysis attack against trusted systems[J]., 2011, (4): 3-10.

[9] Breier J and Kleja M. On practical results of the differential power analysis[J]., 2012, 63(2): 125-129.

[10] 乌力吉, 李贺鑫, 任燕婷, 等. 智能卡功耗分析平台设计与实现[J]. 清华大学学报(自然科学版), 2012, 52(10): 1409-1414.

Wu Li-ji, Li He-xin, and Ren Yan-ting,.. Smart card power analysis platform design and implementation[J].(&), 2012, 52(10): 1409-1414.

[11] Oswald D and Paar C. Breaking Mifare DESFire MF3ICD40: power analysis and templates in the real world[C]. Proceedings of the 13th International Workshop on Cryptographic Hardware and Embedded Systems (CHES2011), Nara, Japan, 2011: 207-222.

[12] Moradi A, Barenghi A, Kasper T,.. On the vulnerability of FPGA bitstream encryption against power analysis attacks[C]. Proceedings of the 18th ACM Conference on Computer and Communications Security(CCS2011), Chicago, USA, 2011: 111-123.

[13] 赵光耀, 李瑞林, 孙兵, 等. Piccolo算法的差分故障分析[J]. 计算机学报, 2012, 35(9): 1918-1925.

Zhao Guang-yao, Li Rui-lin, Sun Bing,.. Differential fault analysis on Piccolo[J]., 2012, 35(9): 1918-1925.

[14] Jeong K. Differential fault analysis on block cipher Piccolo[OL]. http://eprint.iacr.org/2012/399.pdf. 2012.6.

[15] Li S, Gu D W, Ma Z Q,. Fault analysis of the Piccolo block cipher[C]. Proceedings of the 8th International Conference on Computational Intelligence and Security (CIS2012), Guangzhou, China, 2012: 482-486.

[16] Daemen J and Rijmen V. Understanding two-round differentials in AES[C]. Proceedings of the 5th International Conference on Security and Cryptography for Networks (SCN2006), Maiori, Italy, 2006: 78-94.

[17] 刘鸣, 陈弘毅, 白国强. 功耗分析研究平台及其应用[J]. 微电子学与计算机, 2005, 22(7): 134-138.

Liu Ming, Chen Hong-yi, and Bai Guo-qiang. Power analysis research platform and its applications[J].&, 2005, 22(7): 134-138.

[18] 汪鹏君, 张跃军, 张学龙. 防御差分功耗分析攻击技术研究[J]. 电子与信息学报, 2012, 34(11): 2774-2784.

Wang Peng-jun, Zhang Yue-jun, and Zhang Xue-long. Research of differential power analysis countermeasures[J].&, 2012, 34(11): 2774-2784.

[19] AIST of Japan. SASEBO-G Specification[OL]. http://www. risec.aist.go.jp/project/sasebo. 2012.6.

[20] Kim C K, Schläffer M, and Moon S J. Differential side channel analysis attacks on FPGA implementations of ARIA [J]., 2008, 30(2): 315-325.

王晨旭: 男,1977年生,讲师,研究方向为芯片与信息安全.

李景虎: 男,1975年生,讲师,研究方向为数模混合技术.

喻明艳: 男,1965年生,教授,研究方向为计算机体系结构.

王进祥: 男,1968年生,教授,研究方向为SoC的可靠性设计.

Power Analysis Security Evaluation on Piccolo Based on FPGA Platform

Wang Chen-xu①②Li Jing-hu②Yu Ming-yan①②Wang Jin-xiang①

①(,,150001,)②(,,264209,)

To evaluate Piccolo’s security against Power Analysis Attack (PAA), a cipher text attack model is proposed and Correlation Power Analysis (CPA) is conducted on this cipher implementation with measured power traces based on Side-channel Attack Standard Evaluation BOard (SASEBO). Due to the whiten keys for the final round of Piccolo, attacked keys including24L,24R,2and3are divided into four sub-keys, which are disclosed one by one. This approach can reduce the 80-bit primary key search space from 280to (2×220+2×212+216) and make it possible to recover the primary key. The attack results show that 3000 measured power traces are enough to recover Piccolo’s 80-bit primary key, which proves the attack model’s feasibility and Piccolo’s vulnerability to CPA against its hardware implementation. So, some countermeasures should be used for Piccolo’s hardware implementation.

Cryptography; Data security; Piccolo; Correlation Power Analysis (CPA); Attack model; Countermeasure; Side-channel Attack Standard Evaluation BOard (SASEBO)

TP309.2

A

1009-5896(2014)01-0101-07

10.3724/SP.J.1146.2013.00193

2013-02-06收到,2013-07-02改回

国家自然科学基金(60973162)资助课题

王晨旭 wangchenxu@hit.edu.cn