基于DS18B20的小环境测温控制的FPGA实现

2014-05-12王春玲王美红宁崇森薛长忠

王春玲,王美红,宁崇森,薛长忠

(泰山学院物理与电子工程学院,山东泰安 271021)

1 引言

温度是最常见的测量和控制对象.常规温度测控系统一般采用热电阻、热电偶等传感器元件,输出信号是模拟信号,需要经过A/D转换、放大等信号处理后,送入单片机、DSP等微控制器中进行相应数据处理,并通过软件设计实现针对控制对象特征的控制算法,再经D/A转换后输出温度控制驱动信号,实现温度控制.这种温度测控系统结构的缺陷,首先是硬件组成元件较多,成本较高;其次,信号在处理过程中抗干扰能力较差,容易失真,造成测控精度偏低;第三,针对不同控制对象,在元器件选用、算法设计上都需要单独进行,设计通用性差,难以在线升级.在我们设计的小环境温控系统中,我们采用并使用FPGA器件替代单片机进行控制,大大简化了外围电路的设计,同时保证了测量的准确性,便于功能扩展和升级.本文主要阐述FPGA+DS18B20的测温控制设计实现方法.

2 系统方案设计

小环境温控系统面向便携式设备需要进行设计,采用直流开关电源和热电制冷器件实现恒温控制,控制要求较复杂,对精度和速度要求较高,用户要求功能可裁剪和升级.为此,我们利用FPGA器件集成度高、体系结构和逻辑单元丰富、灵活、系统功能和结构可重构等特点,选取了Altera公司高性价比的飓风系列FPGA器件Cyclone EP1C6,其工作电压为3.3V,内核电压1.5V,内嵌两个锁相环电路,工作频率高达200MHz,以简化设计,降低成本,并可实现软件移植和设计升级.

由于空间狭小,温度场均匀,选用一只DS18B20测温即可[1].DS18B20是美国DALLAS公司生产的单线数字温度传感器,价格低廉,体积小.其与控制器之间通信只需一根数据线,测量温度范围为-55℃到125℃,精度为±0.5℃.与传统温度传感器不同的是,它的温度转换精度9-12位可编程,直接将温度转换值以二进制码的方式串行输出;同时,芯片内部将模拟信号转换为12位数字量的时间最大为750ms,对于一般温控系统,完全可以满足实时性需要.

相应的硬件电路方案如图1所示,DS18B20的三个引脚中,引脚VDD通过滤波电容接3.3V TTL电平,对传感器供电.引脚DQ是数据传输线,即一线总线,FPGA通过该引脚控制DS18B20采集温度.通过一个4.7KΩ的上拉电阻,使得数据线在空闲状态下能自动上拉为高电平.GND为公共地.

图1 DS18B20与FPGA的连接电路图

3 DS18B20的功能特征及FPGA控制方案

3.1 DS18B20的功能特征分析

DS18B20作为单总线数字测温器件,其硬件连接简单,相对地控制过程比较复杂,时序要求非常严格.通过对DS18B20功能的分析可知,单片DS18B20的工作流程相对多片系统可以适当简化,其工作流程如图2所示.

图2 单片DS18B20的工作控制流程示意图

由图2可见,DS18B20的工作流程具有显著的顺序控制和循环工作特点;一个完整的工作周期分为温度检测转换和数据传输两大阶段;两个阶段均以初始化开始,并通过主(控)设备(此处是FPGA)向其(从设备)发送ROM命令和功能命令,实现其工作循环.

ROM命令和功能命令均为字节型命令.在只有一片DS18B20的情况下,ROM命令只有一个,即跳过ROM命令(SKIP ROM,代码是CCH),其功能是使主设备判断该芯片存在并可以工作.功能命令包括温度转换指令(CONVERT CMD,代码是44H)和读暂存器指令(READ RESULT,代码是4EH),分别用于启动温度转换和读取DS18B20暂存的温度数据.

由于DS18B20的单线通信特征,所有操作必须分时完成,时隙(Time slot,即完成一位传输所用的时间)是其操作时序的重要特征和基本时间单位.主要操作时隙包括初始化、应答、主机写0、主机写1、主机读0、主机读1等.除应答时隙外,所有时隙都由主设备发出同步信号,并且发送所有的命令和数据都是字节的低位在前(这一点与多数串行通信一般字节高位在前的格式是不同的).两个时隙之间最小的时间间隔是1μs.

图3 为DS18B20的读写时隙

对DS18B20进行读操作时,FPGA先将数据线从高电平拉至低电平,进入读时间隙.FPGA保持低电平1μs以上,然后释放总线.在读时隙的下降沿后15μs之内,DS18B20会将数据送到总线上.FPGA必须在这15μs之内完成读数.在读取数据结束时,I/O引脚应拉回到高电平.对于主设备master而言,无论读入数据是1还是0,其本身的操作及时序相同.

对DS18B20进行写操作时,FPGA先将数据线从高电平拉至低电平,进入写时间隙.15μs之内,FPGA应将数据送到总线上,DS18B20在15~60μs内对总线采样.低电平则写入0,高电平则写入1,连续写入数据位的间隙应大于1μs.

输入时钟频率取1MHz,即周期为1μs时,1个时隙至少需要60μs,且两个时隙间最小间隔1μs.故可以设定基本时隙时间为70μs,具体如图3所示.

3.2 DS18B20的FPGA控制方案

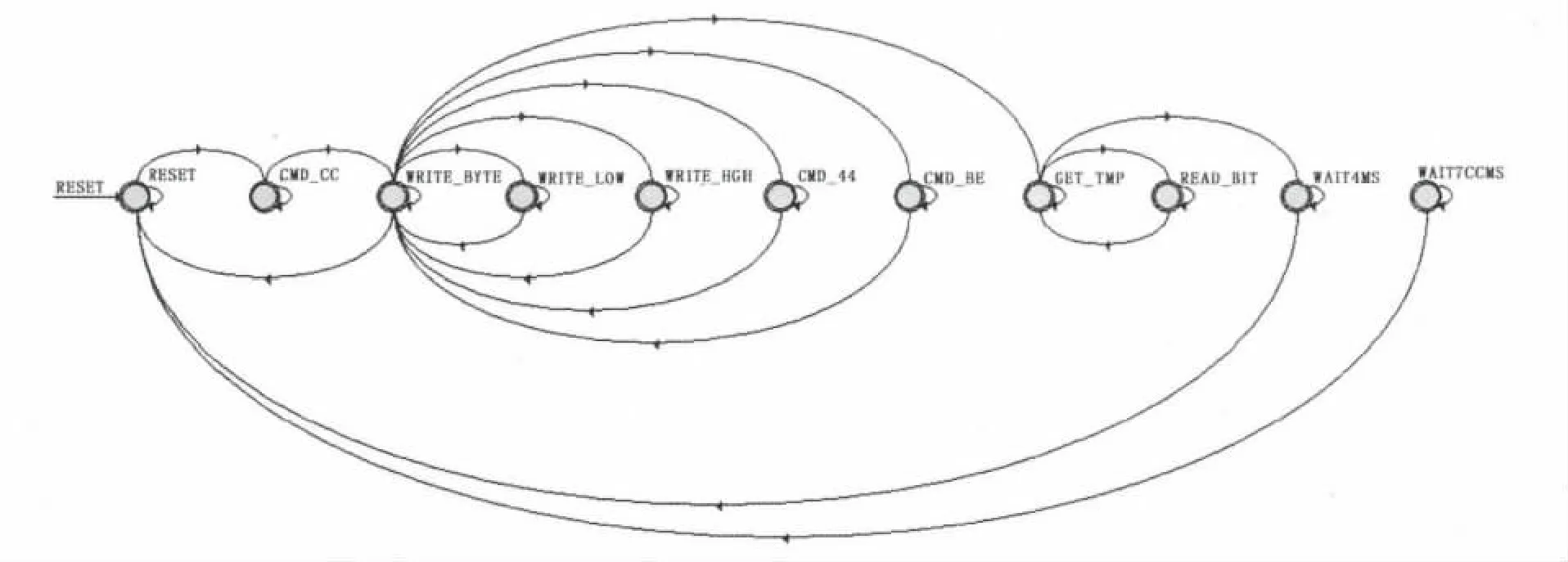

DS18B20的工作周期和操作时隙具有显著的顺序控制特征,适于用有限状态机(FSM)实现[2].实现DS18B20测温控制的有限状态机DS18B20_CTRL的状态转换图如图4所示.

图4 DS18B20_CTRL的状态图

3.2.1 DS18B20测温控制状态机DS18B20_CTRL的程序设计

DS18B20_CTRL状态图中,定义了11个状态,如表1所示.

表1 DS18B20_CTRL状态定义

我们用硬件描述语言VHDL编写该状态机程序.编译后的原理图元件符号如图5所示.其中clk1μs和rst端口分别是1MHz时钟信号和系统复位输入端;dq是与DS18B20单总线的连接线,定义为双向(INPUT)端口[3];temp_h和temp_l两个8位寄存器分别用于存储接收到的温度数据高低字节.

图5 DS18B20_CTRL的元件图

DS18B20_CTRL状态机的设计关键有两点:初始化状态和三个8位字节型命令的执行状态的设计.

初始化状态根据其时序要求,利用一个计数器cnt控制其进程.在490μs复位脉冲后释放总线(输出高阻),然后占用190μs以确定DS18B20器件是否存在,并根据DS18B20器件存在与否决定返回初始化还是进入后续状态.核心程序段如下:

三个8位命令即CMD_CC、CMD_44和CMD_BE的执行共同点在于均为8位写入,所以在进入其中某一状态后均需要转入字节写状态.并且由于写1和写0的区别,需对将要写入数据位的数据进行判断,以确定进入WRITE_LOW还是WRITE_HIGH状态.其次,需要设置一个写字节位数计数器WRITE_BYTE_CNT来控制字节写状态的结束.并且考虑到在图2所示的一个完整的工作周期中共需要顺序执行四次8位命令,所以设置了字节写标志WRITE_BYTE_FLAG用来控制三个8位命令的状态转换次序.具体程序段如下:

3.2.2 DS18B20测温控制状态机的仿真结果分析

选用ALTERA公司EP1C6Q240C8芯片,在QuartusII平台上编译仿真DS18B20_CTRL的结果如图6所示.

图6 DS18B20_CTRL程序仿真结果

图6中给出了系统复位后DS18B20一个基本完整的工作周期.第一个初始化状态(state.reset=0)后,字节写标志WRITE_BYTE_FLAG依次从0、1、2加到3,完成四次8位命令的写入,依次是CMD_CC→CMD_44→CMD_CC→CMD_BE,完成温度采集与转换;然后,即可读入测得温度数据,经过12个位读状态(GET_TMP_CNT从1递增至12),将12位温度数据格式转换后存入两个字节型寄存器temp_l和temp_h.注意图中4个8位命令字均为从低位到高位的格式写入,作为总线输出寄存器的dq_result以粗实线表示高阻态.

4 结论

本文在对单总线数字温度传感器DS18B20进行时序分析的基础上,完成了利用FPGA控制DS18B20实现温度数据采集的软硬件设计,重点剖析了采用有限状态机方法进行程序设计的关键点,仿真结果验证了设计的可行性.考虑到本设计采用的状态个数达11个,可以进一步采用层次状态机的方法对其加以改进.

[1]袁伟亭,周润景.FPGA与DS18B20组成的测温系统的设计[J].内蒙古大学学报(自然科学版),2006,37(7):459-463.

[2]王晓磊,李宏生.基于有限状态机的数字温度传感器控制系统设计[J].舰船电子工程,2010,30(12):182-185.

[3]穆振海.基于FPGA的智能温度采集控制器[J].微计算机信息(嵌入式与 SOC),2008,7(20):225-243.