一种高效率多输出同步整流电路的设计

2014-05-11胡旭,刘静

胡 旭,刘 静

(南京电子技术研究所,江苏 南京210039)

0 引 言

现代雷达集成电源模块的发展趋势是供电电压越来越低,体积越来越小,功率等级不断提高,功率密度成倍增长。随之带来的是降低损耗和散热的问题,尤其是在低压大电流输出的领域,效率作为至关重要的指标被突显出来。过去多采用二极管全波整流或半波整流的方式进行DC/DC变换,但在3 V~8 V低电压输出条件下,二极管正向压降的影响不能够再被忽视,即使采用肖特基硅二极管、快速恢复开关二极管等作为输出整流二极管,其正向压降均为0.4 V~0.6 V,大电流时的通态功耗很大。随着功率变换器输出电压的降低,输出电流的增加,整流损耗成为变换器的主要损耗。为了提高变换器的转换效率,必须降低整流损耗。采用低导通电阻的MOSFET进行同步整流,是提高变换器效率的一种有效途径。

1 混合型电路拓扑

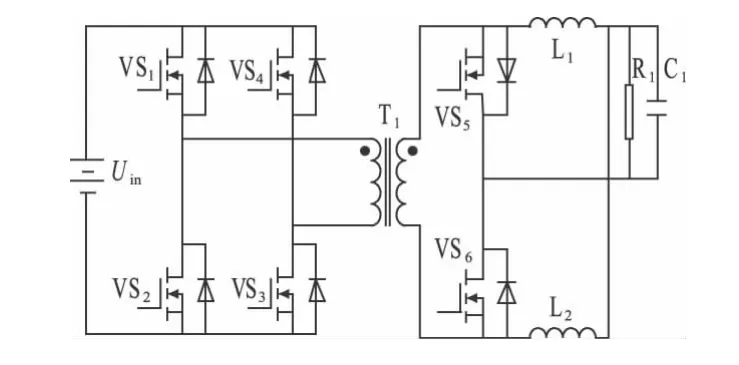

现设计研制一台高效率多输出同步整流电源,采用全桥、半桥加倍流同步整流的电路拓扑结构。全桥倍流同步整流的电路拓扑如图1所示,半桥倍流同步整流的电路拓扑如图2所示。

图1 全桥倍流同步整流电路

图2 半桥倍流同步整流电路

其中,倍流同步整流与半波整流和全波整流相比,具有以下优点:

(1)电感电流和变压器次级电流小,整流管导通损耗以及变压器铜损较小;

(2)双电感交错滤波,可在电感值较小的前提下,减小电流纹波,并提高动态响应性能;

(3)大电流的电路相互连接数目最少,简化了次级的布线,并减少了与布线有关的损耗;

(4)倍流整流的滤波电感可以被集成到主变压器中,减少了元件数量和总体体积。

实验结果证明,本电路拓扑提供了三路不同幅值并相互隔离的输出电压,并可以降低整流损耗,提高整流效率,变换器的转换性能也得到了很大的改善。

2 同步整流管以及驱动方式的选择

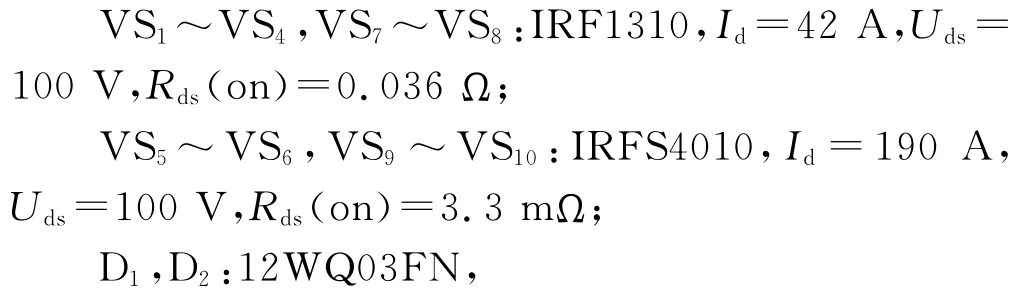

同步整流的原理是应用MOSFET管取代不控整流中的肖特基二极管,因此选择同步整流管的基本要求是导通电阻Rds(on)尽量小,电压和电流不超过整流管的电压和电流限值。由于输入电压范围是30 V~70 V,且主变压器次级电压也超过70 V,因此本设计选择的同步整流管选取IR公司IRFS4010,其漏源极耐压为100 V,导通电阻为3.3 mΩ。

同步整流管选定后,使用PWM控制芯片的外驱动方式对同步整流管提高驱动电压。同步整流管的外驱动方式是指PWM信号经过适当的组合和延时后,作为同步整流管的驱动信号。同步整流管的驱动电压从附加的外部驱动电路获得,可以提供比较精确的控制时序。基于本驱动方式的诸多优势,此处采取PWM控制芯片SG3525和IXDN414驱动的方式。由于此电源为3路独立隔离输出,电路在具备3路隔离辅助电源的同时各路驱动信号也需要与主电路隔离,此处采用驱动变压器隔离的方式。同步整流管IRFS4010的驱动特性如图3所示。

图3 IRFS4010的驱动特性

从图3可以看出,在漏源电流相同的情况下,驱动电压越高,漏源极上电压降越小。也就是说驱动电压越高,同步整流管等效的导通电阻越小。同步整流管IRFS4010最大驱动电压为±20 V,为了保证不超过驱动电压最大值,平衡效率与风险,将驱动电压设计在17 V左右。这样可以明显减小同步整流电路的导通损耗,提高整流电路效率,同时在栅源极两端增加20 V稳压管,保证整流管不会因为驱动电压过高而被击穿。

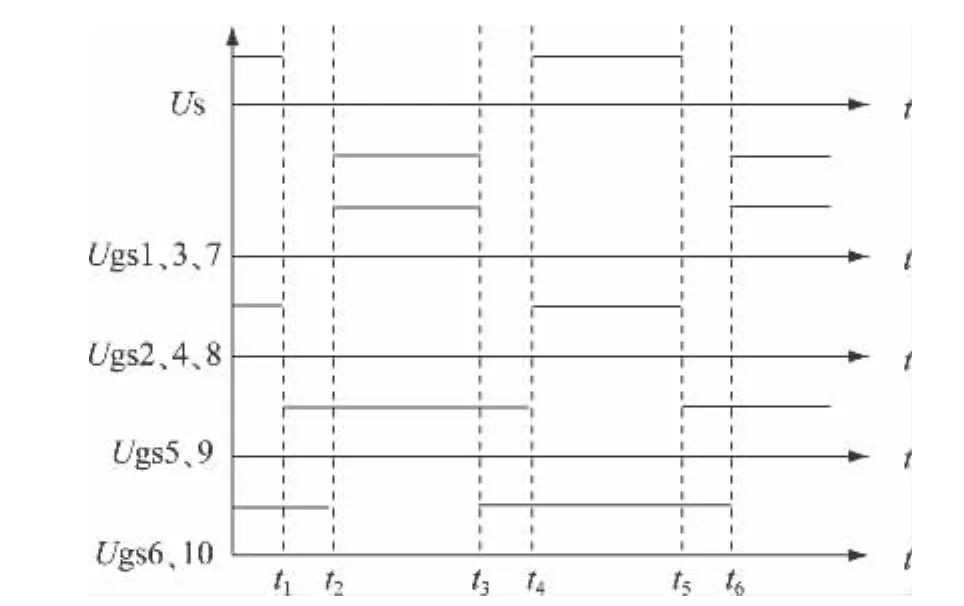

同步整流管的驱动时序关系如图4所示。

图4 同步整流管的驱动时序关系

从图4所示的驱动时序关系图可以看出,当变压器同名端为正时,同步整流管VS5、VS9导通,向负载端提供电能;当变压器同名端为负时,同步整流管VS6、VS10导通,向负载端提供电能。负载电流通过同步整流管流过,导通损耗小。同时,在时间段t1~t2之间,同步整流管的提前导通保证了负载电流从MOS管漏源极间流过,而不通过其体二极管;在t3~t4之间,同步整流管的延时关断同样提供了MOS管漏源极间的续流通道,降低了流过MOS管体二极管造成的导通电流损耗。

为获得如图4所示时序关系的驱动波形,在PWM芯片SG3525和驱动芯片IXDN414后端接上两个次级的激励变压器。并将同步整流管端的驱动信号反接,以获得反相互补的激励波形。

3 电路参数的设计和实验结果

3.1 电路参数

这种多输出同步整流电路输入电压为48 V(30 V~70 V),三路输出电压分别为8 V/32 A,5 V/8 A,-5 V/2 A。单路8 V/32 A采用全桥倍流同步整流电路,如图1所示;单路5 V/8 A采用半桥倍流同步整流电路,单路-5 V/2 A采用半桥全波整流电路,如图2所示,三路输出电压相互隔离。全桥电路输出滤波电感取2×2 mH,半桥电路输出滤波电感取2×4 mH,开关频率为100 kHz。元器件清单如下:

从实验波形可以看出,在能量从原边传送到负载端的过程中,驱动电压保证了同步整流管的适时导通,使负载电流不从MOS管体二极管流过,降低了整流管的导通压降,提高了整机效率。

3.2 实验结果

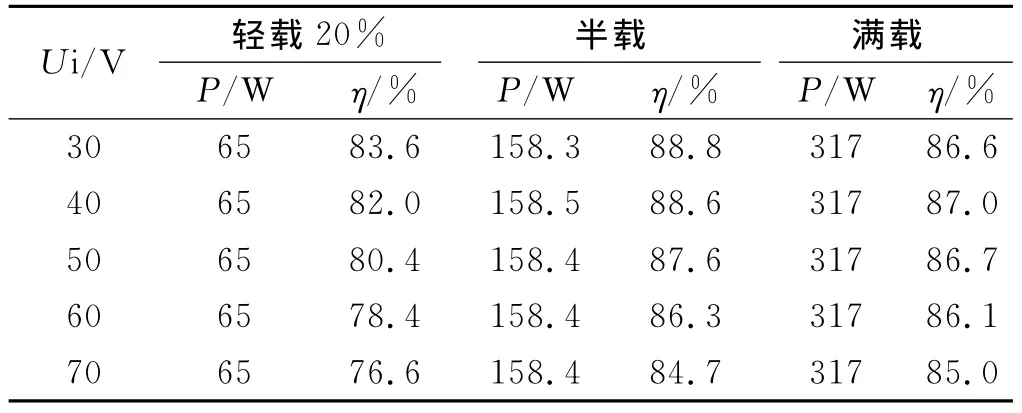

实验中对同步整流电路在轻载(20%负载)、半载、满载状态下的电路指标进行了测试,输入电压在30 V~70 V条件下的参数如表1所示。

表1 实验结果

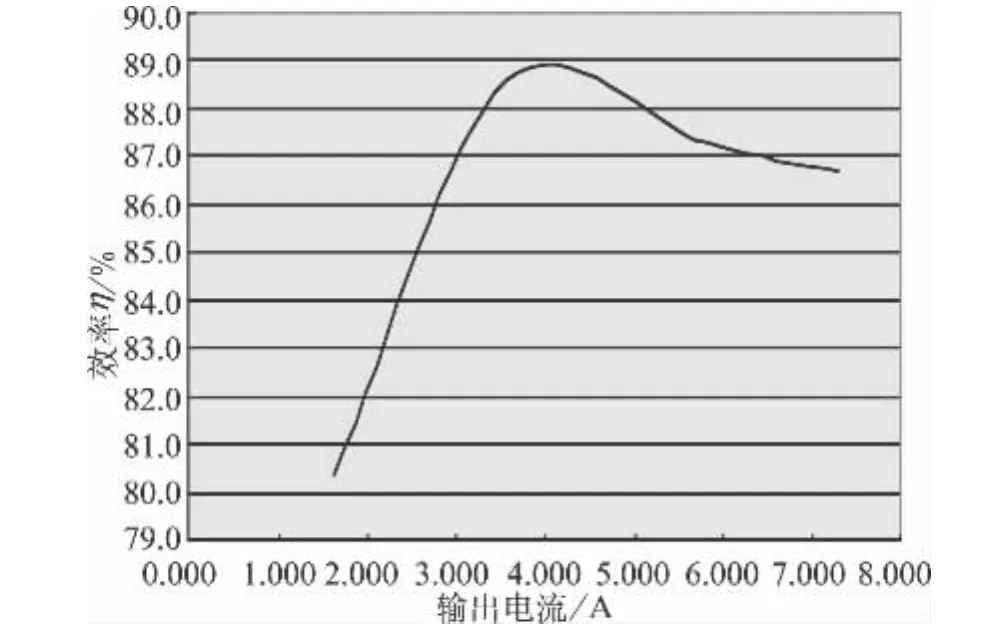

由表1可以看出,当输入电压为48V时,该电路的转换效率最高可达89%,输入电压在48V条件下完整的效率曲线如图5所示。

图5 效率曲线

4 结 论

本文利用同步整流技术,使用全桥倍流同步整流和半桥倍流同步整流拓扑,并采用PWM控制芯片加激励变压器的驱动形式,设计了一台48 V(30 V~70 V)输入,三路隔离(8 V/32 A、5 V/8 A、-5 V/2 A)输出的混合型DC/DC变换器,该变换器的最高效率达到89%。理论分析和实验结果证明,该混合型拓扑和驱动形式解决了低压大电流条件下变换器效率低的问题,并能够提供多路隔离的输出电压,降低了整流损耗,提高了整流效率。

[1]Rozman A F,Richardson.Low loss synchronous rectifier for application to clampd-mode forward[P].US Patent:5303138,1994-04-12.

[2]胡宗波,张 波.同步整流中 MOSFET的双向导电特性和整流损耗研究[J].中国电机工程学报,2002,22(3):88-93.

[3]张海源,吴 卉,邹祖冰,等.同步整流下对称半桥倍流变换器的建模分析[J].中国电机工程学报,2003,23(8):66-70.

[4]顾亦磊,黄贵松,章进法,等.一种新颖的同步整流驱动电路[J].中国电机工程学报,2005,25(5):74-78.

[5]胡宗波,张 波,赵 磊.一种应用同步整流技术的高效率正激变换器的设计[J].电工电能新技术,2002,21(4):69-73.

[6]刘凤君.现代高频开关电源技术及应用[M].北京:电子工业出版社,2008.