基于FPGA和Modbus协议的通用数据采集装置设计

2014-03-26单建华齐立华

孟 飞,单建华,丁 晨,齐立华

(1.常州工学院光电工程学院,江苏常州 213002;2.常州市光电子材料与器件重点实验室,江苏常州 213002)

0 引言

数据采集是测控系统的基本需求。目前,对于分布式测控系统其现场数据采集或控制节点往往由PLC加模拟量模块的方式来实现,而对于现场采集通道较多、数据量较大的则采用专门的现场主机扩展数据采集卡的方式来完成数据采集功能[1-2]。这些方案的优点是较为成熟,但相对复杂的设计和较高的费用对于一些成本较为敏感的测控系统而言是无法承受的。该设计采用现场可编程门阵列(FPGA)为控制核心,扩展模数转换器(ADC)等器件设计数据采集装置;选择工业控制领域使用较多的Modbus协议,不仅能组网实现分布式数据采集,也能很好地与既有系统中的工控机、PLC和触摸屏等进行数据交换,在使用上较灵活方便。

1 数据采集装置的硬件设计

1.1 数据采集装置的基本构成

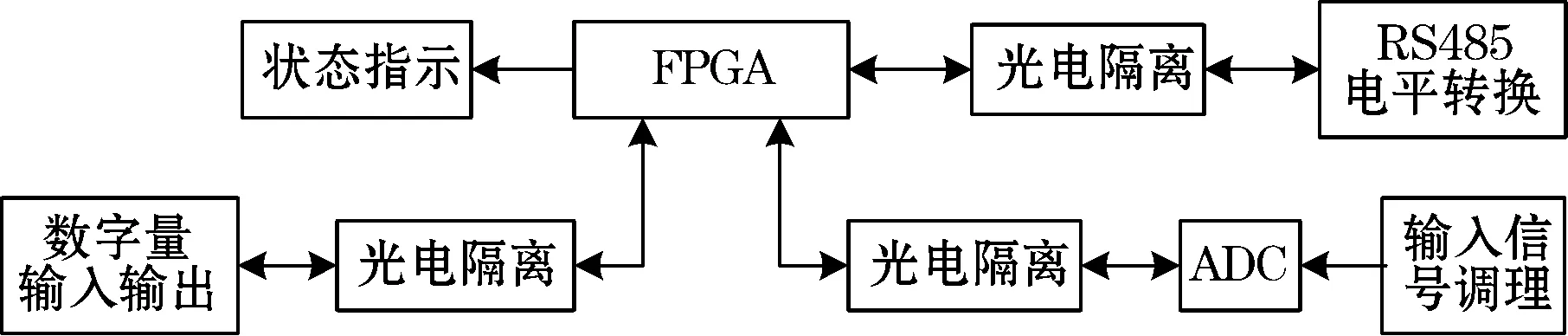

数据采集装置硬件上由FPGA、ADC、通信接口转换器件和隔离电路等组成。FPGA是数据采集装置的控制核心,负责控制ADC转换和Modbus协议的解码和编码等。设计中Modbus协议的硬件介质基于RS485,具有较好的抗干扰性和较长的通信距离。ADC转换器件在FPGA的控制下将现场传感器等模拟信号转换成数字量按Modbus格式要求转换后通过RS485传送给上位计算机、PLC等。数据采集装置的硬件组成如图1所示。

图1 数据采集装置的硬件构成

1.2 数据采集系统的配置

采用本数据采集装置构建数据采集系统时,可选用支持Modbus协议的触摸屏或安装有支持Modbus协议的组态软件的工控机等作为上位机,进行必要的组态开发设计上位机监控软件以实现数据的存储、趋势曲线显示等功能,数据采集系统的配置结构见图2。

图2 数据采集系统的配置方案

1.3 数据采集装置的主要器件选型及设计

该数据采集装置中FPGA主要承担ADC的时序逻辑控制以及Modbus协议的编码和解码运算,其对内部资源及速度等方面的要求主流的FPGA芯片一般都可满足,因此重点考虑的是功耗、稳定性和价格之间的平衡。Cyclone IV系列产品其内部集成高达15万个逻辑单元,采用经过优化的60 nm低功耗工艺,与上代产品相比,总功耗降低了25%[3-4]。根据该设计中对逻辑资源的消耗评估选择了其中的EP4CE6E22C8,其具有6 K的逻辑单元和91根I/O引脚,能够满足设计中对内部逻辑单元和外接ADC以及数字I/O的扩展。采用EPCS16作为FPGA的配置芯片。

一般的工业场合对现场模拟量的分辨率要求并不会特别高,以10位、12位甚至8位等为主流,单纯追求过高的分辨率由于现场各种噪声干扰往往只会成为“理想”的指标,而不会对提高系统的实际精度有明显作用,因此将分辨率选择为12位。此外,工业现场的各类传感器、变送器基本都已经标准化、系列化,以4~20 mA或0~5 V(1~5 V)为主,因此对ADC输入范围限定为0~5 V为宜。

AD7891是一种8通道、12位的模拟到数字量的转换器。根据输入电压的范围细分为多个型号,最大采样速率达到454 KSPS,接口方式串行或并行可选,而FPGA的I/O数量较多,为简化控制程序设计采用并行方式。该设计选用AD7891ASZ-1,通过选择输入引脚将其输入电压范围限定为± 5 V,满足了输入电压范围的要求以及一些需要双极性输入的场合。AD7891已经内置了多路输入选择开关、采样保持器和基准电压源等,采用+5 V单电源供电,因此其所需外围器件较少,接口方便。因FPGA I/O引脚的可配置性,AD7891的控制信号和数据端等引脚与FPGA的连接比较自由,只需考虑布线的方便即可。需要注意的是AD7891和FPGA的电平范围不一样,尽管两者的电平阀值是兼容的,但AD7891的输出电平较高,超出了FPGA I/O引脚的建议电压范围,为避免输入电压过高导致FPGA芯片损坏的可能,应在两者之间接入电平转换芯片或接入分压电阻。

由于Modbus协议的硬件传输介质采用RS485,因此需要在FPGA和通信网络之间添加转换芯片,设计中选用MAX3491,采用3.3 V电源供电,可直接与FPGA连接。其理论传输速度最大10 Mbit/s,主要是为某些特殊场合下仅配置单个数据采集装置而期望较高速度时不至于在通信硬件上产生瓶颈。

为提高系统的稳定性和提高模拟量采集精度,采取电源隔离和光电隔离以及在输入端口接入瞬态抑制二极管TVS等措施来保证。开关量输入输出和ADC的控制、数据信号等与FPGA之间采用光电隔离。外部开关电源的输入经DC-DC隔离电源模块变换后供给FPGA一侧,而ADC的供电采用了开关电源后加线性稳压芯片的方式以提高ADC模拟电路的电源质量。

2 数据采集装置的软件设计

与硬件模块相对应,ADC的控制程序以及Modbus的编码和解码是数据采集装置的主要程序模块。软件以QUARTUS II集成开发环境为开发平台,采用Verilog HDL硬件描述语言进行软件开发。相比采用单片机等方案不同,FPGA的并行化执行特征,使得不同功能模块之间的时间分配、数据交换等变得简单而清晰,不同模块间相对独立且并行运行,通过定义和设置寄存器的方式完成不同程序模块之间的数据交换以及控制数据采集装置的运行状态。

2.1 A/D转换程序设计

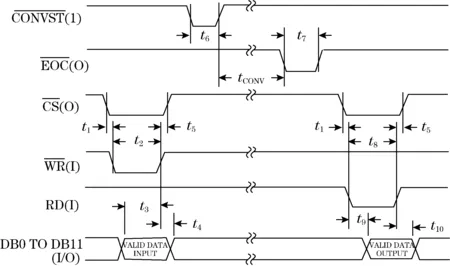

AD7891工作在并行模式时,其时序逻辑如图3所示。开始转换前片选CS、写信号WR等引脚按图示时序要求作电平变化,在相应引脚拉高前后将控制寄存器的数据发送到数据总线上,短时间拉低转换启动CONVST引脚开始转换,其后监测EOC转换结束信号是否有效,有效后延迟适当时间读取A/D转换器的转换结果,具体时间和控制寄存器定义在参考文献[5] 中作了详细的规定。

图3 AD7891并行模式时序逻辑

2.2 Modbus程序设计

Modbus协议是主从站通信协议,除主站外最多可接247台从站,但受线路负载能力和通信时效等限制,实际的基于Modbus的分布式测控系统一般不超过32台从站,所有主从站的波特率、校验规则等参数应严格一致。Modbus协议可使用ASCII、RTU两种模式,该设计中采用RTU模式[2,6]。Modbus作为一个工业通信协议,其定义了较为丰富的功能码,该设计中主要涉及模拟量的读取以及数字量的读取和输出,因此只需使用其功能码中的少数几个,是简化的Modbus协议。Modbus的收发过程是主机发出命令帧(由从站地址、功能码、数据起始地址和数据数量以及CRC校验码等几部分组成),处于监听状态的从机当监测到命令帧中的地址与自己地址相同时,开始接受其后的功能码等信息,根据功能码及相应的数据读取或设置从站内的相应寄存器、数字量I/O口等操作。从站根据执行的情况向主站反馈应答信息,即回复包含从站地址、功能码、数据长度、具体数据和CRC校验码等信息的应答帧。

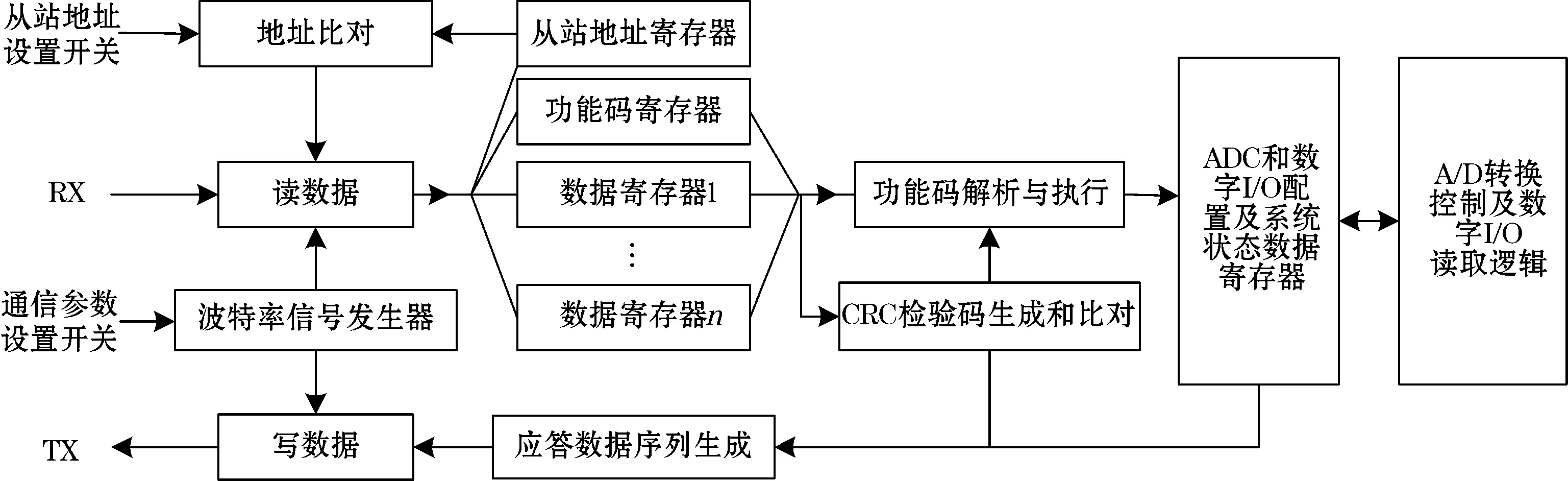

根据Modbus协议的基本要求,将Modbus协议的实现分解为波特率时钟信号发生单元、读写数据单元、功能码解析和执行、CRC校验码生成和比对、寄存器组以及相应的控制逻辑等若干模块组成,FPGA的内部各功能程序单元之间的关系和结构如图4所示。

波特率信号发生器由FPGA外接的通信参数设置开关来设定波特率参数,是串行数据读写节拍的基准,应与主站保持一致。读数据逻辑根据总线上过来的信号,首先读取到从站地址放到相应的寄存器中,地址比对逻辑将其与从站地址设置开关的二进制代码进行比对,如不一致则丢弃后面的数据,继续等待和监测下一帧数据,否则按顺序将功能码等读至相应的寄存器以进行CRC校验和执行相应的功能。而应答数据序列生成单元则根据执行的结果及当前的功能码等生成应答数据发给CRC校验单元生成校验数据,构成完整的应答数据帧经写数据模块发送给主机。设计中CRC校验码的生成采用查表法来完成,相比计算法逻辑上简单明了,缩短了程序调试周期。

图4 FPGA程序结构

3 应用与实验

该数据采集装置已应用于SF6断路器微水含量实时监测系统中,系统根据图2示意的配置方案进行布线和连接,利用数据采集装置中的模拟量输入通道对微水含量传感器的模拟量输出信号进行转换。而上位机则采用VB自行开发了监控软件,能够实时显示各断路器内SF6气体的微水含量值和趋势曲线。经过两个月的实际应用,对回传数据进行分析未出现明显的数据丢失或大的采集偏差,这表明该数据采集装置以及所构成的系统运行稳定,可靠性好。

4 结束语

文中介绍了一种以FPGA为控制核心,采用Modbus协议的数据采集装置能实现多通道的模拟量输入和数字量的输入输出等功能,数据采集装置能方便地配置,具有结构简单、组网方便和易扩展等特点。因此,在对速度和数据吞吐量要求不高的应用领域具有很好的推广使用价值。

参考文献:

[1] 王振力.工业控制网络.北京:人民邮电出版社,2012.

[2] 陈在平,岳有军.工业控制网络与现场总线技术.北京:机械工业出版社,2007.

[3] 吴继华.Altera FPGA/CPLD设计.北京:人民邮电出版社,2011.

[4] 曹建锋,陈星,王明智.一种基于FPGA的Modbus通信协议的接口设计与应用.仪表技术与传感器,2013(3):79-84.

[5] LC2MOS 8-Channel 12-Bit High Speed Data Acquisition System AD7891. Analog Devices Inc.,2004.

[6] 安子良,肖立中,孔令超.基于Modbus RTU通信协议的石油井架应力监测系统.中国测试,2011,37(6):72-75.