基于FPGA的DVI程序设计与开发

2014-03-26康兴斌康玉文

康兴斌,康玉文

基于FPGA的DVI程序设计与开发

康兴斌,康玉文

(漳州职业技术学院 机械与自动化工程系,福建 漳州 363000)

随着科学技术快速发展,解决LED彩色大画面显示成为突出问题。采取改进的LED显示屏幕控制系统,并利用XC3S400A芯片实现了该LED大屏幕控制系统。采用可编程逻辑器件,在不需要修改电路硬件设计的基础上可以缩短设计周期,又可以实现灵活性,还可以实现高速图像数据处理对速度的要求。

FPGA;DVI接口;LED显示屏

1 引 言

当今,业界不断加大对LED显示屏研发的投入,市场对LED显示屏的需求越来越大,不仅因其高亮度、色彩鲜艳、画面清晰等特性,还有环保、节能、寿命长等特点,且在价格上比其它平板显示器有无法比拟的优势。

本文采用在基于FPGA开发研究的平台,并对LED显示屏控制系统是一种灵活的控制器设计方向[1][12]深入的研究。采用这种FPGA方式,在此开发方式下修改内部硬件逻辑可以实现在线升级,将为以后开发升级提供便捷使用。

2 FPGA技术和ISE开发软件/Modelism仿真工具

2.1 FPGA技术

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在CPLD、PAL、GAL等可编程器件的基础上进一步发展的产物[12]。对研发者和设计者来说它的最大特点就是迭代性很强。在测试过程中发现问题,往往需要返回原来的步骤,需要重新审查、修改,然后重新综合、实现、仿真验证,并达到目标的需求。

2.2 ISE开发软件/Modelism仿真工具

ISE是Xilinx公司提供的集成化FPGA开发软件,它的主要功能包括设计输入、综合、仿真、实现和下载[13]。Mentor Graphics公司的Modelsim是业界较好的仿真工具,它的仿真功能强大,且图形化界面好,而且具有结构、信号、波形、进程、数据流等窗口[14]。Modelism现在又好几种版本,比如:SEOEMPE。

3 系统设计说明

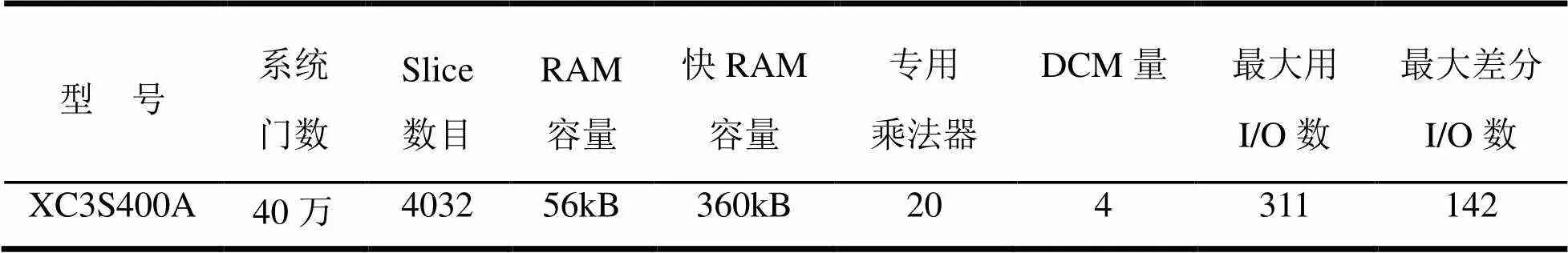

3.1 型号XC3S400A芯片

XC3S400A芯片属于Spartan 3A系列中的一个中等型号的芯片。Spartan 3A在Spartan 3和Spartan 3E平台的基础上,整合了各种创新特性帮助客户极大的削减了系统总成本。利用独特的期间SNA ID技术,实现业内首款FPGA电子序列号。主要技术特征如表1。

表1 XC3S400A主要技术特征

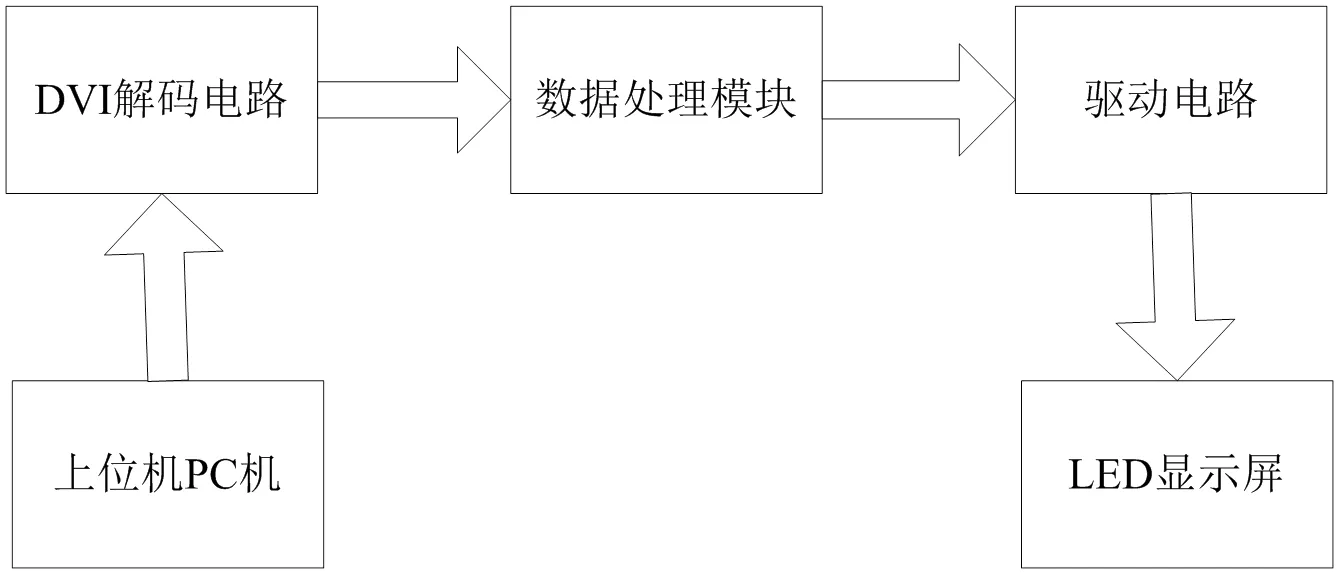

3.2 控制系统总体方案

整个控制系统分成三大部分:DVI解码电路模块,数据处理模块,驱动电路模块[15][17],如图1。

图1 系统总体框图

(1) DVI解码电路:接受来自上位机的视频信号,根据一定的协议,把视频信息解码成为一下级数据处理模块可以使用的是数字数据。

(2) 数据处理模块:它完成RGB数据的转换,并且按一定规律转换成适合驱动电路的数据。

4 FPGA内部子模块设计

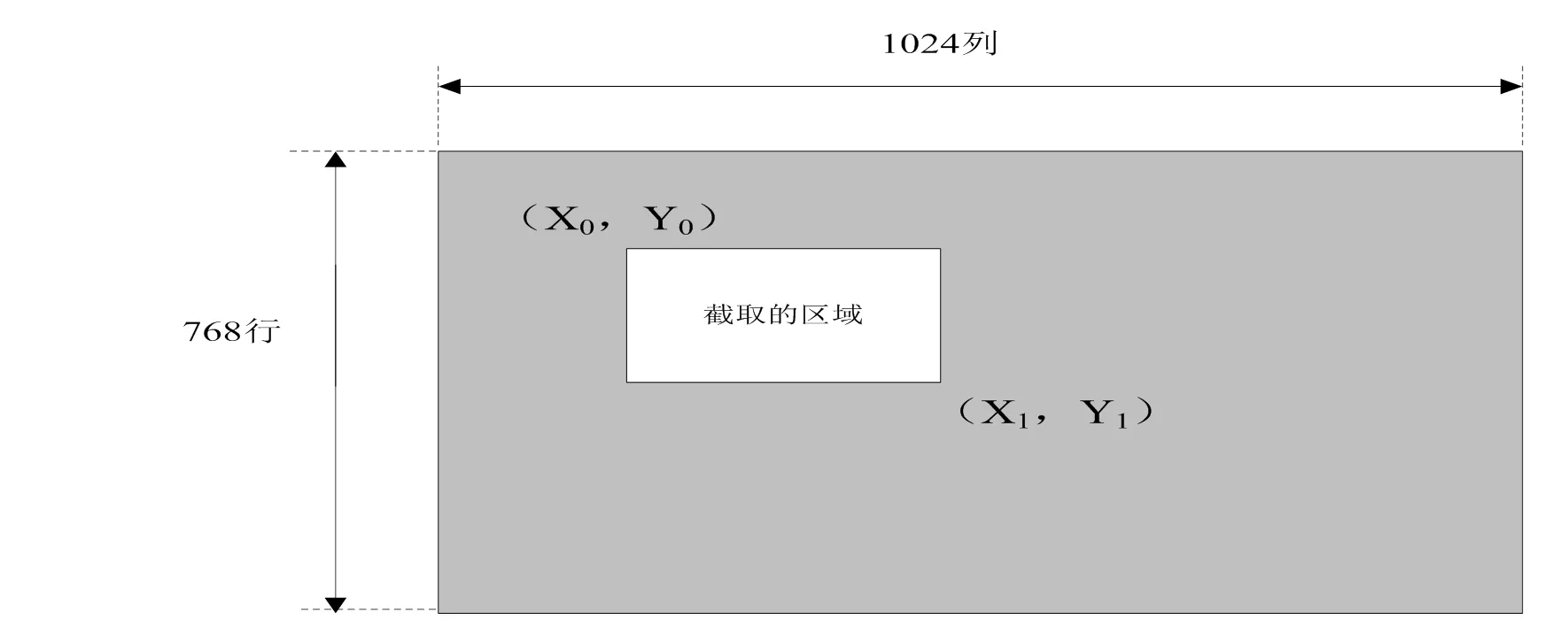

4.1 数据截取模块原理概述

本文截取的是如图2所示的部分:DVI截取显示器视频输出以(X0,Y0)作为起始坐标,(X1,Y1)作为终点坐标[18][19]。

图2 数据截取示意图

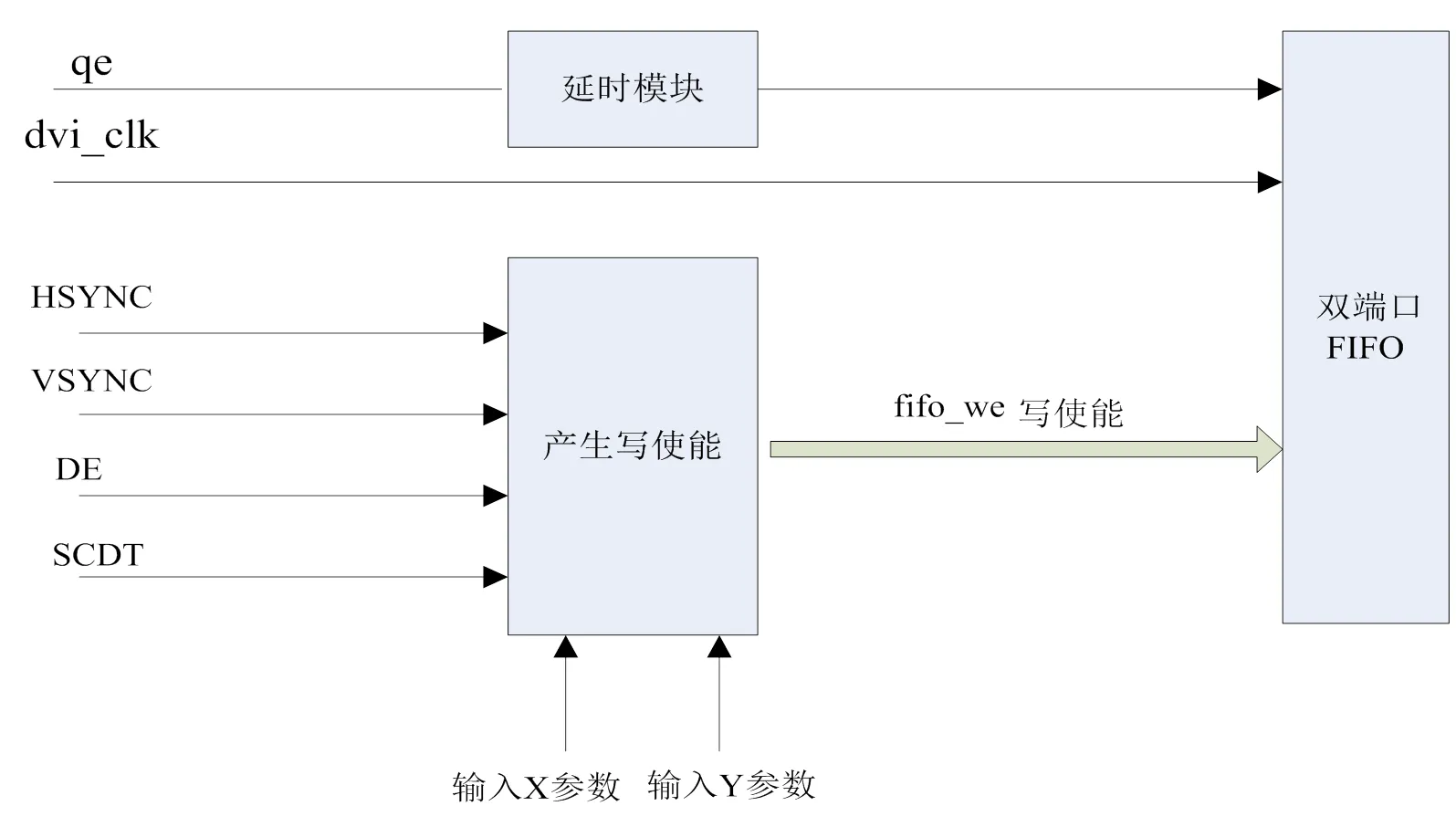

因为产生写使能需要消耗几个时钟周期,所以数据要经过适当的时钟延时后根据dvi_clk写入双口FIFO。

输入:来自DVI解码芯片的场同步vsync,行同步hsync,数据使能de,写时钟wrclk,颜色数据qe[0:23],还没有读时钟rdclk。

其中,rdclk由时钟管理模块生成。

输出:fifo_we写使能,截取的数据qout[0:49]。

当行同步信号HSYNC和数据时能信号de同时有效时,来控制行列计数器,再利用外面输入的两个坐标的值跟行列计数器进行比较后生成fifo_we写使能信号。由于行列计数器的计数和比较需要消耗掉几个时钟周期,因此我们需要将像素点信息qe相应延时几个时钟周期。

数据截取系统结构框架图如图3所示。

图3 数据截取系统结构框架图

4.2 内部子模块实现

数据截取模块中主要实现了根据行场同步来实现行列计数器清零;系统根据行列计数器来产生x_start(X开始标志信号),x_to_end(X结束标识信号),x_start(Y开始标志信号),y_to_end(Y结束标识信号);系统根据x_start和y_start两个信号和输入的参数进行比较来产生fifo_we写使能信号。

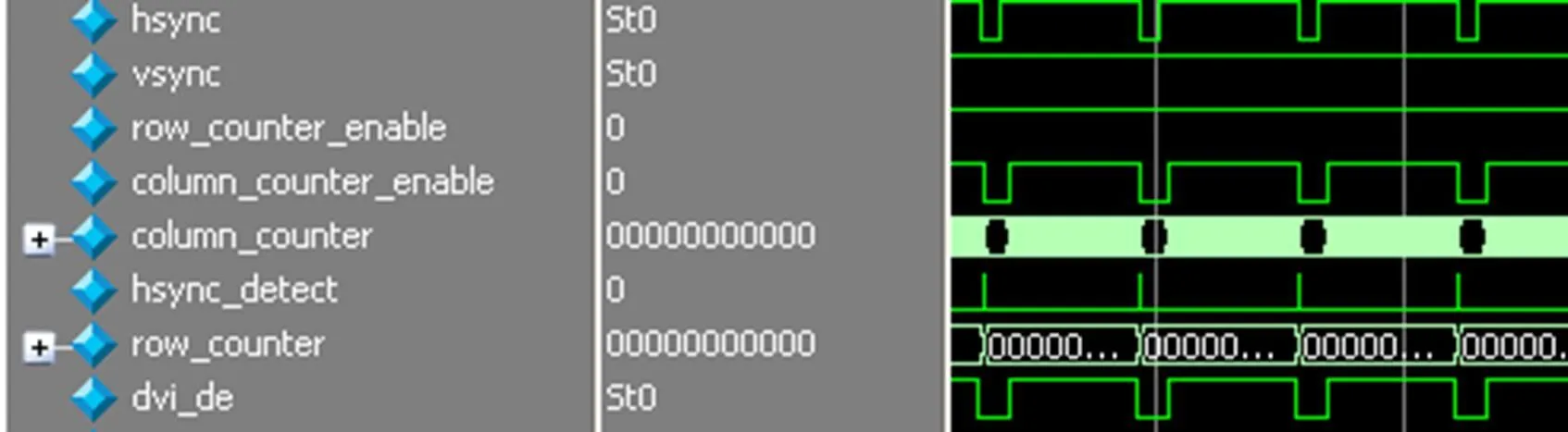

在LED显示系统中,点阵结构单元为其基本构成,在输出一行数据后解码芯片发出一个HSYNC信号,此时列计数器清零同时行计数器加1,当VSYNC有效列计数器和行计数器同时清零。开始先复位清零,当检测SCDT(同步检测信号)为高,然后检测VSYNC(场同步信号)是否为有效,当VSYNC有效时行列计数器都清零,当VSYNC有效时检测DE(使能信号)是否为高,检测到DE为高且HSYNC也为低时行计数器加1,检测到DE为低且HSYNC有效时保持,检测到DE为低且HSYNC为高时列计数器清零。仿真结果如图4。

图4 计数器清零功能仿真

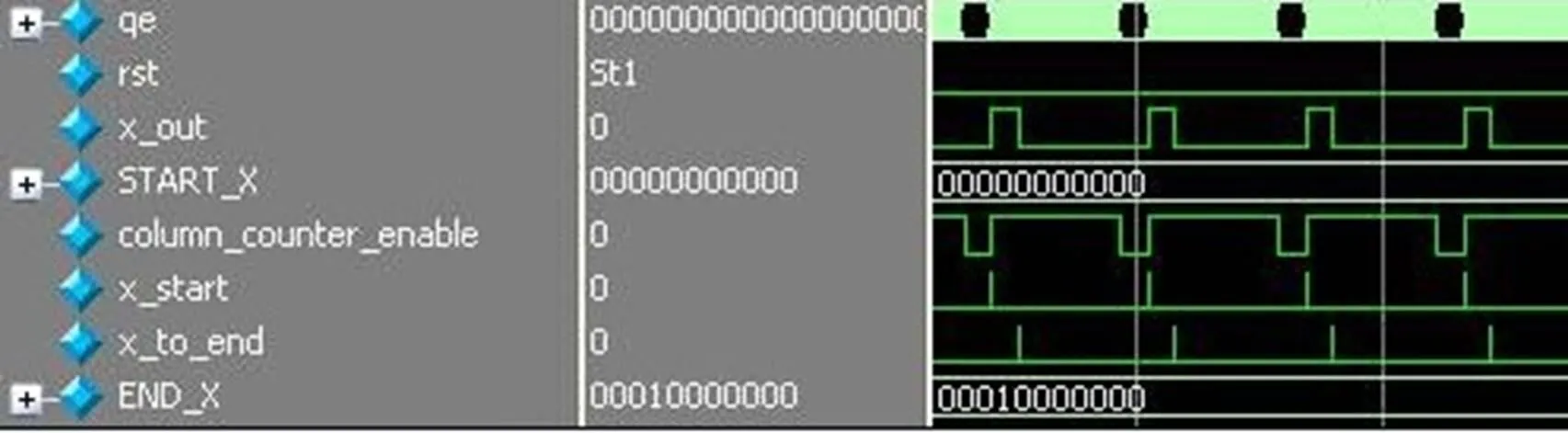

根据上个模块行列计数器的计数情况来产生x_start为x方向开始标记,x_to_end为x方向结束标记,y_start为y方向开始标记,y_to_end为y方向结束标记。以x方向为例仿真如下。

其中START_X信号以及END_X信号是手动输入的起始和终止信号的两个参数x_out为x输出使能信号。仿真结果如图5所示。

图5 输出屏幕位置功能仿真图

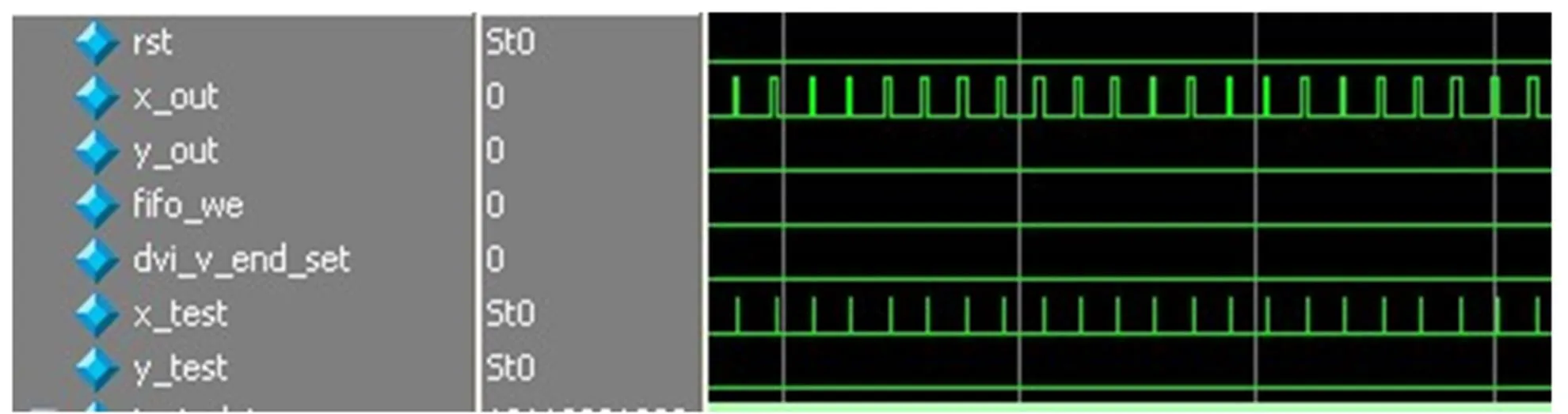

根据X_START和Y_START来产生写使能;仿真结果如图6所示。

图6 产生fifi_we使能功能仿真图

5 小 结

本文改进了LED显示屏幕控制系统。DVI接口能够以简单、低成本的方式传送高带宽的数字视频信号,其输出的数字信号不仅可以输送给近距离的电脑显示屏,还可以经过变换和处理,通过传输介质,送给远距离的数字显示终端。仿真结果表明,主要是实现DVI接口对数据的截取实现了确定输出屏幕位置即(X,Y)坐标以及实现写使能控制信号fifo_we的输出将数据写入fifo等待后续模块的处理。

本设计初步实现了全彩色LED显示屏控制系统的DVI接口功能,在以后的工作中还需要进一步改进和完善。如从DVI口出来的数据在显卡中已事先进行了预校正,即Y校正,如果直接把送给CRT的数据拿来给LED用,就会出现低亮度段得亮度跳变太快,使图像的层次感欠佳,为了提高LED显示质量,在以后的工作中需要对输入数据进行反Y校正。

[1] 俞彬杰.基于FPGA的全彩LED同步显示屏控制系统的设计[D].上海交通大学硕士论文,2008.

[2] 潘松,黄继业.EDA技术适用教程[M].北京:科学出版社,2002:16-20.

[3] 夏文宇.Verilog数字系统设计教程[M].北京:航空航天大学出版社,2003:1-4.

[4] 杨娇.LED大屏幕与VGA同步彩色视频显示系统设计[D].武汉科技大学硕士论文,2006.

[5] DDWG.Digital Visual Interface DVI[J].1994,4,Revision1.0:1-3

[6] DAVICOM Semiconductor,Inc.DM9000A DATASHEET[S].2005,4.

[7] 蒋兆林.DVI数字显示接口标准[J].电子产品世界,2001(4):1-2.

[8] 倪榕斌.DVI接口在电视机及显示器中的应用[J].电子世界,2004(5):2-4.

[9] 冯永茂,丁铁夫,王瑞光,陈宇.数字视频接口DVI1.0[J].电子技术应用,2003(9):1-3.

[10] TI,TI PanelBus Digital Receiver TFP201A datasheet[J].2003(6):1-2.

[11] Video Electronics Standards Association [M].VESAE-EDID Implementation Guide.Version1.0,2001:1-18.

[12] 王冠,俞一鸣等.面向CPLD/FPGA的Verilog设计[M].北京:机械工业出版社,2007:71-74.

[13] 王城,薛小刚.FPGA/CPLD设计工具-Xinlix ISE使用详解[M].北京:人民邮电出版社,2005:19.

[14] 孙富明,李笑盈.基于多种EDA工具的FPGA设计[J].电子技术应用,2002(1):1-4.

[15] 诸昌玲.LED显示屏系统原理及工程技术[M].西安:电子科技大学出版社,2000(12):15-20.

[16] 康志英,冉峰,徐美华.LED显示屏高灰度扫描控制的FPGA实现[J].微计算机信息,2006(20):1-3.

[17] 蔡林飞.LED全彩大屏幕同步显示控制系统设计[D].绵阳:西南科技大学,2007:59.

[18] 姜洪英.基于DVI接口的LED视频显示系统的研究与设计[D].吉林大学硕士学位论文,2006.

[19] 叶心明.基于FPGA的LED视频显示控制系统的设计[D].上海交通大学硕士论文,2009.

(责任编辑:季平)

Design and Development of DVI Program Based on FPGA

KANG Xing-bin,KANG Yu-wen

(Department of Mechanical and Automation engineering, Zhangzhou Institute of Technology, Zhangzhou 363000,China)

With the development of science and technology the LED, solving the large color screen display is particularly prominent problems. By the improved LED display screen control system, it uses XC3S400A chip to realize the LED large screen control system. In order to improve the quality of LED display, it need anti Y correction on the input data in operation. Using the programmable logic devices, it does not need to modify the underlying hardware design can shorten design cycle, and can achieve flexibility, also can realize high-speed image data processing requirements of speed.

LED Panel; FPGA; DVI Interface

2014-04-16

康兴斌(1981-),男,福建龙海人,助教,在读硕士,研究方向:计算机技术、无线局域网。

1673-1417(2014)02-0021-05

10.13908/j.cnki.issn1673-1417.2014.02.0004

TN948.55

A