基于CPLD的TMS320C6727B外设重叠地址空间解析方法的研究与实现

2014-03-24黄璜,田伟

黄 璜,田 伟

(1.第二炮兵工程大学研究生管理大队,西安710025;2.海军航空工程学院训练部,山东烟台264001)

TMS320C6727B(以下简称C6727)是TI 公司于2006年推出的单核高性能32/64bit浮点数字信号处理器,CPU 主频可达300 MHz,处理能力达到1 800 M FLOPS,为专业音频处理、通信基带信号处理等领域的应用提供了高性价比的解决方案。在硬件上,C6727 片载dMax DMA 数据传输引擎、3 组累计16 个通道的McASP专业音频采集接口模块、2个全双工定时器、2个SPI全双工同步串行端口、2组I2C两线式串行总线模块、1 组UHPI 通用主机接口、软件可编程锁相环电路等,为各类开发应用提供了灵活多样的硬件解决方案[1-5];在软件上,C6727 片载了384 k bit 掩模ROM,内置Bootloader模块、全功能DSP/BIOS实时多任务操作系统以及优化的数字信号处理函数库(DSPLIB),非常有利于信号处理软件开发及其市场化。C6727 丰富的片载硬件与软件资源,助推了其在音频信号和通信基带信号处理领域的广泛应用。

C6727 在设计上简化了地址总线,其片载硬件资源都分配了固定的地址,片外扩展的SDRAM 映射到0x80000000 的地址空间,片外扩展的Flash 映射到0x90000000 的地址空间,读写控制非常便捷;但用户扩展的其他外设器件,需要通过外围逻辑电路对地址空间进行解析,否则无法实现对外围器件的片选控制和端口访问。针对这一问题,本文提出了一种基于CPLD的重叠地址空间解析方法,可满足大量外设、外设大量地址段的地址空间解析需求。

1 C6727的地址空间分配

C6727 的地址总线宽度为32bit。其中,从0x00000000~0x0005FFFF 的384 k bit 空间映射为片内的ROM区域,用于内置启动加载器、固化DSP函数库等;从0x10000000~0x1003FFFF的256 k bit空间映射为片内RAM,用于应用程序运行时的程序或数据存储;从0x80000000~0x8FFFFFFF的地址空间,映射到外部SDRAM,用于用户外扩随机存储器,以满足应用程序运行时的程序或数据存储需求;从0x90000000~0x9FFFFFFF 的地址空间,映射到外部Flash区域,用于存储用户程序;从0xF0000000以后的地址空间映射为EMIF控制寄存器。

访问0x80000000~0x8FFFFFFF 和0x90000000~0x9FFFFFFF 地址空间时,通过EM_CS0 和EM_CS1控制引脚,分别选通SDRAM 和FLASH 区域。C6727访问外设(不含SDRAM和FLASH,下同)的地址仅有A0~A11引脚12条,访问地址空间为4k。C6727通过配置行选通地址、列选通地址、存储区地址等EMIF相关的控制引脚,实现对SDRAM 8bit、16bit 或32bit 读写。访问Flash 地址空间可通过C6727 相关寄存器配置数据总线宽度为8bit或16bit,但有关的控制引脚仅EM_CS1、12条地址线和EM_BA0,无法满足当前主流Flash的256kbit(18条地址线)以上地址空间的访问需求,因而访问Flash时,需要借助UHPI的通用引脚,将其高位地址映射到C6727 通用引脚输出至Flash 高位地址线,从而实现对Flash的访问。

图1为C6727扩展SDRAM和Flash的典型连接方法[6]。在图1 中,设定Flash 的数据总线宽度为16bit。DSP 系统地址对应的数据总线宽度默认为8bit,读写数据总线宽度为16bit 的异步器件时,地址将以2 递进;同时,本文中采取了C6727 的BA[0]接入Flash 的A0引脚,这2个因素相当于地址总线左移2bit。因此,C6727分配的外设地址,映射到C6727地址总线A0~A11 的状态,需要右移2bit 才能与之引脚状态一一对应。这一问题易出错、易忽略,经常导致硬件调试失败,需要特别引起重视。

图1 C6727扩展SDRAM和FLASH的连接图Fig.1 Extended SDRAM and FLASH Interface for C6727

2 外围器件地址空间的设计与解析

SDRAM 区域的地址空间在程序运行时访问频繁,而Flash 地址空间仅在系统上电时程序搬移使用。因此,将外设地址配置在Flash 的地址空间。直接分配0x90000000~0x9FFFFFFF 地址空间会造成Flash和外设间地址重叠,因而需配置一条C6727通用引脚作为控制信号,通过CPLD逻辑译码电路,选通外围器件的片选信号,实现外设重叠地址空间的解析。

2.1 外设地址空间的设计

在访问Flash期间,需要通过UHPI引脚输出其高地址。由此,可通过另外配置的一条通用引脚作为开关信号,在其为低电平时,控制UHPI 引脚输出Flash高位地址;反之,则不输出Flash 高位地址,此时映射的地址空间为外设地址空间。按照这种设计思路,选择通用引脚AXR1[2]作为Flash 和外设地址空间的开关控制信号,重新分配后的地址空间如图2所示。

由此可见,CPLD译码逻辑电路,可根据AXR1[2]的状态,选择是否对外设地址空间译码。考虑到不同类外设对地址空间数量需求的不同,为确保系统设计的足够冗余,一般选择高位地址线作为外设的片选逻辑控制信号,低位地址线不做限制,这样即可确保外设具有足够的地址空间选择余量。本文以A8~A11共计4 条地址线,作为CPLD 的片选控制逻辑,结合AXR1[2]的状态,实现对外设片选信号的选通。外设带有地址线时,可用DSP 的地址总线直接接入外设。外设地址的最终确定,还与C6727配置的异步数据总线宽度、Flash 的A0 地址线是否接入C6727 的存储器选择区BA0 有关。以下分析说明几款典型需求对应的地址空间配置。

图2 地址映射分布图Fig.2 Address mapping distribution

2.1.1 通用串口控制器

通用异步串行通信(UART)作为一种灵活方便、简单可靠的通信方式,在各类嵌入式系统中应用广泛。TL16C752B 是TI 公司推出的新型通用异步串行通信协议芯片,可与TI 系列的DSP 直接接口。TL16C752B 有A、B 2 个通道,每个通道有16 个寄存器,寄存器之间的读写可通过线路状态寄存器LCR进行2次寻址。因此,每个通道只需分配8个地址,利用3 条地址线即可实现对TL16C752B 的完全控制[7-8]。假设A8~A11 的状态为“1010”时,TL16C752B 的A 通道被选通,B通道的分析与A通道类似,此处不做过多说明。C6727引脚状态及连接图如表1所示。

表1 TL16C752B接入C6727的管脚及连接分配Tab.1 Pins and collection distribution for the collecting TL16C752B to C6727

由于C6727 配置外设数据总线宽度为16bit 及BA0 接入Flash 的A0 引脚因素,生成的地址总线需要左移2bit,因而作为选通TL16C752B A 通道的基地址应该为0x90000A00(无关引脚取默认状态0)。首位9表示将地址映射到CE1 空间,使EM_CE1 有效。TL16C752B A通道的8个寄存器地址为:

表2 TL7528C接入C6727的管脚及连接分配Tab.2 Pins and collection distribution for the collecting TL7528C to C6727

2.1.2 D/A转换芯片

TL7528C是TI推出的专用D/A芯片,用于将数字信号高速转换为模拟信号输出,被广泛应用于接收信号数字AGC控制中。该芯片有A、B 2个通道,在其片选信号CS有效情况下,由其地址线A0控制选通A通道或B 通道;A、B 通道公用8 位的数据总线,可由C6727 的数据总线直接接入。同样,利用C6727 的A8~A11控制TL7528C的片选信号CS,C6727的A0管脚控制TL7528C 的A、B 通道。假设A8~A11 的状态为“1011”时,TL7528C 的片选信号有效,则其对应的引脚状态及连接图如表2所示。

因此,作为选通TL7528C 通道的基地址应该为0x90000D00。TL7528C A、B通道的地址分别为:

式(2)中:x=0 代表选通A 通道,x=1 代表选通B 通道。

按照以上方法,即可设计各类型外设的地址空间,在用户应用程序中可利用设计的地址值对外设进行读写操作。

2.2 重叠地址解析

为外设分配好地址空间后,需要利用CPLD 对采集的地址信号和C6727 的控制信号进行逻辑运算,输出外设的片选信号,从而实现对重叠地址的解析。重叠地址解析算法主要包括以下2个流程:

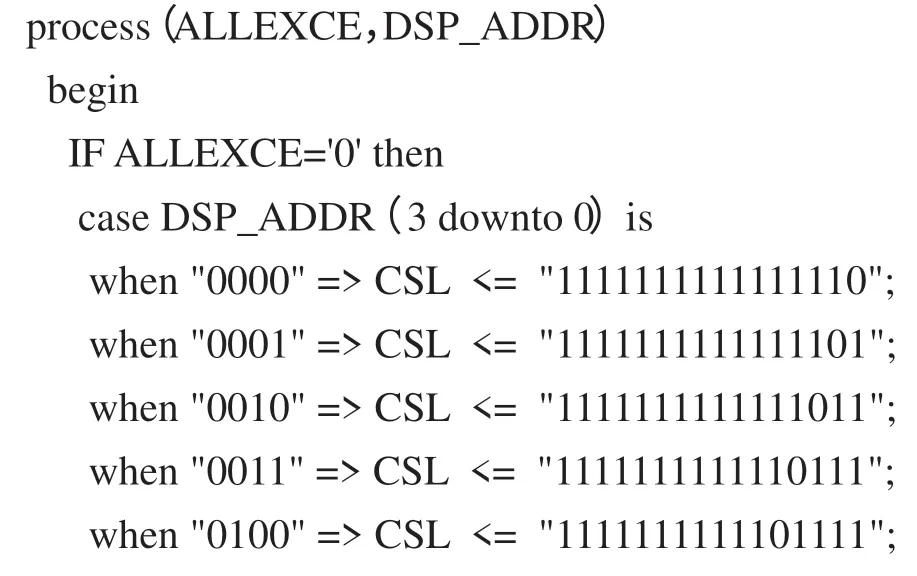

1)根据相关的控制信号,对控制地址A8~A11 和控制信号AXR1[2]、EM_CE1 进行译码。采用4-16 译码器实现相关的控制逻辑[9-12],对应的CPLD实现代码如下:

CSL 为定义的16 位信号向量,用于4-16 译码使用;ALLEXCE<=EM_CE1 or(NOT AXR1[2]),即在访问CE1地址空间、且访问外设空间(AXR1[2]=1)时,才执行以上代码;DSP_ADDR代表A8~A11 4条地址线,可输出16个外设的片选信号。如果外设数量多,可进一步增加译码的高位地址线。

2)对译码信号进行识别,选择合适的外设,输出其控制片选信号或其他类型信号。

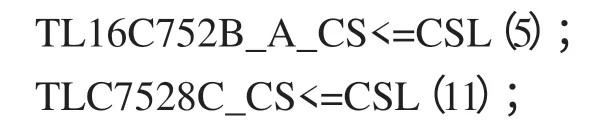

针对2.1中的地址分布,分别输出片选信号:

针对外接Flash,其高位地址信号输出为:

设Flash 高位地址输出允许的地址为0x9000800;SysRst 为系统复位信号,DSP_WEn 为对外设的写操作信号;对应的6条高位地址线与FA(5 DOWNTO 0)相连。

2.3 控制逻辑与访问程序的实现

用户的应用程序访问外设时,根据解析重叠地址要求,需要在程序中设定参数访问外设的条件控制、外设地址访问控制等,并在C6727数据总线上输出相关的读写信号。访问外设时要求设置AXR1[2]为高电平状态(默认情况下该管脚为低电平,表示不访问外设),可通过下述FlashEnable(unsigned char flag)函数实现,即在flag 为0 时,通过配置UHPI 中AXR1[2]引脚为通用类型输出引脚,并输出0,反之输出1,即可实现在AXR1[2]引脚上输出0或1。

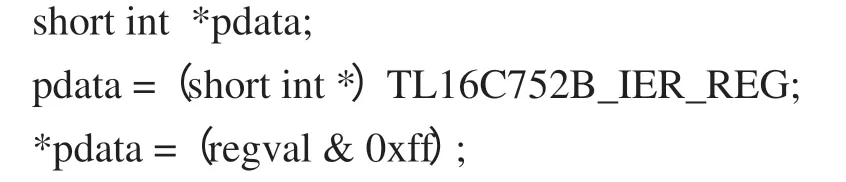

利用地址对外设进行访问时,可预定义需要访问的外设寄存器地址,并在该地址上输入或输出地址值。如预定义TL16C752B A 通道中断使能寄存器IER 的地址,对应TL16C752B 的A2~A0 状态为001 的代码为:

#define TL16C752B_IER_REG 0x90000A000+4

向IER写值regval时,先调用FlashEnable()函数,在AXR1[2]引脚上输出高电平,进而使用下列代码:

在向IER 赋值时,通过定义TL16C752B_IER_REG 指针在0x90000000 范围内,使得EM_CE1 有效;地址中的0xA00 使得TL16C752B A 通道片选信号有效,地址中的4 使得在C6727 的地址信号A2~A0 上输出001。此时,即达到访问TL16C752B A 通道的IER寄存器的条件,数据总线上的regval 值即送出达到IER 寄存中,实现了对IER 的写操作。对外设其他寄存器或端口的操作类似,本文不做过多说明。

3 结束语

通过在C6727 开发板上硬件测试,本文提出的重叠地址解析方法,可同时满足TL16C752B、TL7528C、LCD、外部开关状态信息采集或输出等需求,验证了本文提出的重叠地址解析实现外设访问控制方法的可行性。同时,针对外设数量多的问题,本文提出的该方法可进一步进行扩展,在降低外设寄存器或端口地址空间数量情况下,提高控制外设片选信号的宽度,提高控制外设的数量。当外设数量扩展到32 时,外设寄存器或端口地址空间可达128,对于工程应用而言,32 个外设控制和每个外设128个端口地址能满足各类复杂应用需求。

[1] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x CPU and instruction ser reference guide[K]. Texas:Texas Instruments,2006.

[2] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x DSP serial peripheral interface(SPI)reference guide[K].Texas:Texas Instruments,2006.

[3] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x DSP multichannel audio serial port(McASP)reference guide[K].Texas:Texas Instruments,2006.

[4] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x DSP dual data movement accelerator(dMAX)reference guide[K].Texas:Texas Instruments,2006.

[5] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x DSP software-programmable phase-locked loop(PLL)controller reference guide[K].Texas:Texas Instruments,2006.

[6] TEXAS INSTRUMENTS INCORPORATED. TMS320-C672x DSP external memory interface(EMIF)User's Guide[K].Texas:Texas Instruments,2006.

[7] TEXASINSTRUMENTSINCORPORATED.TL16C752B data sheet[K].Texas:Texas Instruments,2006.

[8] 刘伟,魏芹芹,王伟.TMS320C672x 系列DSP 原理与应用[M].北京:北京航空航天大学出版社,2008:398-405.

LIU WEI,WEI QINQIN,WANG WEI. Principle and application for TMS320C672x[M]. Beijing:Beihang University Presess,2008:398-405.(in Chinese)

[9] 张龙浩,祝怀标,谯艳.CPLD 和MSP430 单片机在导波雷达物位计中的应用[J].电子设计工程,2012,20(21):142-144.

ZHANG LONGHAO,ZHU HUAIBIAO,QIAN YAN.Application of CPLD and MSP430 MCU in guided wave radar level meter[J]. Electronic Design Engineering,2012,20(21):142-144.(in Chinese)

[10]张艳梅,苟锐锋,杨晓平,等.DSP+CPLD在级联H桥配电网静止同步补偿器的应用[J].南方电网技术,2012,6(6):74-76.

ZHANG YANMEI,GOU RUIFENG,YANG XIAOPING,et al.The application of DSP+ CPLD in static synchronous compensator of cascade H bridge contribution network[J]. Southern Power System Technology,2012,6(6):74-76.(in Chinese)

[11]董超,朱军,史勃.DSP 人机接口技术研究[J].机械设计与制造,2012(11):174-176.

DONG CHAO,ZHU JUN,SHI BO. Research on DSP HMI technology[J]. Machinery Design & Manufacture,2012(11):174-176.(in Chinese)

[12]窦亚力,徐向前,张公全,等.基于ARM9+CPLD的嵌入式数据采集系统在PFN 中的应用[J]. 电子测量技术,2012,35(12):81-86.

DOU YALI,XU XIANGQIAN,ZHANG GONGQUAN,et al.Application of an embedded data acquisition system based on ARM9 plus CPLD in PFN[J]. Electronic Measurement Technology,2012,35(12):81-86.(in Chinese)