暂态过电压预处理对氧化锌压敏电阻冲击性能的影响

2014-03-22杨天琦周北平

张 欣,杨天琦,周北平

(1.南京信息工程大学 江苏省气象灾害预报预警与评估协同创新中心,江苏南京 210044;2.南京信息工程大学 中国气象局气溶胶与云降水重点开放实验室,江苏南京 210044;3.南京市气象局南京市气象服务中心,江苏南京 210009;4.南京信息工程大学大气科学学院,江苏南京 210044)

0 引言

在现代防雷减灾工作中,电涌保护器(Surge protection device,SPD)的重要性已被人们认识[1-6]。其中,MOV型SPD因其良好的非线性特性,被广泛运用在智能电网及电气电子电路等电涌防护中。实际工作中,MOV芯片在遭受雷电等过电压冲击后,耐冲击性能会随着冲击电流幅值增大、冲击次数增加而下降,因此,对MOV芯片冲击性能的研究备受关注。[7-10]

目前,对于MOV冲击老化劣化方面的研究多基于实验分析静态参数变化过程,研究认为:MOV芯片在冲击电流作用下,压敏电压U1mA呈先上升后下降的趋势,上升的幅度小于下降的幅度,漏电流IL呈线性增长的趋势[11-12];非线性系数α随劣化程度的增加而呈下降趋势,标称电流In冲击下,α值随冲击次数近线性下降[10]。而SPD接入电路中会遭受工频过电压入侵,暂态过电压对于MOV冲击性能的影响,也是目前MOV冲击老化劣化研究热点之一。

文献[13]指出,由于负荷不对称,中性线断线,低压接地故障引起的暂态过电压一般持续时间不超过5 s,在电网中发生的概率很高,过电压持续作用下SPD会发热,温度不断升高会导致MOV发生热熔穿,产生永久性破坏[14],但未提及持续5 s的暂态过电压作用后MOV试样特性变化。文献[15]发现,MOV型SPD具有一定的暂时过电压耐受能力,耐受时间与预期短路电流有关,预期短路电流越大,耐受时间越短,超过耐受时间后SPD会被击穿,击穿时伴随电弧出现,可能引起火灾。庞弛[16]等研究了工频过电压老化对MOV芯片8/20 μs冲击特性影响,指出经不同幅值过电压老化15 min后,MOV芯片通流能力呈现不同程度的下降,但工频过电压老化时间较长,与实际MOV工作环境中可能遭受的暂态过电压有一定区别。

基于MOV芯片实际工作环境,文中设计暂态过电压预处理后MOV芯片冲击性能影响试验,分析试验数据,结合双肖特基势垒导电理论,研究遭受暂态过电压后对MOV芯片冲击性能的影响。

1 MOV芯片冲击性能影响试验

为研究MOV芯片实际工作环境中遭受暂态过电压对其冲击性能影响,设计MOV暂态过电压预处理后冲击试验。MOV实际工作电路中,因操作和故障等原因造成的暂态过电压多为瞬时工频过电压,所以文中采用工频恒定交流过电压模拟实验。

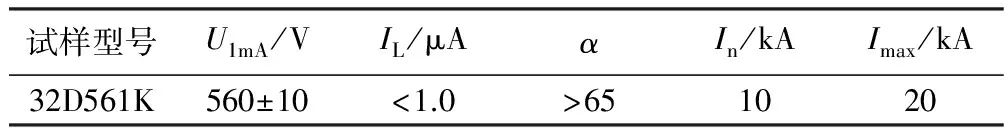

试验选用18片同厂家同型号MOV芯片作为试样,每3片试样为一小组,分别为A1组、B1组、A2组、B2组、A3组、B3组。试验前逐一测得每一试样静态参数。其中MOV芯片压敏电压、漏电流和非线性系数可用压敏电压直流参数仪测得,标称电流和最大放电电流由厂家标示,如表1所示。

表1 试样静态参数

试验过程中,室温控制在恒定25 ℃.利用工频交流恒压源设备产生450 V和470 V工频恒定交流过电压对试样进行暂态过电压预处理,即在A2组、B2组MOV芯片两端施加450 V过电压5 s,A3组、B3组试样施加470 V过电压5 s.A1组、B1组为对比样,不经过暂态过电压预处理。

暂态过电压预处理后,待试样冷却至室温再次测量记录每一试样静态参数。采用20 kA多波形发生器设备产生8/20 μs冲击波形对所有试样分别进行不同幅值的冲击老化,A1组、A2组、A3组试样冲击8/20 μs 电流波10 kA,B1组、B2组、B3组冲击8/20 μs电流波15 kA.每次冲击后待试样冷却至室温,记录静态参数后再进行下一次冲击,直至试样压敏电压跌落10%以上,漏电流大于20 μA为止,证明该试样已发生冲击损坏。

2 试验数据分析

将试验过程中每一组芯片数据取平均值,得到暂态过电压预处理前后,每组MOV芯片静态参数如表2所示。

表2 试样暂态过电压预处理前后静态参数对比

从表2中可看出,试样经暂态过电压预处理5s后静态参数发生变化,其中A2、B2、A3、B3组试样压敏电压均比施压前增大,且大于未施压的A1、B1组试样,漏电流几乎不变,非线性系数较小幅度下降。施加470 V过电压的A3、B3组试样压敏电压均比施加450 V过电压的A2、B2组试样略高。

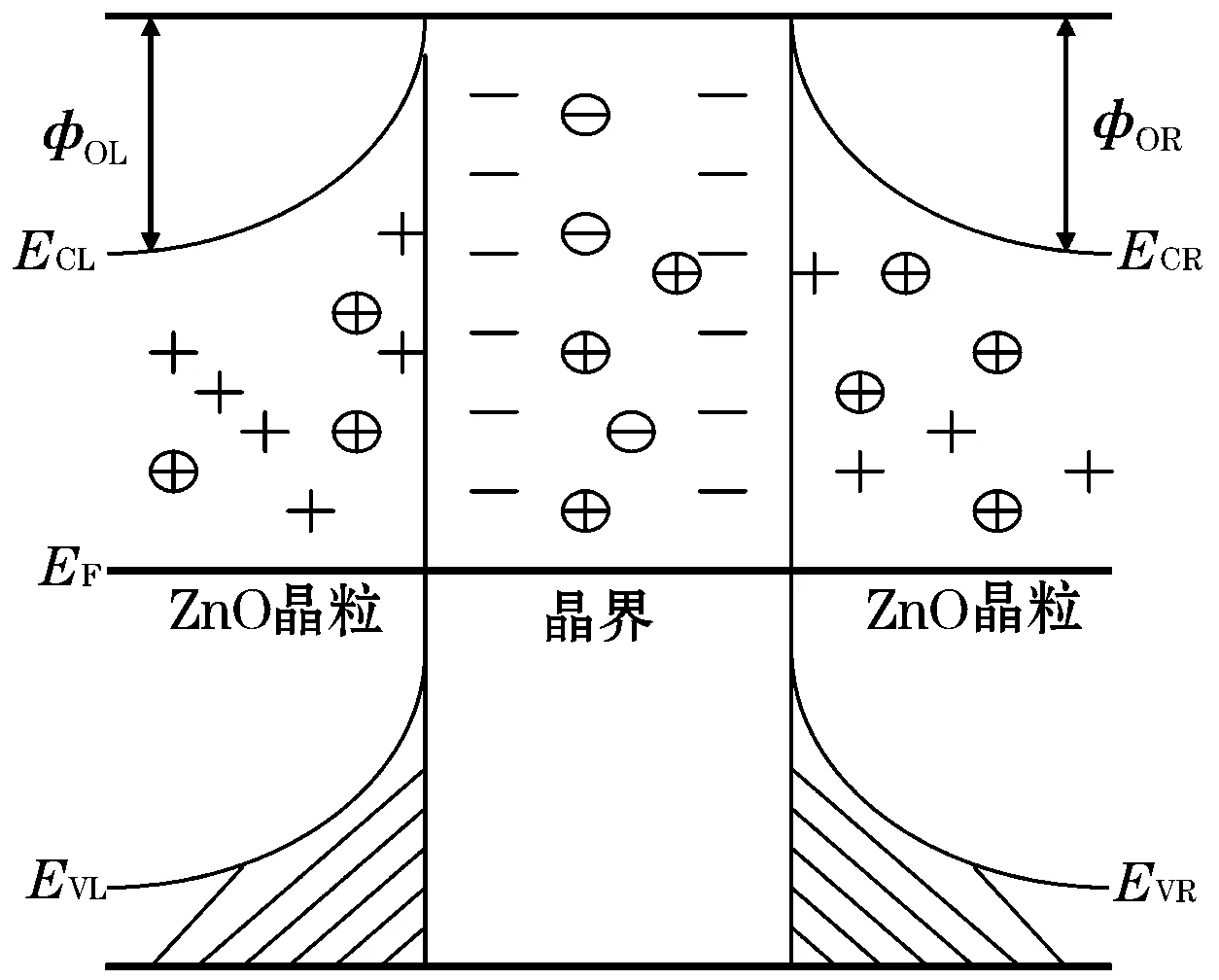

从MOV导电机理[12,17-19]分析可知,MOV芯片在高温烧结过程中产生晶粒-晶界-晶粒的微观结构,形成双肖特基势垒[20]。如图1(a)所示,晶粒和晶界费米能级不同,N型半导体氧化锌晶粒费米能级EFG高于非N型晶界费米能EFB,使得晶粒中自由电子流向晶界,在晶界和晶粒的交界面上被受主表面态俘获,形成大量的带负电的界面电荷,而晶粒表面失去自由电子后从电中性变成带正电。晶粒内部自由电子在热运动作用下向晶粒表面移动,使晶粒表面达电中性。而内部注入电子又会被晶界表面态俘获,直至晶界负电荷与晶粒正电荷达到平衡为止,此时晶粒与晶界费米能级相等,形成了晶界两侧的双肖特基势垒高度φ0,如图1(b)所示。未加压时,晶界两侧双肖特基势垒为对称分布,势垒高度决定MOV芯片非线性特性。当对MOV芯片施加直流电压时[21],如图1(c)所示。

(a)未结合前能带图

(b)结合后零偏压时能带图

(c)直流电压作用后能带图

图1(c)中,左侧肖特基势垒φOL正偏,右侧肖特基势垒φOR反偏,电压主要施加在反向肖特基势垒上,正向肖特基势垒高度不变,反向肖特基势垒高度增加。若长时间直流电作用,反偏侧晶粒中正电荷向左移动,与晶界右侧界面负电荷发生电中和,减少表面态密度,降低势垒高度。

试验中施加在MOV芯片两端过电压时间较短,且采用工频交流电压,可认为交流电短时间作用下,ZnO晶粒左右两侧肖特基势垒交替处于反偏状态,双势垒高度均增加,可致暂态过电压预处理后,MOV芯片压敏电压升高,非线性变好。

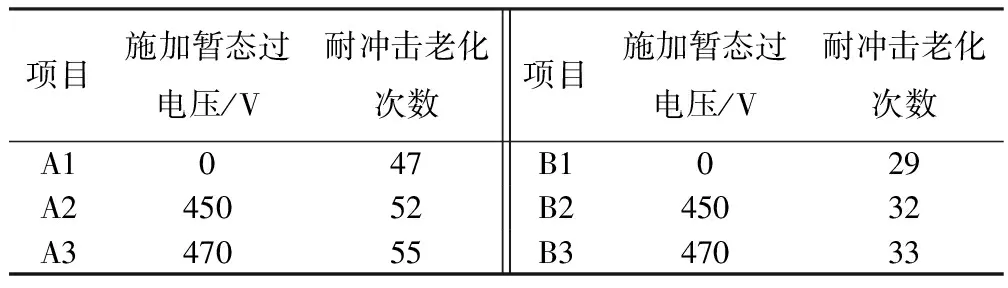

不同幅值暂态过电压预处理后,MOV耐冲击老化过程静态参数变化不同,且耐冲击次数也不同。如表3所示。

表3 试样经不同幅值暂态过电压预处理后耐冲击老化次数

表3中,不同幅值暂态过电压预处理后的MOV芯片耐受冲击老化次数比未经暂态过电压预处理的芯片多,耐冲击性能好。同样冲击10 kA幅值8/20 μs 电流波,A2、A3组试样耐冲击老化次数多于A1组试样,其中施加暂态过电压470 V的A3组试样耐冲击老化55次,多于施压450 V的A2组试样。冲击15 kA幅值8/20 μs 电流波的B1、B2、B3组试样,得到的数据分析结果同样遵循此规律。由此可以看出,经过暂态过电压预处理后MOV芯片冲击性能变好,且施加470 V暂态过电压预处理MOV芯片冲击性能略好于施加450 V过电压的芯片。可证明对工频交流暂态过电压预处理后,MOV芯片势垒高度变高,非线性变好的推断是合理的。

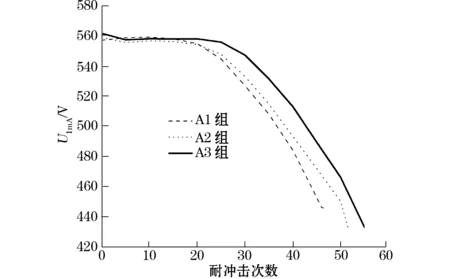

MOV芯片未施加暂态过电压和施加不同幅值暂态过电压后,冲击不同幅值8/20 μs电流波,压敏电压变化趋势也不同,如图2、图3所示。图2为A1组、A2组、A3组试样冲击10kA幅值8/20 μs电流波压敏电压随冲击次数变化关系图。

图2 A1组、A2组、A3组试样冲击8/20 μs 电流波压敏电压变化趋势

从图2中可以看出,施加暂态过电压的A2组、A3组试样冲击初始阶段压敏电压较未施压的A1组试样高,冲击过程中,A2组、A3组试样压敏电压呈现下降-保持-下降的趋势,A1组试样压敏电压呈现上升-下降趋势,且上升幅度很小,没有保持阶段,致使整个耐冲击阶段,A1组试样压敏电压下降速率大于A2组和A3组,耐冲击特性较A2组和A3组略差。

图3为B1组、B2组、B3组试样冲击15 kA幅值8/20 μs 电流波压敏电压随冲击次数变化关系图,图中所反映出来的变化规律与图2相符合。

图3 B1组、B2组、B3组试样冲击8/20 μs 电流波压敏电压变化趋势

3 结论

MOV芯片实际制造过程中,某些厂家在芯片出厂前会进行“预老化”处理,可提升MOV性能。文中采用暂态过电压预处理MOV芯片,由试验数据分析可证明,暂态过电压预处理后芯片冲击性能有所提升,与实际制造工艺相符合。

MOV芯片受暂态过电压预处理后,微观电气特性和宏观耐冲击特性发生改变。不同幅值暂态过电压预处理对芯片冲击性能影响不同。研究表明:

(1)MOV芯片耐受暂态过电压5 s后压敏电压会升高,冲击性能会变好,耐8/20 μs 电流波冲击次数多于未施压芯片。

(2)MOV芯片耐受470 V暂态过电压预处理后,冲击性能好于耐受450 V过电压芯片。

(3)利用双肖特基势垒导电机理分析工频交流暂态过电压瞬时作用下,晶界两侧势垒均升高,非线性变好,并由试验验证此推论的合理性。

(4)暂态过电压预处理后MOV芯片耐8/20 μs 电流波冲击过程中压敏电压呈现下降-保持-下降过程,与未施压芯片压敏电压变化过程有所不同。

参考文献:

[1]AMICUCCI G L,FIAMINGO F,FLISOWSKI Z,et al.Surge protective devices for low voltage systems:practical approach for the protection distance evaluation.Power Tech,2007 IEEE Lausanne.IEEE,2007:778-782.

[2]MANSOOR A,MARTAZLOFF F.The effect of neutral earthing practices on lightningcurrent dispersion in a low-voltage installation.Power Delivery,IEEE Transactions on,1998,13(3):783-792.

[3]秉钧.金属氧化物避雷器.北京:水利电力出版社,1993.

[4]DRABKIN M M.Surge protection of low-voltage AC power by MOV-based SPDs.Harmonics and Quality of Power.10th International Conference on.IEEE,2002,1:13-16.

[5]任晓明,蔡振新,傅正财.低压电涌保护器暂态过电压测试方法研究.高压电器,2007,43(4):248-249.

[6]张南法.电涌保护器应用中几个问题的探讨.低压电器,2002 (4):9-13.

[7]尹桂来,李建英,尧广,等.ZnO压敏陶瓷冲击老化的电子陷阱过程研究.物理学报,2010,59(9):6345-6350.

[8]章天金,周东祥.低压 ZnO 压敏陶瓷冲击老化特性.电子元件与材料,1999,18(4):18-19.

[9]李慧峰,王士良,许毓春,等.氧化锌非线性电阻冲击老化机理的研究.中国电机工程学报,1993(13):25-31.

[10]杨仲江,张枨,柴健,等.氧化锌压敏电阻老化过程中非线性系数变化的研究.电子元件与材料,2011,30(9):27-30.

[11]师正,谭涌波,柴健,等.MOV压敏电阻静态参数变化的特征分析.电瓷避雷器,2012(5):59-63.

[12]商鹏.氧化锌压敏电阻特性的研究:[学位论文].南京:南京信息工程大学,2012.

[13]应达,肖稳安,赵军,等.工频过电压对压敏电阻影响的实验研究.电瓷避雷器,2012(6):71-75.

[14]杨仲江,李强,张枨,等.MOV 在交直流电压下耐受能力的试验研究.电瓷避雷器,2013(6):42-47.

[15]李晓明,尹天文,王碧云.暂时过电压威胁 SPD 安全使用的分析.低压电器,2009(24):37-40.

[16]庞驰,叶萃,费自豪,等.ZnO压敏防雷芯片工频耐受与通流能力的相关性.电子元件与材料,2011,30(6):26-28.

[17]何金良,刘俊,胡军,等.电力系统避雷器用ZnO压敏电阻研究进展.高电压技术,2011,37(3):634-643.

[18]张郴莉.双脉冲电流作用下氧化锌电阻冲击老化破坏机理的研究:[学位论文].北京:中国科学院电工研究所,2001.

[19]WOKTERS D R,SEHOOT J V.Kinetics of charge trapping in duekeetries .J ApplPhys,1985,58(2):831-837.

[20]吴维韩,何金良,高玉明.金属氧化物非线性电阻特性和应用.北京:清华大学出版社,1998.

[21]刘俊,何金良,胡军,等.ZnO压敏电阻老化机理的研究进展.电工电能新技术,2010,29(3):63-67.