一种适于FPGA芯片的SRAM单元及外围电路设计

2014-02-26徐新宇徐玉婷林斗勋

徐新宇,徐玉婷,林斗勋

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

目前,现场可编程门阵列(FPGA)被广泛用于数字系统,而FPGA产品大多基于静态存储单元SRAM技术,通过采用SRAM单元阵列来存储编程位,并由存放在SRAM中的程序来设置FPGA的工作状态。

标准SRAM单元主要有三种结构:四管加TFT负载单元、四管加多晶负载单元和六管单元。其中采用六管单元设计的静态存储器生产工艺由于与CMOS工艺兼容性好,按比例缩小后其面积与多晶负载四管单元相当,在超大规模静态存储器设计中已被广泛使用。

我们分析静态存储器六管单元的漏电原理,采用国内某工艺线提供的40 nm的SPICE模型,对六管单元进行了仿真,设计完成SRAM单元以及其读写电路,并为静态存储器六管单元编写了verilog语言描述的行为模型,用于FPGA芯片中大规模静态存储器的仿真验证。

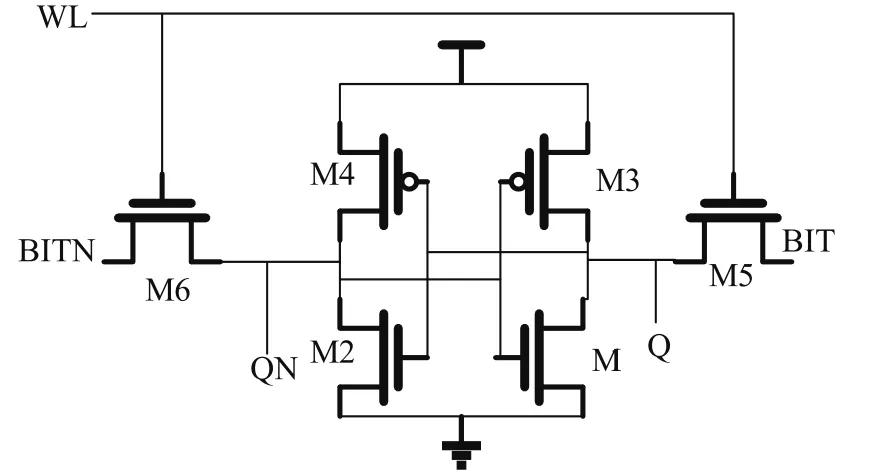

2 静态存储器SRAM单元静态电流分析

图1为六管结构SRAM单元。两个PMOS管M3和M4是负载管,主要是用来补偿存储管和开关管的漏端电荷的泄放。与M3和M4构成反相器对的两个NMOS管M1和M2是存储管,数据和数据的反分别存放在Q和QN点。而栅极与字线(WL)相连的两个NMOS管M5和M6起开关的作用,BIT和BITN为两条位线。

图1 SRAM六管结构图

以写“1”为例来说明SRAM的写过程。首先译码电路选中特定的存储单元,然后使写使能信号有效,将要写入的数据“1”通过写入电路变成了“1”和“0”后分别加到选中单元的两条位线BIT和BITN上,此时选中存储单元中的WL=“1”,晶体管M5和M6打开,把BIT和BITN上的信号分别传送到Q和QN点,从而使Q=“1”,QN=“0”,这样数据“1”就被锁存在晶体管M1、M2、M3和M4所构成的锁存器中。写入数据“0”的过程与此类似。

以读“1”为例来说明SRAM的读过程。读“1”时,首先预充电信号将BIT和BITN上拉,对BL和BL进行预充电,一般预充到电源电压VDD,主要是为了防止发生误操作。预充电后再通过行译码器选中某行,则某一存储单元被选定,即WL选通。此时,由于其中存放的是“1”,Q=1,晶体管M2和M6导通,有电流经过M2和M6到地,从而使BITN电位降低,BIT和BITN间产生电压差;当电压差增大到一定的程度后,打开灵敏放大器,对BIT和BITN间的电压差进行放大;最后再将灵敏放大器的输出接到三态输出驱动器上,驱动器的输出就是被读出的数据,完成了整个读过程。

由于工艺进入40 nm后,SRAM的漏电流将大大增加,从而产生存储器功耗的问题。而六管结构的SRAM单元在设计上没有结构性的静态电流,其静态电流主要取决于工艺。而且在电路待机状态下,通常将BIT和BITN设置为高电平状态,因此整个静态存储器的待机电流是由于MOS管的亚阈值电流引起的。

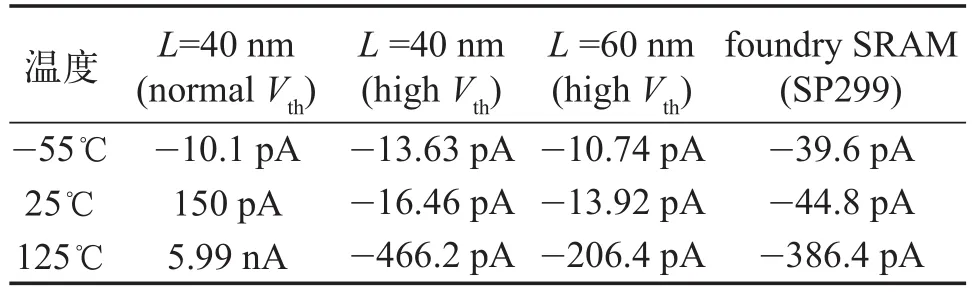

为了改善静态存储器的漏电流,我们采用高阈值晶体管替代普通晶体管设计完成SRAM单元设计,同时晶体管的W/L满足SRAM设计的两个基本条件,即数据读取操作不破坏存储单元存储的信息和在数据写入过程中存储单元应该允许存储信息的改变。采用不同阈值和沟长的MOS管构造的SRAM单元的漏电电流仿真结果如表1所示。

表1 SRAM单元待机电流仿真

从仿真结果可以看出,与沟长为40 nm(最小沟长)的MOS管相比,采用沟长为60 nm的MOS管构造的SRAM单元,其待机电流将减小一半左右。而且在版图实现时,并不会大幅影响SRAM单元的面积。因此,将SRAM单元中MOS管的沟长修改为60 nm。

3 静态存储器单元的外围读写电路设计

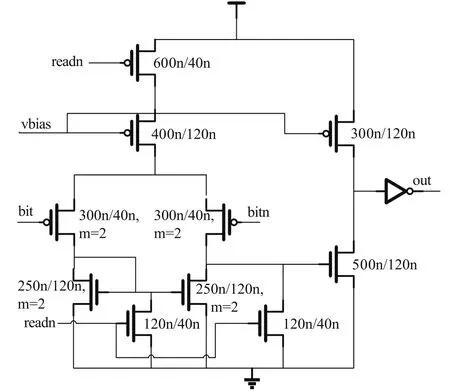

SRAM的外围电路一般包括灵敏放大器、地址译码器、三态输入/输出缓冲器和控制逻辑等。灵敏放大器是静态存储器外围读写控制电路的关键部件。它对整个存储电路的性能有着极其重要的影响。由于存储单元的器件充放电能力较弱,而它与连接的位线的电容较大,当对电路进行读操作时,单元较弱的导电能力使位线的电压摆幅很小,并且要使位线达到能拉动数字器件的摆幅需要很长的时间。因此,在位线的读出输出级必须设置灵敏放大器,加快电路的读出速度。即当读信号开始、被选中单元的传输管打开以后,存储单元对位线放电(一般情况下,位线都会被预充到某一电平,读出的过程是对单边位线的放电过程)。当位线的电压达到一定的摆幅,通常在几百毫伏之内时,就可以启动灵敏放大器,将位线上的小摆幅电平迅速放大到逻辑电平“1”或“0”,送出到输入端口。本文设计的灵敏放大器的结构如图2所示,在读信号readn为低电平有效时,灵敏放大器正常工作。

图2 灵敏放大器电路图

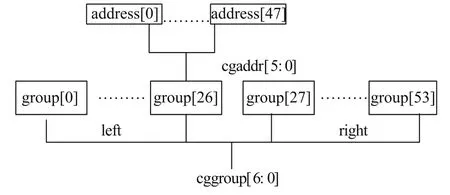

外围电路中另一个重要的部件就是地址译码器。由于我们设计了3232行、1296×2列SRAM,地址线总线控制,数据线横向控制,因此需要产生1296×2个地址,每个地址控制一列SRAM传输管的开启。地址译码器的结构如图3所示。

图3 地址译码示意图

由图3可以看出,在地址译码电路里采用了级联的方式。首先由分组地址cggroup[6]确定左右,cggroup[5:0]译码可以产生26=64个地址,此处采用前26个地址。每个group里又包含48个小地址,由cgaddr[5:0]译码产生。

4 实现及仿真

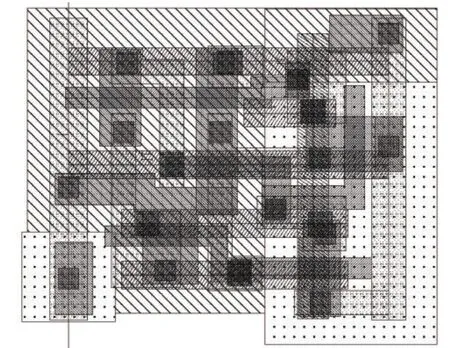

SRAM单元的实现版图如图4所示,单个SRAM单元的面积约为0.73 μm2。

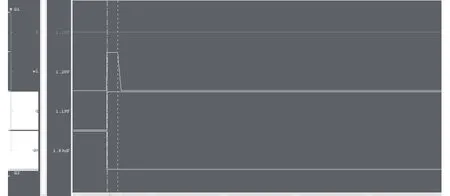

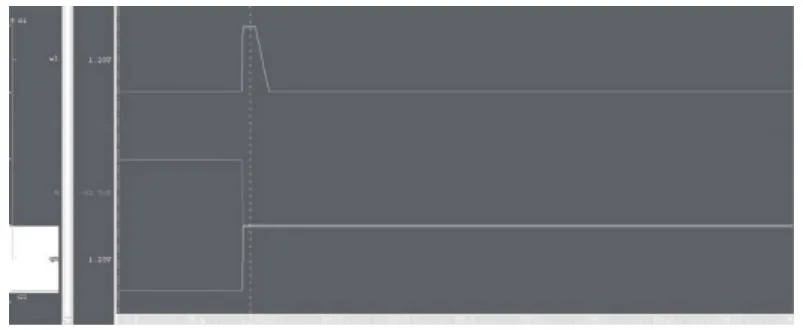

为了验证单个SRAM单元工作的正确性,本文采用40 nm工艺SPICE模型和1.1 V电源电压进行仿真。图5和图6表示写操作1和写操作0时的波形,图7和图8表示读操作1和读操作0时的波形。

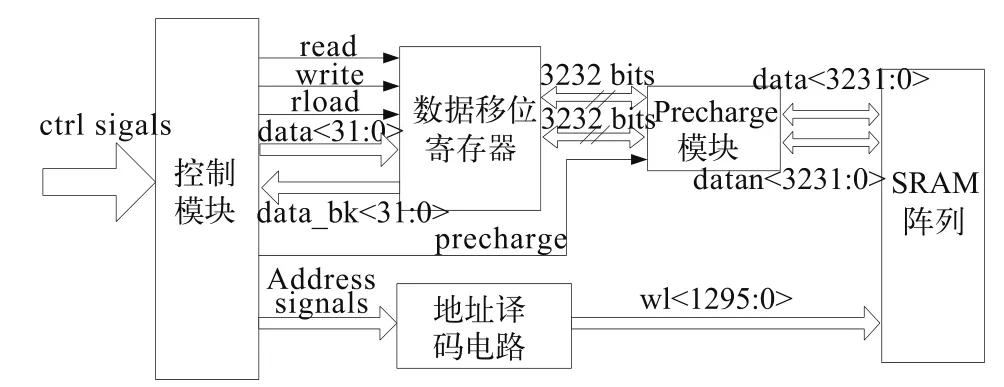

基于SRAM阵列,我们设计的整个电路功能模块如图9所示。控制模块负责产生电路所需的各类控制信号。数据移位寄存器将控制模块送出的32位数据进行移位,形成3232位数据,在数据线上准备好。当写信号有效时,precharge信号无效,地址译码器将地址信号进行译码,将某列SRAM的WL线打开,将数据线上的数据写入SRAM。写操作完成后,precharge信号有效,将SRAM的data和datan拉高。当读操作有效时,precharge信号无效,地址译码器将地址信号进行译码,将某列SRAM的WL线打开,将该列SRAM中存储的数据读出,再通过移位寄存器返回控制模块。读操作完成后,precharge信号有效,将SRAM的data和datan拉高。

图4 SRAM实现版图

图5 写“1”仿真波形

图6 写“0”仿真波形

图7 读“1”仿真波形

图8 读“0”仿真波形

图9 电路简化模块图

由于电路的规模比较大,而且涉及的模拟单元比较多,为了方便整体电路功能的仿真验证,我们为所有的模拟单元编写了用verilog语言描述的行为级模型。其中在SRAM的行为描述中,为了读写数据的不冲突,将BIT和BITN设置成了弱驱动。

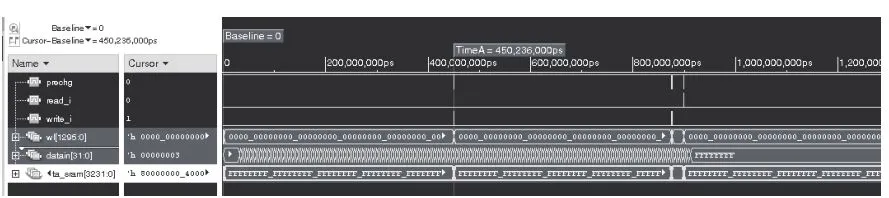

我们采用JTAG模式对电路输入32位数据,分别对两列SRAM进行读/写操作,NC-verilog仿真波形如图10所示。

图10 整体电路仿真波形

5 结束语

我们根据foundry提供的40 nm工艺的NMOS、PMOS管的SPICE模型,分别对采用不同阈值的MOS管构造静态存储器SRAM产生的待机漏电电流进行了仿真比较,提出了一种采用高阈值MOS管的漏电电流较小的SRAM单元结构,并设计完成了读写控制电路以及地址译码电路,同时为了大规模电路仿真和验证的需求,为SRAM单元以及相关模拟电路用verilog语言编写了行为模型,完成了整体电路的仿真。

[1] 王媛媛,王子欧,张立军. 一种适用于小尺寸工艺的SRAM单元设计[J]. 苏州大学学报,2012,32(3):51-55.

[2] SteevinckE, List FJ. Static-noise margin analysis of MOS SRAM cells[J]. IEEE JSSC,1987, 22(5): 748-754.

[3] MoshovosA,FalsafiB,NajmFN,et al. A case for asymmetriccell cache memories[J]. IEEE Transactions on Very Large Scale Integration System, 2005, 13(7): 877-811.