基于FPGA硬核的PCI Express实现

2014-02-10何春茂

何春茂

(广州锐达测控科技有限公司,广东广州 510385)

基于FPGA硬核的PCI Express实现

何春茂

(广州锐达测控科技有限公司,广东广州 510385)

PCI Express速度快,性能稳定,广泛使用于计算机与外围设备的通信。根据PC平台的运动控制器要求,采用Altera公司的EP4CGX30的硬核,实现PC机与DSP之间的通信,通过FPGA内部自带的RAM,采用FIFO的方式,实现全双工通信,满足DSP与PC的通信要求。

FPGA;PCI Express;硬核

0 引言

目前,PC平台的运动控制卡应用上,大多采用了PCI的通信方式,如雷赛科技公司的MDC1380、MDC1410等,固高科技公司的GE-200-SV-PCI、GE-300-SG-PCI等。PCI总线时钟频率为33.3 MHz/66 MHz,最大数据传输速率为133 Mb/s,能满足大多数PC平台的运动控制器的通信需求。对于通信速度要求更快只需要采用PCI Express总线进行通信。PCI Express总线是一种完全不同于过去PCI总线的一种全新总线规范,与PCI总线共享并行架构相比,PCI Express总线是一种点对点串行连接的设备连接方式,点对点意味着每一个PCI Express设备都拥有自己独立的数据连接,各个设备之间并发的数据传输互不影响,而对于过去PCI那种共享总线方式,PCI总线上只能有一个设备进行通信,一旦PCI总线上挂接的设备增多,每个设备的实际传输速率就会下降,性能得不到保证。PCI Express总线有X1、X2、X4、X8、X16、X32通道规格。现在已经发展到了PCI-E 3.0。由于受限于FPGA器件的支持,本文使用了PCI-E 2.0规范。支持最大频率为2.5 GHz,最大传输速度为512 Mb/s(双工)。

1 硬件平台

本文采用了Altera公司的Cyclone IV系列器件EP4CGX30F23,属于低成本、低功耗FPGA。该器件有29 440个逻辑单元,1.08Mbits内嵌Memory模块,290个最大I/O接口。同时,采用了Altera成熟的GX收发器技术,具有出众的抖动性能和优异的信号完整性。PCI-SIG兼容收发器型号支持多种串行协议,支持2.5 GHz的收发频率。FPGA实现PCI Express通信、伺服驱动器的控制及各信号的采集与输出。

DSP采用的是TI公司的TMS320C6713,它是32位高速浮点型DSP,时钟最高频率为300 MHz,通过EMIF总线的方式和FPGA通信。DSP用来完成运动控制运算,硬件如图1所示。

图1 硬件平台

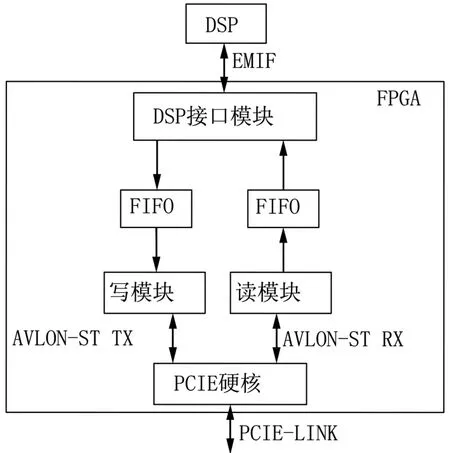

2 数据流程

PCI Express体系结果分为四个层,分别为:物理层(Physical layer)、数据链路层(Link Lay⁃er)、处理层(Transaction Layer)、软件层(Soft⁃ware Layer),其中,物理层、数据链路层及处理层已经包含在硬核中,用户要实现的就是软件层。如图2中的读模块和写模块。PC端发送数据下来时,通过读模块,把接收到的数据放处FIFO,当DSP通过EMIF总线检测到FIFO内部有数据时,就可以从FIFO中读出数据。当DSP需要上传数据时,也通过EMIF总线把数据写到FIFO,当写模块检测到FIFO有数据时,就通过AVLON-ST TX总线把数据打包传输给硬核,完成数据的通信流程。如图2所示。

图2 数据流程

3 硬核使用

3.1 硬核的生成

在quartus工程内,点击工具菜单下面Mega⁃wizard Plug-In Manager,选择IP Compiler for PCI Express。在System Settings菜单下,选择Hard IP For PCI Express,Lanes选择通道,该器件最大支持x4通道,本文选择x1,Port Type框内选择Na⁃tive EndPoint,作为终端设备。PC机输入的差分参考时钟Xcvr ref_clk选择100 MHz,Application clock(应用时钟频率)为125 MHz。点击下一步进入PCI resisters配置。在配置空间里,默认选择一个64-bit Prefetchable memory,也可以开通多个存储空间或I/O空间。PCI Read-only Registers是PC端对目标设备身份进行识别寄存器,可以选择默认,也可以更改。如图4所示。点击Next进入PCI Capabilities设置,默认四条MSI中断线。后面的配置选择默认即可,最后点击Finish,生成PCI Express硬核文件。

3.2 硬核关键信号说明

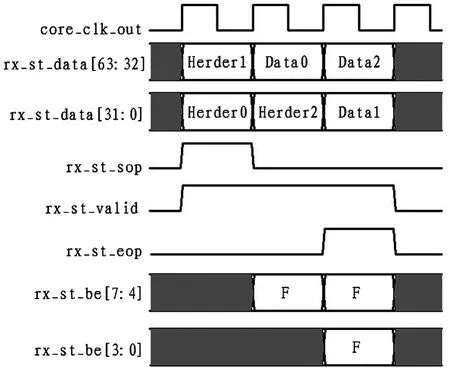

Avalon-ST RX组:即在读模块内完成这个功能。时序如图3[1]所示。在rx_st_sop高电平时,即表读时序开始,读第一个数据,开始读取数据,rx_st_eop高电平处读取最后一个数据,即完成数据读取,rx_st_valid高电平表示数据有效。

图3 Avalon-ST RX时序

Avalon-ST TX组:在写模块内完成这个功能,时序如图4[1]所示。在core_clk_out上升沿处,把tx_st_sop置高,并写入第一个数据,同时把tx_st_valid置高,中间数据在tx_st_valid置高时输入有效,最后一个数据写入并把tx_st_eop置高。完成一帧数据的发送。

图4 Avalon-ST TX时序

Clock组 : 这 组 包 括 refclk、 pld_clk、core_clk_out、 pclk_in、 app_clk、 cal_blk_clk、clk250_out、clk500_out、fixedclk_serdes、recon⁃fig_clk等。其中refclk为输入信号,与配置的ref_clk一至,由 PC端提供,core_clk_out、app_clk、clk250_out、clk500_out为硬核输出时钟,供应用层使用,core_clk_out用于发送接收模块, app_clk用 于 中断 模 块。 pld_clk由core_clk_out驱动,保持应用层时钟与硬核时钟一至。pclk_in为仿真时钟,连接到 refclk。cal_blk_clk为发送基准时钟,连接至core_clk_out。reconfig_clk,serdes、分别为固定的50 M、125 M时钟,必须于外部时钟驱动,可用PLL锁相环产生50 M和125 M的时钟来驱动。

Reset组:这组包括crst、npor、srst。crst为同步配置复位,高电平有效,可由pcie_rstn(pcie插槽复位引脚)和local_rstn(硬件复位引脚)逻辑与之后再取反得到的信号来驱动。npor为异步上电复位,低电平有效,可local_rstn来驱动。Srst为同步数据通路复位,高电平有效,可由lo⁃cal_rstn取反后来驱动。

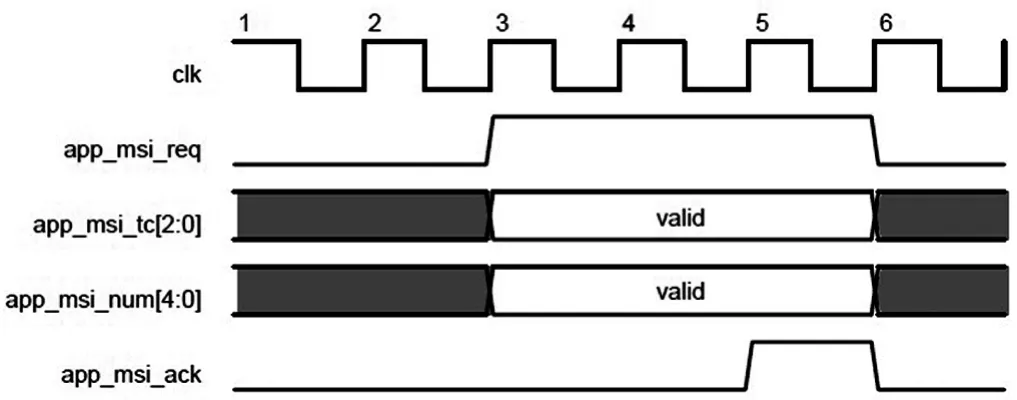

Interrupt组。这组由上层中断应用模块来驱动。可产生MSI Interrupts和Legacy Interrupt二种中断。其中MSI Interrupts如图5[1]所示。在app_mis_req高电平下,写入app_mis_tc和 pp_msi_num,当硬核承认信号app_msi_ack为高时,将产生一个MSI报文向处理器申请中断,完成MSI中断操作。

图5 MSI Interrupt

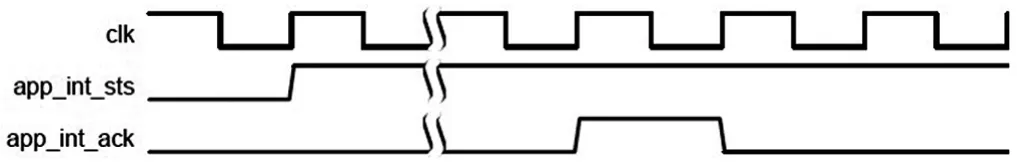

Legacy Interrupt操作时序如图6[1]所示。将app_int_sts信号置高,然后等待app_int_ack变高,即产生一个Assert_INTA信息报文向处理器申请中断。

图6 Legacy Interrupt

其他信号组用户可以根据需要进行选择使用。

4 PCI Express通信报文

PCI Express硬核已经生成了数据链路层和处理层,用户只需要完成应用层,即完成接收、发送及中断等模块。PCI Express通信报文有内存读、内存写、配置读、配置写、I/O读、I/O写、信息、完成等报文。而作为终端设备,接收到PC端发送的内存读报文后,需要返回完成报文,当收到内存写报文时,则无需返回报文。报文是按一定格式进行填充或读取,其中内存读报文格式如图7[2]所示。

图7 读内存报文

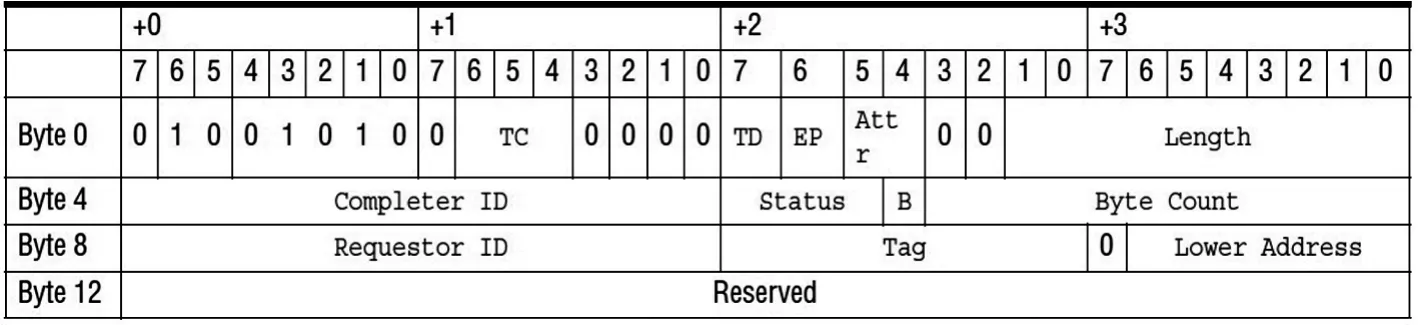

其中,TC字段定义报文的传送类型,TD位表示TLP中的TLP Digest是否有效,EP位表示当前TLP中的数据是否有效,Attr定义报文的模型,Length为报文的有效负载,即需要读取的双字(DW)个数,Requestor ID设备的总线号(Bus Num⁃ber)、设备号(Device Number)和功能号(Function Number)组成,Tag由八位组成,决定了发送端能够暂存256个同类型的TLP,Last BE表示最后一个数据是否有效,First BE表示第一个数据是否有效。应用层需要根据Length及Address,使用完成报文返回相应的数据,完成报文格式如图8[3]。

图8 完成报文

其中,Completer ID也是由设备的总线号、设备号和功能号组成,该字段内容保存在地址为OxF的传输层配置寄存器内,可以通过tl_cfg_ctl总线来读取该值,本文生成的PCI Express硬核得到的Completer ID是0X0200。Status字段保存当前完成报文的完成状态。Byte Count字段记录源设备还需要从目标设备中,获得多少字节的数据就能完成全部数据传递,当前TLP中的有效负载也被Byte Count字段统计在内。Low Address字段存放在存储器读完成TLP中第一个数据所对应地址的最低位,对应内存读报文中Address[6:0]。Byte12开始,填入内存数据。

图9 PCI Express硬核发送数据

图10 PCI Express硬核接收数据

5 PCI Express通信调试及结果

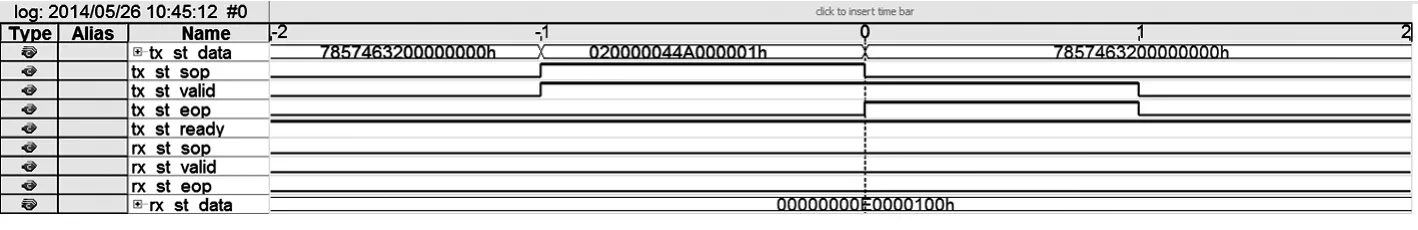

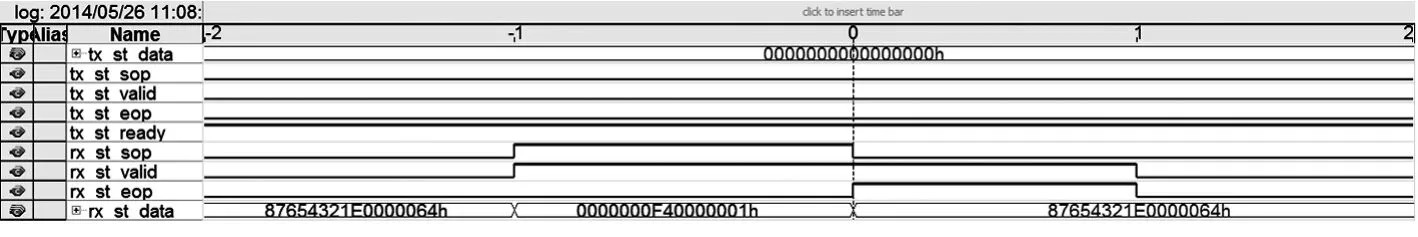

完成代码设计,编译之后,把应用程序加载到FPGA配置芯片,把卡插入电脑PCI Express插槽,开机后,打开Driver Wizard调试软件,可以看到有个Altera-device的PCI设备,双击BARO,进入BAR0读写操作框。根据数据流程模块,DSP向FPGA发送FIFO写处一个0x78574632的数据后,当FIFO有数据时,使用Driver Wizard读该地址数据,进而触发数据发送模块,使用Quartus II自带的SignalTap II Logic Analyzer可以看到发送的时序,如图9所示。Driver Wizard信息框内提示读到的数据。

在Driver Wizard读写框内,向地址0X64写数据0x87654321。在FPGA端 , SignalTap II Logic Analyzer显示接收到数据0x87654321,如图10所示。

6 结论

采用PCI Express方式实现PC机与DSP之间的通信,具有较快的通信速率,完全满足实时通信要求。采用PCI Express硬核,能够缩短开发周期,提高了产品的可靠性和稳定性。

[1]IP Compiler for PCI Express User Guide[EB/OL].www. altera.com.cn.

[2]马鸣锦,朱剑冰,何红旗,等.PCI、PCI-X和PCI Ex⁃press的原理及体系结构[M].北京:清华大学出版社,2007.

[3]杨子元,包启亮,王旭,等.基于PCIE/104总线的高速数据接口设计[J].现代电子技术,2011,34(14):75-78.

Implementation of PCI Express Based on FPGA Hardcore

HE Chun-mao

(Guangzhou Ruida measurement and Control Technology Co.,Ltd,Guangzhou510385,China)

Because the PCI Express fast,stable performance,it is widely used in computer and peripheral equipment communication. According to the motion controller PC platform,using Altera's EP4CGX30 hardcore,realized communication between PC and DSP,through the FPGA internal RAM,adopt FIFO mode,implemented full duplex communication,to meet the requirements of communication between DSP and PC.

FPGA;PCI Express;hardcore

TP393

:A

:1009-9492(2014)10-0081-04

10.3969/j.issn.1009-9492.2014.10.022

何春茂,男,1980年生,江西石城人,硕士。研究领域:工业自动控制及检测。己发表论文2篇。

(编辑:向 飞)

2014-04-29