磁控溅射成膜温度对纯铝薄膜小丘生长以及薄膜晶体管阵列工艺良率的影响

2014-02-02刘晓伟郭会斌李梁梁郭总杰郝昭慧

刘晓伟,郭会斌,李梁梁,郭总杰,郝昭慧

(北京京东方显示技术有限公司,北京 130012)

1 引 言

薄膜晶体管-液晶显示器(TFT-LCD)已经实现全面商业化生产,并在性能上不断提高,大尺寸、高刷新率、高分辨率逐渐成为未来的主要发展方向。为了应对上述发展需求,作为TFT配线使用的低电阻率材料的研究迫在眉睫。纯铝和纯铜材料是近年来研究的重点,并逐渐在量产中得到应用[1-2]。纯铝以其低电阻率(3.3 μΩ·cm)、低成本、易刻蚀等优势逐渐成为TFT配线的主要材料。但铝热膨胀系数较大,在受热的情况下很容易产生小丘,从而刺穿TFT的绝缘层,对产品的可靠性产生严重影响[1]。因此,在量产中,降低小丘发生率是提高产品良率的重要课题。

小丘形成的主要原因是:TFT阵列基板在生产过程中受热,由于金属薄膜和玻璃基板的热膨胀系数不匹配,使得金属薄膜的内应力增大,在应力的驱动下,原子迁移并形成小丘。小丘的形成微观机理目前还有较多争议,主要有3种理论:原子沿着薄膜与基板界面迁移、原子沿着晶界迁移和原子在薄膜表面迁移[3-8]。对如何抑制小丘,研究者也做了大量工作,目前主流的方法是通过在纯铝中添加杂质原子形成固溶体以抑制晶界的原子迁移[9-11],或者在纯铝表面覆盖更硬的薄膜以抑制小丘的生长[12-15],但是对纯铝本身性质和成膜条件对小丘的影响的研究目前还较少。

本文中,我们通过在不同温度下溅射沉积获得了晶粒尺寸不同的纯铝薄膜,并通过电学、扫描电子显微镜(SEM)、应力测试对小丘的形成情况进行了分析,尝试从纯铝薄膜本身沉积工艺的调整上抑制小丘的生长。

2 实 验

2.1 样品制备

本文采用静止垂直成膜的交流磁控溅射设备,使用纯度为99.999%的纯铝和纯度为99.95%纯钼靶材,本底真空为1.3×10-5Pa,通入气体纯度为99.99%的氩气。

分别在100 ℃和120 ℃下在直径为150 mm、厚度为0.65 mm的单晶硅片上沉积350 nm的纯铝薄膜,在350℃、空气氛围中退火20 min,用SEM观察小丘发生情况以及纯铝薄膜的晶粒度。

分别在100 ℃和120 ℃下在直径为150 mm、厚度为0.65 mm的单晶硅片上沉积Mo/Al/Mo 15 nm/350 nm/80 nm三层结构的薄膜,用应力测试仪表征了2种薄膜热应变的屈服强度和温度。

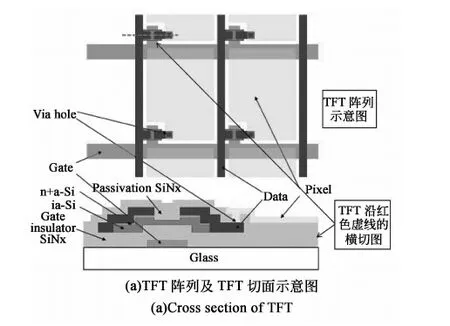

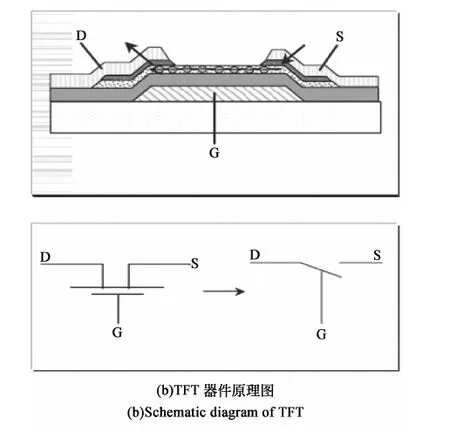

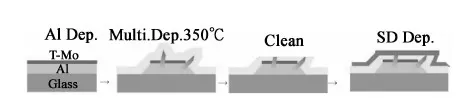

为了验证在硅片上的测试结果,以及小丘对TFT器件量产的影响。 分别在80、100和120 ℃下,在2 200 mm×2 500 mm×0.7 mm、10 000 lx的无碱玻璃基板上用同一台溅射设备沉积了Mo/Al/Mo 15 nm/350 nm/80 nm的薄膜作为TFT Gate层,用高温CVD工艺(350 ℃)沉积绝缘层和半导体层,完成TFT(如图1)整个工艺,制作成TFT阵列。高温CVD工艺起到退火的作用,可以使Gate层Al产生小丘,小丘会造成绝缘层被刺穿,导致Gate层和SD层短路,形成的电学不良(如图2)。通过特定的电学检测设备,可以直观的看出小丘造成的TFT电学不良的比例。采用Mo/Al/Mo三层结构是为了一定程度抑制小丘[12-15],因为如果采用纯铝做电极,小丘太严重会导致不同条件的结果没有对比性。

图1 TFT器件示意图Fig.1 Diagram of TFT

图2 小丘造成的TFT短路原理示意图Fig.2 DGS schematic diagram of TFT caused by hillock

3 结果与讨论

3.1 不同成膜温度下纯铝薄膜小丘发生情况

图3 不同温度下沉积的纯铝薄膜的小丘发生情况Fig.3 Hillock formation in pure Al film at different deposition temperature

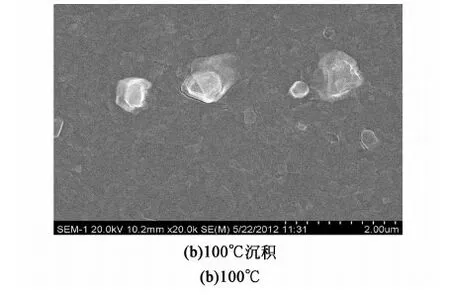

为了直观地确认不同温度下沉积的纯铝薄膜小丘的发生情况,分别在100 ℃和120 ℃下在硅片上沉积350 nm的纯铝薄膜,在350 ℃、空气氛围中退火20 min,用SEM观察小丘发生情况,如图3。

从图3中可以明显看出在100 ℃下沉积的纯铝薄膜产生的小丘不论是密度还是体积都明显大于120 ℃下沉积的纯铝薄膜。在基片的不同位置取样进行比较,结果均如此。

3.2 不同成膜温度下纯铝薄膜晶粒尺寸的差异

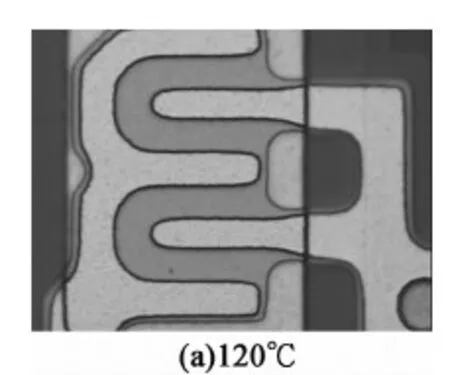

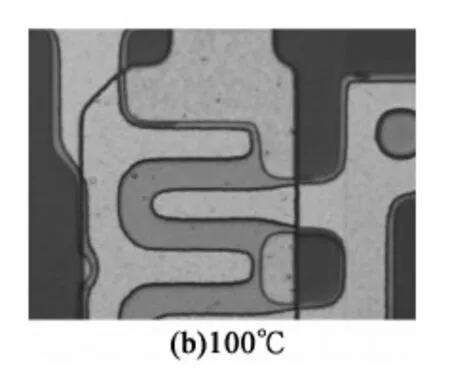

为了进一步确认高温成膜对小丘影响的原因,我们准备了两片分别在100 ℃和120 ℃下沉积的纯铝薄膜(350 nm)未退火的样品,用稀盐酸浸润10 s之后用SEM观察晶粒尺寸,如图4。

图4 不同温度沉积的纯铝薄膜的晶粒尺寸Fig.4 Grain size of pure Al film deposited at different temperature

从SEM照片上看,可以明显看出120 ℃下沉积的纯铝薄膜的晶粒尺寸明显大于100 ℃下沉积的薄膜的晶粒尺寸。小丘是在内应力驱动下原子的扩散行为,晶粒尺寸较小,晶界较多,小丘容易在晶界间生长[3]。因此高温成膜晶粒尺寸较大,晶界较少,有助于抑制小丘的发生。

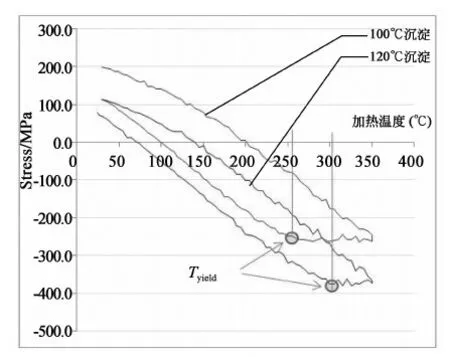

3.3 不同温度下沉积的纯铝薄膜的应力-温度变化

图5是不同温度下沉积的Mo/Al/Mo 15 nm/300 nm/80 nm的热应变的应力-温度曲线,纵坐标是应力,横坐标表示加热的温度。薄膜沉积在Ф 150 mm×0.6 mm的单抛光硅片上。应力通过东朋公司的FLX-2320-S型应力测试仪测出。

图5 不同温度下沉积的Mo/Al/Mo 15/300/80 nm的应力-温度曲线Fig.5 Stresses v.s. temperature curve of Mo/Al/Mo 15 nm/300 nm/80 nm

超过屈服温度后,薄膜倾向于塑性形变,开始形成小丘[13]。从应力测试结果可以看出,高温沉积的薄膜应力屈服点温度较高,因此,小丘的发生会更难,这也与前面的实验结果吻合,高温沉积有助于抑制小丘的发生。

3.4 不同成膜温度下完成的面板电学检测结果

在2 200 mm×2 500 mm×0.7 mm、10 000 lx的无碱玻璃上在不同的温度下沉积Gate层Mo/Al/Mo 15 nm/350 nm/80 nm,按32 in(1 in=2.54 cm)的mask进行曝光,每张基板可以做出独立的18个TFT阵列单元,对每个阵列单元分别进行电学检测,结果如表1所示。

其中DGS表示Gate层与交叠处的Date线发生短路,DDS表示Date线与Date线短路,一般是因为相邻的DGS造成,DCS是指Date线与Common线的短路,common线与Gate线属于同一层沉积的金属,因此DCS可以认为与DGS相同。DGS/DDS/DCS主要是由于小丘造成(如图2)。

表1不同温度下沉积的Gate层完成TFT阵列工艺后电学检测结果

Tab.1 TFT Array which gate layer was deposited at different temperature electrical test yield

Gate层纯铝溅射温度单元数量36DGSDDSDCS失效的单元数21104780℃不良数量241347成品率/%417278111194失效的单元数2011100℃不良数量2011成品率/%944002828失效的单元数0000120℃不良数量0000成品率%100000

从表1中可以看出,120 ℃下沉积Gate层的样品基本没有相关不良,样品的成品率达到100%。而在80 ℃下,阵列单元的良率最低,主要的不良为Gate线与Date线交叠处的小丘引起的短路,小丘容易刺破绝缘层导致Gate和SD层金属短接如图2。从光学显微镜上看,80 ℃沉积的样品,Gate线上小丘密度较大,而在120 ℃下沉积的样品Gate线上小丘的密度则很小(如图3)。

图6 不同温度下沉积的Gate层,完成TFT工艺后小丘发生情况Fig.6 Hillock formation in TFT gate layer deposited at different temperature

4 结 论

不同沉积温度下沉积的纯铝薄膜小丘发生情况有明显差异,高温沉积下的纯铝薄膜由于有较大的晶粒尺寸,可以减少薄膜内部晶界,因此可以减少应力释放导致的纯铝原子的在晶界的迁移,因此,小丘发生的尺寸和密度都较小。热应变的屈服温度也较高。在TFT-LCD中阵列工艺的量产中适当提高纯铝薄膜的成膜温度,对小丘的抑制效果较为明显。

[1] 王大海,杨柏梁,吴渊,等. TFT阵列金属电极的制备与性能[J].液晶与显示,2000,15(4):260-267.

Wang D H,Yang B L,Wu Y,etal. Preparation and characterization of metal films in TFT array [J].ChineseJournalofLiquidCrystalsandDisplays,2000,15(4):260-267. (in Chinese)

[2] 刘翔,陈旭,谢振宇,等. 使用低电阻金属铝制造薄膜晶体管阵列信号电极[J].液晶与显示,2009,24(4):533-536.

Liu X,Chen X,Xie Z Y,etal. Low resistant metal for thin film transistors [J].ChineseJournalofLiquidCrystalsandDisplays,2009,24(4):533-536. (in Chinese)

[3] Kwang-Ho J,Soo-Jung H,Young-Chang J. Effect of capping layer on hillock formation in thin Al films [J].MetalsandMaterialsInternational,2008,14(2):147-150.

[4] 王刚,刘宏宇,赵超,等. 表面无小丘Al双层栅电极结构研究[J].液晶与显示,2000,15(2):92-100.

Wang G,Liu H Y,Zhao C,etal. Study on hillock-free al gate materials with double layer structure [J].ChineseJournalofLiquidCrystalsandDisplays, 2000,15(2):92-100 . (in Chinese)

[5] Chaudhari P,Scott B A,Laibowitz R B,etal. Simulation of structural anisotropy and void formation in amorphous thin films [J].ApplPhys,1974,25(11):641-643.

[6] Iwamura E,Ohnishi T,Yoshikawa K. A study of hillock formation on AlTa alloy films for interconnections of TFT-LCDs [J].ThinSolidFilms,1995,270(1-2):450-455.

[7] Ericson F,Kristensen N,Schweitz J A. A transmission electron microscopy study of hillocks in thin aluminum films[J].MicroelectronicsandNanometerStructures,1991,9(1):58-63.

[8] Chang C Y,Vook R W. Thermally induced hillock formation in Al-Cu films [J].JournalofMaterialsResearch,1989,4(5):1172-1181.

[9] Arai T,Makita A,Hiromasu Y,etal. Mo-capped Al-Nd alloy for both gate and data bus lines of liquid crystal displays [J].ThinSolidFilms,2001,383(1-2):287-291.

[10] Kim D K,Nix W D,Vinci R P,etal. Study of the effect of grain boundary migration on hillock formation in Al thin films [J].JournalofAppliedPhysics,2001,90(2):781-788.

[11] Onishi T,Iwamura E,Takagi K,etal. Influence of adding transition metal elements to an aluminum target on electrical resistivity and hillock resistance in sputter-deposited aluminum alloy thin film[J].Vac.Sci.Technol.A,1996,14(5):2728-2735.

[12] Dell′oca C J,Learn A J. Anodization of aluminum to inhibit hillock growth during high temperature processing [J].ThinSolidFilms,1971,8(5):R47-R50.

[13] Chang C Y,Vook R W. The effect of surface aluminum oxide films on thermally induced hillock formation [J].ThinSolidFilms,1993,228(1-2):205-209.

[14] Takatsuji H,Haruta K,Tsuji S,etal. Pure Al thin film protective layer to prevent stress migration in Al wiring for thin-film transistors [J].SurfaceandCoatingsTechnology,2000,125(1-3):167-172.

[15] Iwamura E,Takgi K,Ohnishi T. Effect of aluminium oxide caps on hillock formation in aluminium alloy films [J].ThinSolidFilms,1999,349(1-2):191-198.

[16] Soo-Jung H,William D N,Young-Chang J. A model for hillock growth in Al thin films controlled by plastic deformation [J].ActaMaterialia,2007,55(15):5297-5301.