电缆连通性快速检测系统设计

2014-01-21李金洪

李金洪

(昆明船舶设备研究试验中心 云南 昆明650051)

水下航行体各个组件的连接主要通过电缆来实现。水下航行体由许多不同的功能组件构成,组件类型众多[1-3],连接组件的电缆数量多,类型杂。据某型产品的电缆需求统计,一个产品的电缆种类就多达30多种,芯数上万颗。在生产中对水下航行体电缆连通性检测是一个非常困难的问题。传统办法是采用人工逐芯测量的办法,效率低,且容易出错。

目前市场中针对电缆检测的产品能检测的电缆芯数都比较小,而且主要是国外公司的产品居多,国内研究较少。对芯数众多的电缆的通断性检测设备研究设计,具有较大应用范围和前景[4]。本文设计的电缆通断性检测设备可以对电缆芯数不大于256的电缆进行连通性检测和识别。

1 电缆连通性检测原理

水下航行体连接各个功能组件的电缆长度一般都不大于2 m,电缆的电阻值小于10 Ω。当电缆芯数大于15芯时,用人工测试方法容易导致错误。本设计主要针对芯数大于20芯以上,电缆长度小于3 m、电缆自身电阻小于50 Ω的电缆的通断性检测。

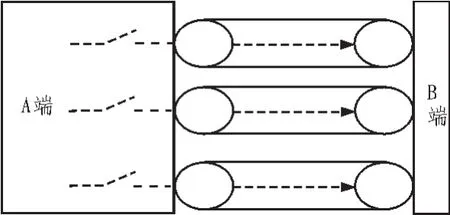

对于短距离小电阻的电缆通断性检测,可以通过在一端加一个电压信号,然后在另一端进行状态采集的方法实现。如图1所示,假设在电缆A端加5 V的TTL信号,就可以通过检测B端的状态信号判断电缆的通断性。

图1 电缆连通性检测原理图Fig.1 The schematic of Cable connectivity detection

图1 中电缆芯之间的扫描切换通过CPLD实现,用数字开关的方法代替继电器,增加扫描速度。在实际应用中,电缆一端与另一端连接关系复杂。在A端加数字电平信号,同时在B端进行状态采样,A端扫描信号变化后,重复采集B端的状态。扫描结束后,对采集存储的状态信息进行分析处理,通过综合逻辑判断的方法实现电缆连通性的检测。

当电缆芯数较多时,为了提高对B端状态信息的处理速度,对电缆芯数进行分组,按16芯一组进行采集存储。

2 连通性检测电路设计

某型水下航行的电缆种类繁多,大部分电缆芯数都大于20,最多的达到256芯。对芯数如此多的电缆进行电信号扫描,对检测电路提出较高的要求。

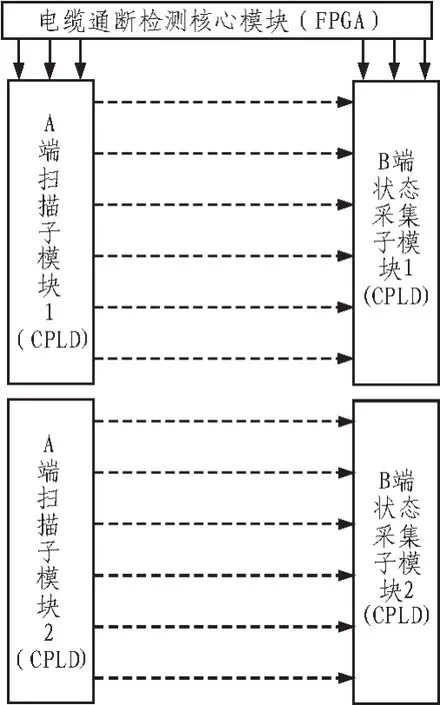

通过对电缆的特性进行分析,选择模块化的设计方法来实现电缆的通断检测功能。对256芯进行分组,每组128芯,用两个子模块来实现扫描任务。在电缆的另一端进行状态采集也使用模块化设计,按分级的方法每个模块采样128芯的状态,用两个子模块完成电缆状态采集。

为了对各个子模块进行协调控制,并对检测结果进行逻辑判断,设计了基于FPGA的核心处理模块,它主要负责与外部设备进行通信,控制电缆的电信号扫描方法,同时对电缆另一端的采样信息进行收集存储,进行信息处理。电路模块结构如图2所示。

图2 电缆通断性检测电路模块结构图Fig.2 Diagram of cable connectivity detection module

核心模块用FPGA来实现,它提供与上位机的通信接口,对上位机定制的电缆扫描任务进行分配调度,然后把扫描控制信号传送给电路扫描子模块1和2去执行,同时核心模块对电缆另一端的状态进行采集回收,实时存储采集状态,为电缆的通断逻辑判断提供信息。

电缆检测核心模块FPGA的电路设计用verilog硬件编程语言实现,其设计方法灵活方便[5]。通过FPGA核心的功能分析设计相应的功能块,实现结构如图3所示。

图3 FPGA核心模块结构Fig.3 FPGA core module structure

电缆扫描模块根据核心模块给出的扫描任务提供相应的扫描信号。针对电缆芯数多达256芯的情况,扫描模块选用CPLD来设计扫描电路。在设计中选择Xilinx公司的CoolRunner系列XCR3256实现,它具有速度快,功耗低的特点[6]。采用CPLD设计扫描信号,通道切换用数字通道代替传统的继电器矩阵开关,提高了通道切换速度,而且缩小了电路的体积。图4为16芯电缆的实现原理图,芯数增加通过CPLD扩展即可实现。

图4 电缆扫描电路结构图Fig.4 Diagram of the cable scanning circuit

在扫描电路中,为了方便电缆芯数扫描范围扩展,按16芯为最小扫描单元实现,最小扫描单元都设计了扩展控制信号CE,通过控制信号CE进行级联扩展,并接收FPGA核心模块给出的其它控制信号,实现扫描256芯的目标。

在电缆A端加上扫描信号后,要实时采集电缆另一端的状态,通过对状态数据分析来判断电缆的通断性。在实际应用中,对电缆的通断性检测只是其中一个应用方面,有的时候需要对电缆两端的连接对应关系进行了解,要求电缆通断检测设备对电缆的每一根芯进行地址编码,以方便识别连接关系。

电缆终端状态采集电路设计也采用CPLD来实现。终端状态采集电路主要由状态采集存储电路、状态数据传输电路、电缆终端状态输入信号处理电路构成。对256芯电缆的终端状态进行采集,利用256个数字通道实现,同时对相应的通道进行地址编码,方便电路识别电缆连接关系。根据电缆通断检测的电路系统设计,电缆终端采集电路模块采集的状态信息需要传递给核心电路处理模块。为了降低硬件布线困难,状态数据传输电路采用SPI总线模块,它只需要4根信号线即可完成两个模块之间的数据传输功能。由于状态采集电路只需要进行单向传输数据,只需要SPI总线的SCLK和MOSI两根线即可。电缆终端状态采集电路模块电路结构如图5所示。

图5 电缆终端状态采集电路结构Fig.5 Circuit structure of cable terminal state acquisition

3 电缆通断性检测软件设计

在软件设计中,由于电缆类型众多,对电缆通断检测功能,主要目标是验证产品的通断性,电缆的连接关系有相应的技术要求保证,根据技术要求设计相应的扫描任务数据库就实现。扫描任务定制比较简单,只对有连接功能的芯进行扫描验证就可以,简化了扫描任务,节省了扫描时间。

在水下航行体测试过程中,如果航行体产品来自多家设计单位,电缆的连接关系由设计单位事先处理好,一般不会提供电缆连接对应关系详细信息。出现故障后,如果没有设计单位提供的图纸或是详细技术资料,对电缆的故障排查变得非常困难。设计电缆连接对应关系识别软件,可以在没有电缆连接设计图纸的情况下判断电缆的故障问题。电缆连接识别软件首先对完好产品的电缆进行连接关系扫描,并把连接对应关系构建为标准数据库,为故障电缆检测提供检测标准。

在电缆通断性检测软件设计过程中,对电缆的连通性质量检测和电缆连接关系识别都需要对电缆进行扫描任务定制,它们的大部分功能程序要求相同,通过上位机设定工作模式,然后进行具体的功能设计即可。软件流程图如图6所示。

图6 电缆通断性检测软件流程图Fig.6 Software flow chart of cable connectivity detection

4 设计验证

电缆通断性检测电路设计目标是对电缆芯数不大于256芯的电缆进行通断性快速检测,对电缆的连接关系进行识别。通过前面的电路设计分析,进行相应的软件仿真和硬件测试。软件仿真主要利用ModelSim测试FPGA和CPLD数字电路设计原理的正确性。为了方便测试,按16芯的情况进行仿真测试,结果如图7所示按,它完成了扫描信号的发送,同时对电缆终端的状态进行采集传输。

图7 电缆通断检测电路硬件仿真图Fig.7 Hardware emulation of Cable connectivity detection

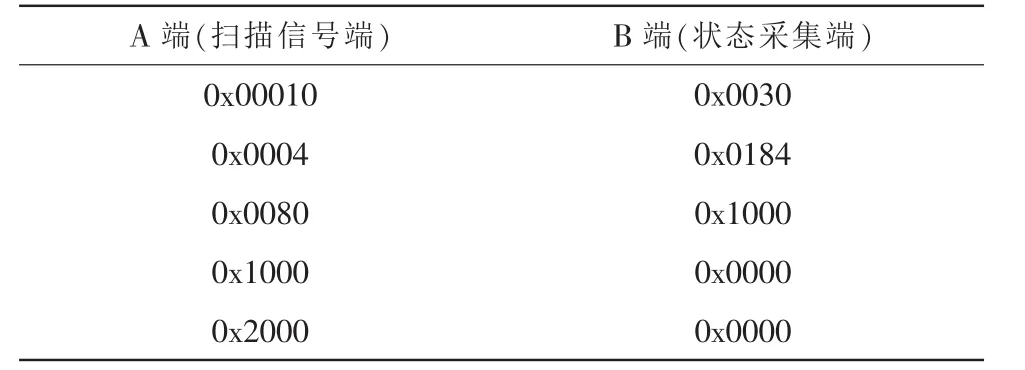

通过软件仿真测试验证了设计原理的正确性。按16芯电缆情况利用Xilinx公司的FPGA平台xs1200e进行硬件级电缆通断性检测测试,测试结果见表1。测试条件如下:

表1 电缆连通性检测数据表Tab.1 Test data of the cable connectivity detection

1)被测试电缆A的两端芯数连接对应关系为a1对b5、b7;a3 对 b3、b8、b9;a8 对 b13;其余芯为空。

2)扫描信号加载端设为A端,加载于每根芯的信号用0或是1表示。0表示没有加载信号,1表示加载信号。电缆状态采集终端为B端。0表示无连接,1表示有连接。表中为了表示16根芯状态,用长度为一个字的16进制数据表示。

从表1可知,在A端加信号0x0001,对应为a1芯加载扫描信号,在B端采集信号为0x0030,对应连接的芯为b5和b7芯,与实际连接关系符合,其它芯同理可知,结果与实际电缆连接关系一致,电路设计正确。

5 结论

结合水下航行体连接电缆的特性对电缆连通性检测原理进行研究,设计电缆通断性检测电路,经验证方法可行,为工程设计提供了设计依据。

水下航行体的电缆种类繁多,在生产中对其进行通断性检测占用太多的时间和人力,效率低下。电缆通断检测系统可以自动检测电缆通断性,满足芯数不大于256芯的电缆通断性检测。在实际操作中,电缆的连接关系比较复杂,需要进一步优化电缆检测快速扫描方法,提高系统的适用性。

[1]赵连恩.高性能船舶水动力原理与设计[M].哈尔滨:哈尔滨工程大学出版社,2007.

[2]徐德民.鱼雷自动控制系统[M].2版.西安:西北工业大学出版社,2001.

[3]尹韶平,刘瑞生.鱼雷总体技术[M].北京:国防工业出版社,2011.

[4]孙启飞.电缆检测技术的应用与提高[J].低压电器,2010(1):49-53.SUN Qi-fei.Application and improvement of cable inspection technology[J].Low Voltage Apparatus,2010(1):49-53.

[5]萨米尔·帕尔尼卡 (Samir Palnitkar),Verilog HDL数字设计与综合[M].2版.夏宇闻译,北京:电子工业出版社,2013.

[6]王杰,王诚,谢龙汉.Xilinx FPGA/CPLD设计手册[M].北京:人民邮电出版社,2011.