通用信号处理模块功能线程动态重构技术

2014-01-01刘可

刘 可

(中国西南电子技术研究所,四川成都610036)

0 引言

IMA是当前航电体系结构发展的最高阶段[1],其体系架构实现了基于模块的高度综合,硬件资源与软件资源均采用模块化设计,系统通过对软硬件资源进行配置及重构来实现各项功能线程[2]。在IMA系统中,通用SPM通过加载不同的应用程序和配置参数来实现不同的数字信号处理功能[3],其设计难点在于如何实现稳定可靠的功能线程动态重构和应用程序在线更新。目前国内航空电子领域已知范围内尚缺乏相关专门研究和工程实践。本文介绍了一种机载通用SPM功能重构和代码更新技术。通用SPM以大规模可编程逻辑器件(FPGA)和高速数字信号处理器(DSP)为主处理单元,引入应用程序3级加载流程,可按照系统指令动态配置主处理单元,可实现数10种数字信号处理功能程序的存储和加载。

1 通用SPM硬件设计

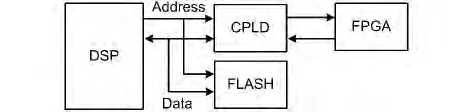

通用SPM每个处理通道配备高速LVDS串行解串器(SERDES)[4]、FPGA、DSP 和通用异步收发器(UART)[5],此外还有大容量 FLASH 存储器、SDRAM存储器、用户自定义接口以及模块支持单元。模块支持单元可由CPLD或小容量FPGA编程实现。通用SPM单处理通道如图1所示。

FPGA和 DSP是通用 SPM的主处理单元[6]。其中,DSP除了是数字信号处理的核心器件,还是功能线程动态重构和应用程序在线更新的主控器。DSP挂接的FLASH存储器用于保存各种数字信号处理功能的DSP和FPGA应用程序代码,此外还存储功能重构和代码更新所需的自举加载程序(BOOTLOADER)[7]以及功能管理程序。模块支持单元主要负责在功能重构过程中实现FPGA加载接口和加载过程监控。SDRAM存储器为功能管理程序和应用程序提供了数据暂存空间。

图1 通用SPM单处理通道

2 功能重构和代码更新解决方案

基于自身具备的自举加载(BOOTLOAD)[8]能力,DSP成为功能线程动态重构和应用程序在线更新的主控器。为了突破DSP自举加载程序代码尺寸不能超过1 KB的限制以满足系统需求,通用SPM采用了应用程序3级加载流程。

2.1 DSP 应用程序加载流程

通用SPM DSP应用程序加载流程分为3个阶段:自举加载程序加载运行、功能管理程序加载运行和应用程序加载运行,即3级加载。

通用SPM FLASH存储器挂接在DSP芯片EMIFB总线CE1空间,DSP通过上拉/下拉电阻配置成从EMIFB总线CE1空间的8 bit ROM上电/复位自举加载。FLASH低地址段保存BOOTLOADER程序,BOOTLOADER用汇编语言编写,编译后大小不超过1 KB。DSP上电/复位后,CPU处于“挂起”状态,增强型直接存储器访问(EDMA)控制器使用默认的ROM访问时序,以单帧数据块传输方式自动把FLASH中前1 KB地址单元中存储的BOOTLOADER代码拷贝到片内程序存储区,在此过程中EMIF接口自动把连续的8 bit字节组合成32 bit指令字以便EDMA控制器复制。数据块传输结束后,CPU从“挂起”状态中被释放并从内存地址0开始执行 BOOTLOADER代码,该阶段为第1级加载[9]。

受限于代码尺寸,BOOTLOADER的主要任务是把FLASH中保存的功能管理程序代码整块搬移到DSP片内程序存储区,然后跳转到功能管理程序起始处执行,该阶段为第2级加载,功能管理程序可视为第2级BOOTLOADER。

应用程序的加载由功能管理程序完成。功能管理程序根据模块支持单元CPLD中保存的加载参数信息,从FLASH中特定存储空间读取数字信号处理应用程序代码并写入DSP内存,校验正确后跳转执行,该阶段为第3级加载。至此,DSP应用程序加载流程结束。

2.2 FPGA应用程序加载流程

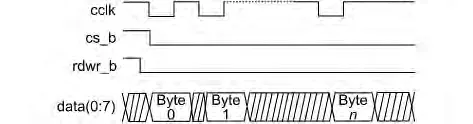

和DSP应用程序一样,FPGA应用程序也保存在FLASH存储器中。FPGA配置模式通过硬件设定为从并模式(Slave SelectMAP)[10],由 DSP 充当FPGA加载的主控器。DSP在自身加载流程的第2阶段运行功能管理程序对FPGA进行配置。一般情况下可将FPGA视为DSP的外设,因此功能管理程序先配置FPGA,再加载DSP。功能管理程序通过DSP EMIF总线从FLASH中读出FPGA应用程序代码,然后通过模块支持单元CPLD写入FPGA加载端口。CPLD实现DSP EMIF总线至FPGA加载端口之间的接口适配逻辑[11],FPGA加载如图2所示。

图2 FPGA加载

通过CPLD实现的FPGA加载时序如图3所示。

图3 FPGA加载时序

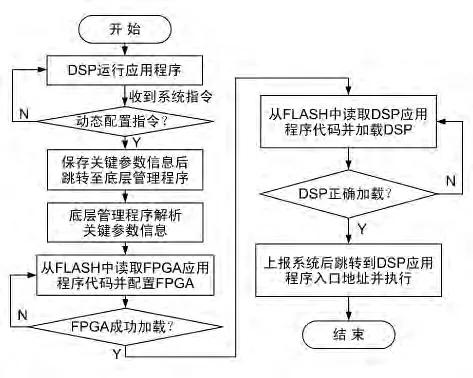

2.3 功能线程动态重构流程

系统在需要对通用信号处理模块进行功能重构时,首先通过UART接口向DSP发送功能重构指令。DSP当前运行的应用程序接收到该指令后,将指令中包含的关键参数信息保存在模块支持单元中,然后通过模块支持单元发出DSP复位信号,启动DSP加载流程。DSP依次运行BOOTLOADER和功能管理程序。功能管理程序根据模块支持单元中保存的功能重构参数,从FLASH存储器中对应地址空间读取用户程序FPGA和DSP代码。用户程序FPGA代码通过CPLD中的适配逻辑写入FPGA配置口。FPGA在数据加载正确完成后自动启动配置流程。此后,功能管理程序将用户程序DSP代码直接写入DSP内存,校验正确后跳转执行。在跳转执行DSP应用程序前,功能管理程序通过UART接口将功能线程动态重构操作结果上报系统。功能重构流程如图4所示。

图4 功能重构流程

2.4 应用程序在线更新流程

应用程序在线更新流程如图5所示。

图5 应用程序代码更新流程

通用SPM在功能重构流程中读取的DSP和FPGA应用程序代码全部存放在大容量FLASH存储器中。模块单板调试时,DSP可挂接仿真器,在PC机CCStudio开发环境中将保存在本地硬盘上的DSP和FPGA应用程序代码烧录到FLASH内。在系统联试和维护的情况下,系统主控可通过UART接口向通用信号处理模块DSP发送应用程序代码更新指令。DSP当前运行的应用程序接收到该指令后,将指令中包含的关键参数信息保存在模块支持单元中,然后通过模块支持单元发出DSP复位信号,启动 DSP加载流程。DSP依次运行 BOOTLOADER和功能管理程序。功能管理程序解析模块支持单元中保存的指令参数,并通过UART接口接收系统下发的DSP和FPGA应用程序代码数据。应用程序代码以数据帧的形式分包传送,每一帧数据内含该包数据的CRC校验值。通用SPM将接收到的应用程序代码数据暂存在SDRAM存储器中。校验无误后,功能管理程序再将应用程序代码烧写到FLASH相应地址空间中并将操作结果上报系统主控。

2.5 功能重构常见问题

通用SPM功能重构有2个常见问题:加载耗时和加载可靠性。

加载耗时受以下因素制约:被加载代码长度、DSP内核时钟速率和EMIF接口工作速度、FLASH存储器访问位宽以及FPGA配置时钟速率和配置接口位宽。因此,提高加载速度的可行办法有:提高DSP内核和EMIF接口运行速度;在功能管理程序开始运行后把FLASH访问位宽从字节(8 bit)改为字(16 bit);将FPGA配置位宽增大到32 bit并提高配置时钟速率。

加载可靠性可分为硬件可靠性和操作完备性2个问题。硬件可靠性是指模块长时间工作以及应对极端使用环境的能力,如高低温、振动和复杂电磁环境。硬件可靠性问题的关键是PCB及其完整性设计,不仅包括信号完整性、电源完整性,还包括EMC、防护、热设计、结构和易测试性等内容[12]。而操作完备性主要指在功能动态重构过程中严格遵循相关器件使用要求,做好器件复位、配置和校验等操作,最大限度保证器件正常可靠工作。

3 结束语

介绍了一种机载通用SPM功能线程动态重构和应用程序在线更新技术。该技术采用了特有的应用程序3级加载流程以实现系统要求,目前已在一系列工程项目和产品中获得了成功应用。需要特别指出的是,在DSP支持自举加载功能的前提下,通用SPM主处理单元可根据应用需求灵活选用TI公司的TMS320C64XX和 TMS320C64X+系列各型DSP和XILINX公司的Virtex和Spartan系列各型FPGA。此外,通用SPM与系统主控的通信接口可以换用网络接口单元,如TMS320C6455等DSP芯片具备的4路1X RapidIO串行接口或1路4X RapidIO并行接口[13]。通过网络接口单元,通用SPM可加入系统内部互联网络,为系统硬件体系架构的开放性和可扩展性奠定基础。

[1] 张凤鸣,褚文奎,樊晓光,等.综合模块化航空电子体系结构研究[J].电光与控制,2009,16(9):47-51.

[2] 茅 成.综合通信导航识别系统中的多链路超短波通信的实现[J].电讯技术,2009,49(8):59 -64.

[3] 陈 颖,苑仁亮,曾 利.航空电子模块化综合系统集成技术[M].北京:国防工业出版社,2013(9):1-2.

[4] National Semiconductor. DS92LV16 Datasheet[S],2013.

[5] PHILIPS.SC16C554B/554DB.Datasheet[S],2014.

[6] 齐青茂,王岩建,张华冲.中频采样全数字接收机的设计与实现[J].无线电通信技术,2012,38(4):77 -80.

[7] Texas Instruments.Creating a Second-level Bootloader for FLASH Bootloading on TMS320C6000 Platform With Code Composer Studio[S],2006.

[8] Texas Instruments.TMS320C6414T/15T/16T Datasheet[S],2011.

[9] Texas Instruments.TMS320C6000 EMIF to External Flash Memory[S],2002.

[10]余金磊,孙明杰.基于NIOSⅡ的FPGA配置技术[J].无线电通信技术,2013,39(3):73 -75.

[11] XILINX.Virtex-4 Configuration Guide[S],2011.

[12]王剑宇,苏 颖.高速电路设计实践[M].北京:电子工业出版社,2010.

[13] Texas Instruments. TMS320C6455 Fixed-Point Digital Signal Processor Datasheet[S],2011.